го

сд

Јъ

ОЭ СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки микроЭВМ | 1986 |

|

SU1432531A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

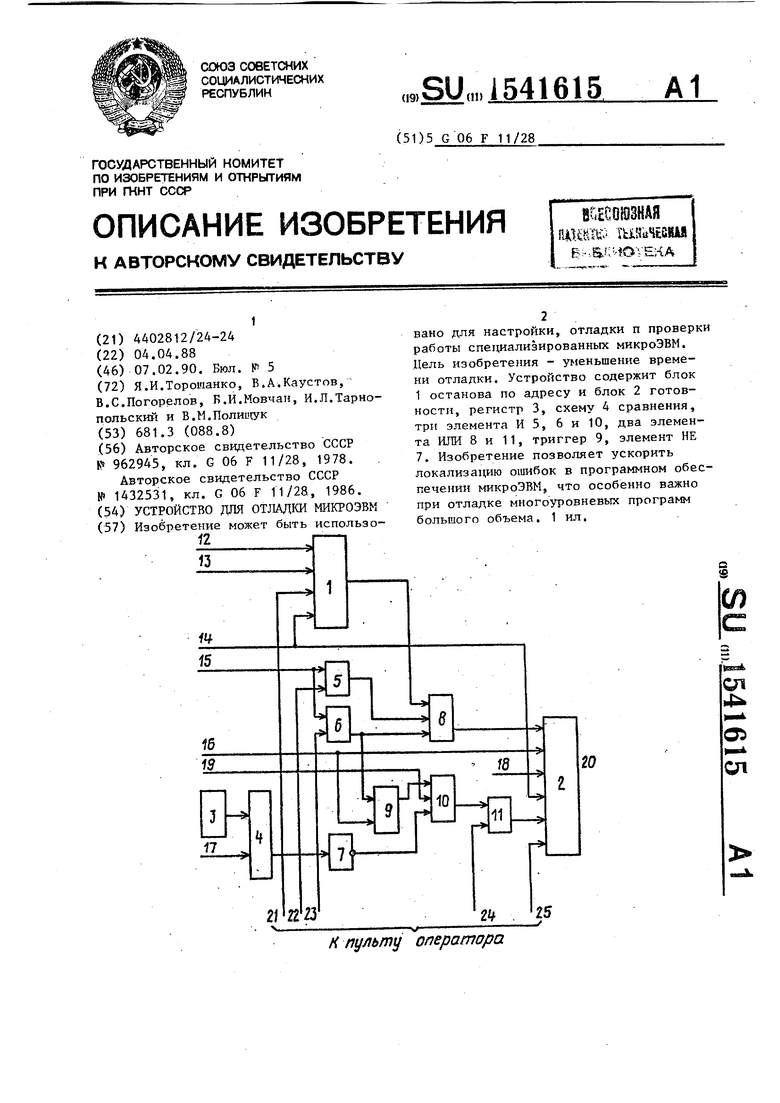

Изобретение может быть использовано для настройки, отладки и проверки работы специализированных микроЭВМ. Цель изобретения - уменьшение времени отладки. Устройство содержит блок 1 останова по адресу и блок 2 готовности, регистр 3, схему 4 сравнения, три элемента И 5, 6 и 10, два элемента ИЛИ 8 и 11, триггер 9, элемент НЕ 7. Изобретение позволяет ускорить локализацию ошибок в программном обеспечении микроЭВМ, что особенно важно при отладке многоуровневых программ большого объема. 1 ил.

К пульту оператора

Изобретение относится к вычислительной технике и может быть использвано для настройки, отладки и проверки работы специализированных микро- ЭВМ.

Цель изобретения - сокращение времени отладки программ.

На чертеже представлена схема устройства для отладки микроЭВМ.

Устройство для отладки микроЭВМ содержит блок 1 останова по адресу, блок 2 готовности, регистр 3, схему 4 сравнения, первый 5 и второй 6 элементы И, элемент НЕ 7, первый элемент ИЛИ 8, триггер 9, третий элемент И 10, второй элемент ИЛИ 11, выходы отлаживаемой микроЭВМ, соответствующие входам устройства: адресный 12, модификации останова по адресу 13, признака начала команды 14, подтверждения прерывания 15, синхронизации 16, вектора прерывания 17, тактовый 18, приема вектора прерывания 19, вход 20 готовности отлаживаемой микроЭВМ, входы от пульта оператора: останова по адресу 21, останова по прерыванию 22, останова по вектору прерывания 23, пуска 24 и задания режима 25.

Устройство для отладки микроЗЙМ обеспечивает следующие аппаратные режимы отладки: останов по адресу или зоне общий, останов по адресу либо зоне адресов при записи в ОЗУ мккрс- ЭВМ, при записи в стек, при записи в область ОЗУ, не являющуюся стеком; останов по адресу либо зоне адресов при чтении памяти, при чтении стека, при чтении области памяти, не являющейся стеком; останов по адресу либо зоне адресов при вводе информации из внешнего устройства, останов по адресу либо зоне адресов при выводе информации во внешнее устройство, останов по адресу либо зоне адресов при чтении кода команды, останов по адресу либо зоне адресов при чтении операндов команды, шаговый режим по- циклового прохождения программы, шаговый режим покомандного прохождения программ, останов по определенному вектору прерывания, останов по прерыванию.

Работа устройства для отладки микроЭВМ в режимах: останова по адресу или зоне обший, останова по адресу либо -зоне адресов при записи в ОЗУ, при записи в стек, при записи в об5

0

5

ласть ОЗУ, не являющуюся стеком; останова по адресу; останова по адресу или зоне адресов при вводе информации из внешнего устройства, останова по адресу либо зоне адресов при выводе информации во внешнее устройство, останова по адресу либо зоне адресов при чтении кода команды,

Q останова по адресу либо зоне адресов при чтении операндов команды, шаговый ре.жим поциклового прохождения программы, шаговый режим покомандного прохождения программы описаны в известном устройстве.

Режим останова по определенному вектору прерывания реализован следующим образом.

В регистр 3 необходимо занести код, соответствующий заданному вектору прерывания. На вход останова по вектору прерывания 23 подать высокий уровень. При появлении сигнала подтверждения прерывания на входе 15 на выходе блока 2 готовности появится низкий уровень, который вызывает останов отлаживаемой микроЭВМ. Одновременно на выходе триггера 9 появится высокий уровень. Если пришедший в последующий момент времени по входу 17 вектора прерывания код совпадает с занесенным в регистр 3, то на выходе схемы 4 сравнения появится высокий уровень, который, пройдя через элемент НЕ 7, приходит низким уровнем на третий вход третьего элемента И 10. В этом случае на выходе второго элемента ИЛИ 11 будет низкий уровень и микроЭВМ останется в режиме останова. Вывести ее из этого режима можно, подав на вход пуска 24 высокий уровень. Если пришедший по входу 17 вектора прерывания код не совпадает с занесенным в регистр 3, то на выходе третьего элемента И 10 появится высокий уровень, который, пройдя через второй элемент ИЛИ 11, вызовет установление высокого уровня на выходе блока 2 готовности, и отлаживаемая микроЭВМ продолжит работу.

Режим останова по признаку прерывания реализуется при высоком уровне на входе 22 останова по прерыванию. При приходе сигнала подтверждения прерывания на вход 15 на выходе пер5 вого элемента И 5 появится высокий уровень, который, пройдя через первый элемент ШГИ 8, вызовет останов отлаживаемой ЭВМ. Гак как на выходе

0

5

0

5

0

51

второго элемента И Ь присутствует низкий уровень, то на выходе триггера 9 будет также низкий уровень, который предотвращает поступление высокого уровня на пятый вход блока 2 готовности и тем самым запрещает работу отлаживаемой мнкроЭВМ. Для того, чтобы отлаживаемая микроЭВМ продолжила работу, необходимо подать на вход 24 пуска высокий уровень.

Формула изобретения

Устройство для отладки микроЭВМ, содержащее блок останова по адресу, блок готовности, причем адресный вход, вход модификации останова по адресу и вход останова по адресу устройства соединены соответственно с первым, вторым к третьим входами блока останова по адресу, вход признака начала команды устройства соединен с четвертым входом блока останова по адресу и с первым входом блока готовности, выход которого является выходом останова устройства, вход синхронизации и тактовый вход устройства соединены соответственно с вторым и третьим входами блока готовности, вход задания режима устройства соединен с четвертым входом блока готовности, отличающееся тем, что, с целью сокращения времени отладки, в устройство введены регистр, схема сравнения, первый, второй и третий элементы И, первый и второй элементы

Q

5

0

$

5

0

156

ИЛИ, триггер и элемент НЕ, причем входы вектора прерывания, останова пп прерыванию, останова по вектору прерывания и приема вектора прерывания устройства соединены соответственно с первым входом схемы сравнения, с первым входом первого элемента И, с первым входом второго элемента И, и с первым входом третьего элемента И, вход подтверждения прерывания устройства соединен с вторыми входами первого и второго элементов И, выходы которых соединены соответственно с первым и вторым входами первого элемента ИЛИ, вход синхронизации устройства соединен с тактовым входом триггера, выход которого соединен с вторым входом третьего элемента И, выходы блока останова по адресу и второго элемента И соединены соответственно с третьим входом первого элемента ИЛИ и информационным входом триггера, выход регистра соединен с вторым входом схемы сравнения, выход равенства которой через элемент НЕ соединен с третьим входом третьего элемента И, выход третьего элемента И соединен с первым входом второго элемента ИЛИ, выход первого элемента ИЛИ и вход пуска устройства соединены соответственно с пятым входом блока готовности и с вторым входом второго элемента ИЛИ, выход которого соединен с шестым входом блока готовности.

| Устройство для прерывания при отладке программ | 1980 |

|

SU962945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки микроЭВМ | 1986 |

|

SU1432531A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-07—Публикация

1988-04-04—Подача