Изобретение относится к вычислительной технике и может быть использовано в системах обмена информацией

Целью изобретения является повыше- ние быстродействия устройства.

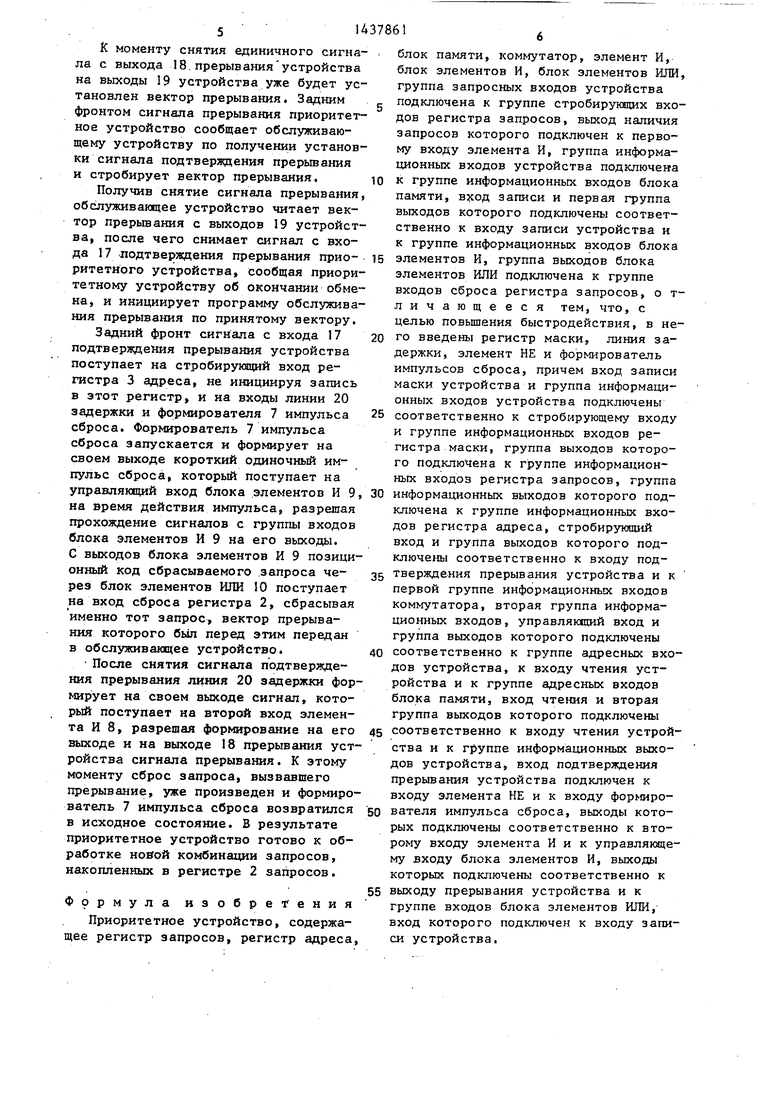

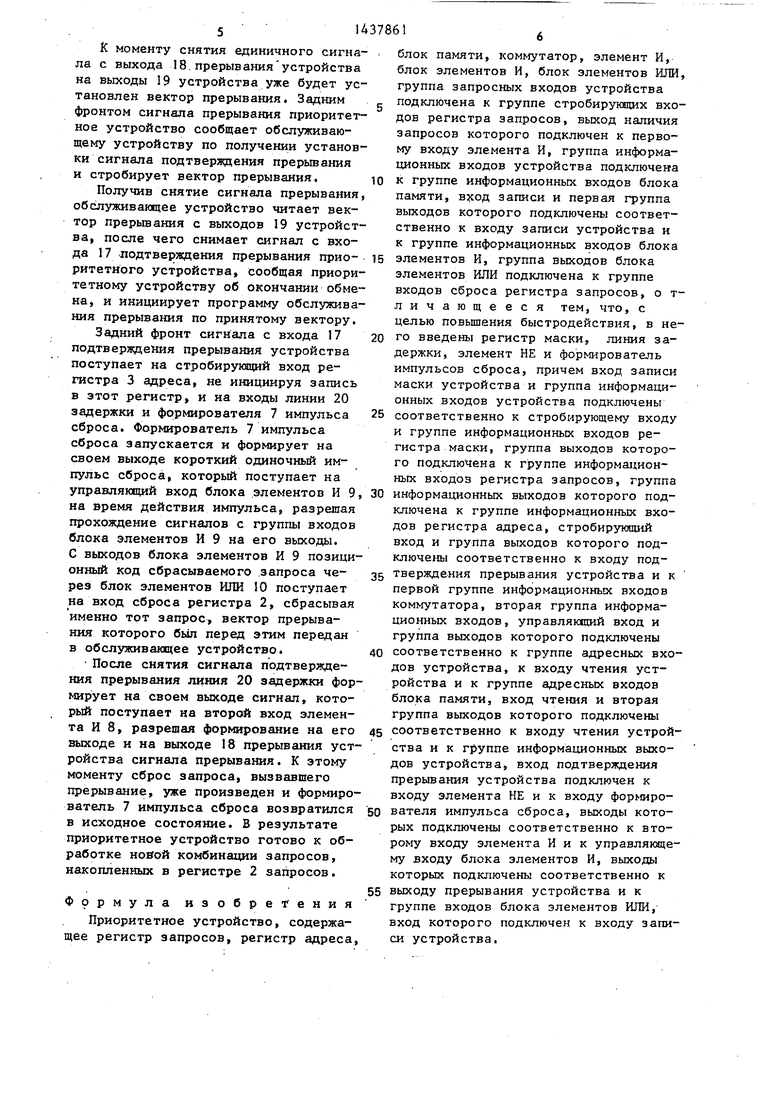

На чертеже представлена блок-схе- |Ма приоритетного устройства, ; Приоритетное устройство содержит регистр 1 маски, регистр 2 запросов, регистр 3 адреса, коммутатор 4, блок 5 памяти, элемент НЕ б,формирователь 7 импульса сброса, элемент И 8, блок элементов И 9, блок элементов ИЛИ 10 группу информационных входов 11 уст- ройства, группу адресных входов 12 устройства, вход 13 записи маски устройства, группу запросных входов 14 устройс гва, вход 15 чтения устройства, вход 16 записи устройства, вход 17 подтверждения прерывания устройства, выход 8 прерывания устройства,, группу информационных выходов 19 устройства, линию задержки 20.

Приоритетное устройство работает следуюпдам образом.

Предварительно в ячейки блока 5 памяти записывается информация, т.е. задается соответствие меядду адресом ячейки (комбинацией запросов) и ее содержимым.

Запись производится в следующем порядке.

На входе 13 устройства, на входе 15 устройства и на входе 16 устройстна устанавливаются нулевые сигналы, которые поступают соответственно на стробирую1гщй вход регистра 1 . и входы чтения и записи блока 5 памяти, в результате чего операции с регистром и с блоком 5 памяти не производятся. Нулевой сигнал с входа 15 устройства поступает на управлягаций вход коммутатора 4, в результате чего коммутатор 4 под1шючает группу входов 12 к группе адресных входов блока 5 памяти. После этого на группе входов 12 устройства устанавливается адрес ячейки блока 5 памяти, в которую заносится информация. Этот адрес через коммутатор 4 поступает на адресные входы блока 5 памяти. Одновременно с установкой адреса на входах 12 устройства на информационных входах 11 устройства устанавливается записывавмая информация, которая поступает на информационные входы блока 5 памяти. Затем на входе 16 записи устройства устанавливается единичный сигнал, который поступает на вход записи блока 5 памяти и на вход блока элементов ИЛИ 10, в результате чего происходит запись информшдии с информационных входов 11 устройства в ячейку блока 5 памяти по адресу, установленному на входах 12 устройства. Одновременно единичный сигнал с входа 16 записи устройства поступает через блок элементов ИЛИ 10 на входы сброса регистра 2 запросов, который в результате зтого обнуляется. Затем на входе 16 записи устройства вновь устанавливается нулевой сигнал, после чего с информационных входов 1i устройства и входов 12 устройства снимает- ся информация. Запись в другие ячей- 1СИ 5 памяти производится аналогично.

После того, как во все ячейки блока 5 памяти была занесена информация производится запись маски в регистр I масгда. Каждьй бит маски соответствует одному запросному входу устройства. Если необходимо запретить (замаскировать) прерывание по какому- либо запросу, соответствующий бит маски сбрасывается (устанавливается) в нулевое состояние.

Запись маски производится следукг- ЩИ.М образом.

На входах 1 устройства устанавливается записываемая информация (маска) , которая поступает на информационные входы регистра 1. Затем на входе записи маски 13 устройства устанавливается единичный сигнал, поступающий на стробирующий вход регистра 1, в результате маска записывается в регистр 1, после чего на входе 13 устройства вновь устанавливается нулевой сигнал, затем с входов II устройства снимается информация. Аналогично можно оперативно изменять информацию в регистре 1 (маскировать запросы) и во время обработки запросов приоритетным устройством.

По окончании записи информации в блок 5 памяти и в регистр 1 приоритетное устройство переводится в исходное состояние (состояние ожидания запроса) т.е. на входе 16 устройства устанавливается нулевой сигнал, а на входе 5 устройства - единичный сигнал, которьш поступает на управлягаций вход коммутатора 4 и на вход чтения блока 5 памяти, в результате чего выходы регистра 3 адреса подключаются через коммутатор 4 к ад

ресным входам блока 5 памяти, а последний переходит в режим чте1шя.

Единичный сигнал на входе 17 подтверждения прерывания устройства мо-i жет появиться лишь в ответ на установку единичного сигнала на выходе 18 прерывания устройства, поэтому в исходном состоянии на этом входе установлен нулевой сигнал, который инвертируется элементом НЕ 6. В результате с его выхода на второй вход элемента И 8 поступает единичный сигнал, разрешающий прохождение сигнала с сигнального выхода регистра 2 запросов через элемент И 8 на выход 18 прерывания устройства. Так как при записи информации в блок 5 памяти регистр 2 запросов бьш обнулен, на сигнальном выходе регистра 2 запросов установлен нулевой сигнал, кото рьш поступает на первый вход элемента И 8 и вызывает появление нулевого сигнала на выходе 18 прерывания устройства.

Одновременно нулевой сигнал с входа 17 устройства поступает на вход формирователя 7 импульса сброса, в результате чего на его выходе появляется нулевой сигнал (так как формирователь срабатывает только по заднему фронту единичного входного сигнала). С выхода формирователя 7 импульса сброса нулевой сигнал поступает на второй вход блока элементов И 9, устанавливая на его выходах нулевые сигналы, которые поступают на группу входов блока элементов ИШ1 10, Так как на вход блока элементов ИЛИ 10 также поступает нулевой сигнал, на выходах блока элементов ИЛИ 10 формируются нулевые сигналы, которые поступает на входы сброса регистра 2, разрешая запись информации в этот регистр.

До тех пор , пока не появится хотя бы один запрос на прерывание, приоритетное устройство находится в исходном состоянии. При появлении единичного сигнала на одном или нескольких входах группы запросных входов 14 устройства происходит запись соответствующих битов маски с выходов регистра 1 в регистр 2. Если все эти биты были предварительно сброшены при записи в регистр 1, т.е. все пос тупившие запросы были замаскированы, то регистр 2 останется обнуленным, и все приоритетное устройство останется в исходном состоянии. Если же

5

5 0

0 5 0

5 0 55

хотя бы один записанный в регистр 2 бит маски бьш предварительно установлен, т.е. соответствующий запрос не бьш замаскирован,.на сигнальном выходе регистра 2 появляется единичный сигнал, который поступает на первый вход элемента И 8, в результате чего на его выходе и на выходе 18- прерывания устройства формируется единичный сигнал, и в обслуживающее устройство выдается сигнал прерывания.

До тех пор, пока обслуживающее устройство не вьздает в приоритетное устройство сигнал подтверждения прерывания, поступающие незамаскированные запросы будут накапливаться в регистре 2 запросов. Сформированная таким образом в регистре 2 запросов комбинация запросов с его выхода поступает на информационньш вход регистра 3 адреса.

Когда обслуживающее устройство выдает сигнал подтверждения прерывания, с входа 17 этот сигнал поступает на стробиругощий вход регистра 3 и на входы линии 20 задержки и формирователя импуль.са 7 сброса. Формирователь 7 импульса сброса не срабатывает 1 сигнал на его выходе не изменяется. В результате по переднему фронту сигнала подтверждения прерывания происходит запись комбинации накопленных к этому моменту запросов в регистр 3. С выхода регистра 3 адрес, т.е. комбинация запросов через коммутатор 4 поступает на адресные входы блока 5, в результате через суммарное задержки коммутатора 4 и блока 5 памяти на его выходах устанавливается информация, соответствующая данной комбинации запросов. С выхода блока 5 памяти на выходы 19 устройства поступает вектор прерывания, а с вторых выходов блока 5 памяти на группу входов блока элементов И 9 поступает позиционный код обслуживаемого (сбрасываемого) запроса.

Через время задержки линии 20 задержки после установки еди1шчного сигнала подтверждения прерывания на ее входе линия 20 задержки формирует сигнал, который поступает на второй вход элемента .И 8 запрещает выдачу единичного сигнала на его выход.

В результате на выходе элемента И 8 и на выходе 18 прерывания устройства фopмIipyeтcя нулевой сигнал.

блок памяти, коммутатор, элемент И, блок элементов И, блок элементов ИЛИ, группа запросных входов устройства подключена к группе стробирукщих входов регистра запросов, выход наличия запросов которого подключен к первому входу элемента И, группа информационных входов устройства подключена к группе информационных входов блока памяти, вход записи и первая группа выходов которого подключены соответственно к входу записи устройства и к группе информационных входов блока

входов сброса регистра запросов, о т- личающееся тем, что, с целью повышения быстродействия, в не20

51Д37861

К моменту снятия единичного сигна- ла с выхода 18.прерывания устройства на выходы 19 устройства уже будет установлен вектор прерывания. Задним фронтом сигнала прерывания приоритетное устройство сообщает обслуживающему устройству по получении установки сигнала подтверждения прерывания и стробирует вектор прерывания. ю

Получив снятие сигнала прерывания, обслуживающее устройство читает вектор прерьшания с выходов 19 устройства, после чего снимает сигнал с входа 17 лодтверждения прерывания прио- is элементов И, группа выходов блока ритетного устройства, сообщая приори- элементов ИЛИ подключена к группе тетному устройству об окончании обмена, и инициирует программу обслуживания прерывания по принятому вектору.

Задний фронт сигнала с входа 17 подтверждения прерывания устройства поступает на стробирующий вход регистра 3 адреса, не инициируя запись в этот регистр, и на входы линии 20 задержки и формирователя 7 импульса сброса. Формирователь 7 импульса сброса запускается и формирует на своем выходе короткий одиночный импульс сброса, который поступает на управляющий вход блока элементов И 9, 30 информационных выходов которого под- на время действия импульса, разрешая ключена к группе информационных входов регистра адреса, стробирующий вход и группа выходов которого подключены соответственно к входу под- 35 тверждения прерывания устройства и к первой группе информационных входов коммутатора, вторая группа информационных входов, управляюций вход и группа выходов которого подключены 40 соответственно к группе адресных входов устройства, к входу чтения устройства и к группе адресных входов блока памяти, вход чтения и вторая группа выходов которого подключены та И 8, разрешая формирование на его 45 соответственно к входу чтения устрой- выходе и на выходе 18 прерывания уст- ства и к группе информационных выхо- ройства сигнала прерывания. К этому моменту сброс запроса, вызвавшего

го введены регистр маски, линия задержки, элемент НЕ и формирователь импульсов сброса, причем вход записи маски устройства и группа информационных входов устройства подключены 25 соответственно к стробирующему входу и группе информационных входов регистра маски, группа выходов которого подключена к группе информационных входов регистра запросов, группа

прохождение сигналов с группы входов блока элементов И 9 на его выходы. С выходов блока элементов И 9 позиционный код сбрасываемого запроса через блок элементов ИЛИ JO постуцает на вход сброса регистра 2, сбрасывая именно тот запрос, вектор прерывания которого бьш перед этим передан в обслуживающее устройство.

После снятия сигнала подтверждения прерывания линия 20 задержки формирует на своем выходе сигнал, который поступает на второй вход элемендов устройства, вход подтверждения прерывания устройства подключен к входу элемента НЕ и к входу формиропрерывание, уже произведен и формирователь 7 импульса сброса возвратился в исходное состояние. В результате приоритетное устройство готово к обработке новой комбинации запросов, накопленных в регистре 2 запросов.

Формула изобретения Приоритетное устройство, содержащее регистр запросов, регистр адреса.

блок памяти, коммутатор, элемент И, блок элементов И, блок элементов ИЛИ группа запросных входов устройства подключена к группе стробирукщих входов регистра запросов, выход наличия запросов которого подключен к первому входу элемента И, группа информационных входов устройства подключена к группе информационных входов блока памяти, вход записи и первая группа выходов которого подключены соответственно к входу записи устройства и к группе информационных входов блока

элементов И, группа выходов блока элементов ИЛИ подключена к группе

входов сброса регистра запросов, о т- личающееся тем, что, с целью повышения быстродействия, в неэлементов И, группа выходов блока элементов ИЛИ подключена к группе

информационных выходов которого под- ключена к группе информационных входов регистра адреса, стробирующий вход и группа выходов которого подключены соответственно к входу под- тверждения прерывания устройства и к первой группе информационных входов коммутатора, вторая группа информационных входов, управляюций вход и группа выходов которого подключены соответственно к группе адресных входов устройства, к входу чтения устройства и к группе адресных входов блока памяти, вход чтения и вторая группа выходов которого подключены соответственно к входу чтения устрой- ства и к группе информационных выхо-

го введены регистр маски, линия задержки, элемент НЕ и формирователь импульсов сброса, причем вход записи маски устройства и группа информационных входов устройства подключены соответственно к стробирующему входу и группе информационных входов регистра маски, группа выходов которого подключена к группе информационных входов регистра запросов, группа

информационных выходов которого под- ключена к группе информационных входов регистра адреса, стробирующий вход и группа выходов которого подключены соответственно к входу под- тверждения прерывания устройства и к первой группе информационных входов коммутатора, вторая группа информационных входов, управляюций вход и группа выходов которого подключены соответственно к группе адресных входов устройства, к входу чтения устройства и к группе адресных входов блока памяти, вход чтения и вторая группа выходов которого подключены соответственно к входу чтения устрой- ства и к группе информационных выхо-

дов устройства, вход подтверждения прерывания устройства подключен к входу элемента НЕ и к входу формирователя импульса сброса, выходы которых подключены соответственно к второму входу элемента Ник управляющему входу блока элементов И, выходы которых подключены соответственно к

выходу прерывания устройства и к группе входов блока элементов ИЛИ, вход которого подключен к входу записи устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Приоритетное устройство | 1989 |

|

SU1651286A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1287155A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для контроля блоков памяти | 1991 |

|

SU1833920A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для обработки запросов | 1988 |

|

SU1580365A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах обмена информацией. Цель.изобретения - повышение быстродействия, Приоритетное устройство содержит регистр 1 маски, регистр 2 запросов, регистр 3 адреса, коммутатор 4, блок 5 памяти, формирователь импульса 7, элемент ИЗ, блок элементов И 9, блок элементов ИЛИ 10. Информация об абоненте, поступающая на информационный вход 1 устройства, записывается в ячейки блока 5 памяти, адреса которых устанавливаются на адресном входе 12 устройства, ив регистр 1 маски. Информацию в регистре 1 маски можно оперативно изменять и в дальнейшем в процессе работы устройства. При появлении незамаскированного (в регистре 1 маски) запроса на входе 14 устройства он зaпo aIнaeтcя в регистре 2 запросов, в результате чего на выходе прерыг а шя 18 устройства появляется активный сигнал. В ответ обслуживающее устройство уста- }1авл вает активньй сигнал на входе подтверждения прерывания 17 приоритетного устройства. По этому сигналу происходит запись в регистр 3 адреса комбинации запросов, накопленных в регистре 2 запросов. Адрес с выхода регистра 3 адреса проходит через коммутатор 4 и поступает на адресный вход блока 5 памяти. В результате на выходах блока памяти устанавливается информация, соответствующая данной комбинации запросов, на информационный выход 19 устройства поступает вектор прерывания, а на первый вход блока элементов И 9 поступает позиционный код загфоса, имеющего в данной комбинации наивысший приоритет. В приоритетном устройстве производится параллельный поиск запроса, имеющего наивысший приоритет, а также производится маскирование запросов без останова обработки запросов. 1 ил. уе (Л |й О9 М 00 О5

| Приоритетное устройство | 1982 |

|

SU1056194A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приоритетное устройство | 1985 |

|

SU1411744A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-15—Публикация

1986-12-10—Подача