4J Ш

LZ

сл

4 оо ч

00 О О5

матор 14, накапливающий сумматор 15, элемент И-ПЕ 16, группу прямых информационных входов 17 устройстпа, группу инверсных информационных выходов 18 устройства, выход 19 конца счета устройства, тактовый вход 20 устройства, вход 21 включения режима счета устройства, информационный выход 22 устройства, счет последовательного суммироваття количества единиц в трех разрядах каждого блока 3 фиксации единиц группы с помощью элементов ШШ 11-13, одноразрядного сумматора 1А и накапливающего сумматора 15 достигается сокращение времени подсчета количества единиц. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Интегродифференциальный вычислитель | 1981 |

|

SU1007105A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСяТичНОгОВ дВОичНый | 1979 |

|

SU849197A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство для приведения 1-кода Фибоначчи к минимальной форме | 1989 |

|

SU1665515A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля цифровых блоков. Цель изобретения - повышение быстродействия устройства. Устройство содержит элементы И 1,2, групп блоков 3 фиксации единиц, элементы И 4-7 блока 3 фиксации единиц группы, триггер 8, элементы ИЛИ 9,10 блока 3 фиксации единиц группы, эле- менты ИПИ 11-13, одноразрядный сум

1

Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля цифровых блоков.

Целью изобретения является повышение быстродействия устройства.

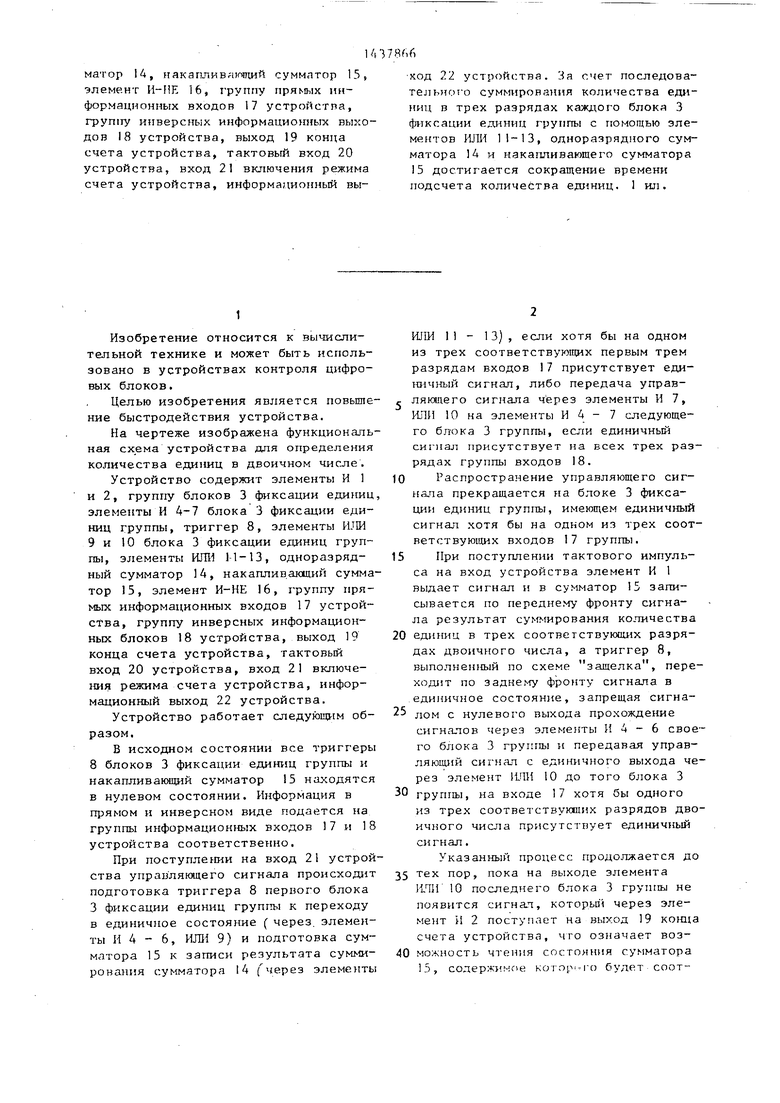

На чертеже изображена функциональная схема устройства для определения количества единиц в двоичном числе.

Устройство содержит элементы И 1 и 2, группу блоков 3 фиксации единиц элементы И 4-7 блока 3 фиксации единиц группы, триггер 8, элементы ИЛИ 9 и 10 блока 3 фиксации единиц группы, элементы ИЛИ М-13, одноразрядный сумматор 14, накаплив.акадий сумматор 15, элемент И-НЕ 16, группу прямых информационных входов 17 устройства, группу инверсных информационных блоков 18 устройства, выход 19 конца счета устройства, тактовый вход 20 устройства, вход 21 включения режима счета устройства, информационный выход 22 устройства.

Устройство работает следующим образом.

В исходном состоянии все триггеры 8 блоков 3 фиксации единиц группы и накапливающий сумматор 15 находятся в нулевом состоянии. Информация в прямом и инверсном виде подается на группы информационных входов 17 и 18 устройства cooTBeTCTBetnio.

При поступлении на вход 21 устройства управляющего сигнала происходит подготовка триггера 8 первого блока 3 фиксации единиц группы к переходу в единичное состояние ( через, элементы И 4 - 6, ИЛИ 9) и подготовка сумматора 15 к записи результата сумми- роваушя сумматора 14 { через элементы

ИЛИ 11 - 13), если хотя бы на одном из трех соответствую1циз первым трем разрядам входов 17 присутствует еди- HH4}ib i сигнал, либо передача управ- ляющего сигнала ч ерез элементы И 7, ИЛИ 10 на элементы И 4 - 7 следующего блока 3 группы, если единичный сигнал присутствует на всех трех разрядах группы входов 18.

Распространение управляющего сигнала прекращается на блоке 3 фиксации единиц группы, имеющем единичный сигнал хотя бы на одном из трех соответствующих входов 17 группы.

При поступлении тактового импульса на вход устройства элемент И 1 выдает сигнал i в сумматор 15 записывается по переднему фронту сигнала результат суммирования количества

единиц в трех соответствуюсцих разрядах двоичного числа, а триггер 8, выполненный по схеме защелка, переходит по заднему фронту сигнала в единичное состояние, запрещая сигналом с нулевого выхода прохождение

сигналов через элементы И 4 - 6 своего блока 3 группы и передавая управ- ляю11Ц1Й сигнал с единичного выхода через элемент 1ПИ 10 до того блока 3

группы, на входе 17 хотя бы одного из трех соответствукхних разрядов двоичного числа присутствует единичный сигнал.

Указанный процесс продолжается до

тех пор, пока на выходе элемента .(ПИ 10 последнего блока 3 группы не появится сигнал, которьо через элемент И 2 поступает на выход 19 конца счета устройства, что означает возможность чтения состояния сумматора 15, содержимое которого будет соответстпонать количяству единиц в дво- ич}юм числе. Этот же сигнал, поступая через элемент H-ilE 6 на вход элемента И 1, прекращает подачу так- 1 овьгх импульсов.

Формула изобретения

Устройство для определения количества единиц в двоичном числе, содержащее два элемента И, элемент И-ИЕ и группу блоков фиксации единиц, кая:- дый из которых содержит два элемента И, первый элемент ИЛИ и триггер, причем первый вход первого элемента И - является тактовым входом устройства, второй вход первого элемента И, первый вход второго элемента И и первый вход элемента И-ИЕ объединены и образуют вход включения режима счета уст-2о операнда и переноса одноразрядного

ройства, выход элемента И-НЕ соединен с третьим входом первого элемента И, выход которого соединен с так- ТОВЫМ51 входами триггеров всех блоков

фиксации единиц группы, выход второ- 25 тора, остальные разряды информационго элемента И является выходом конца работы устройства, в ка5едом блоке фиксации единиц группы прямой выход триггера соединен с первым входом первого элемента ИЛИ, первый вход первого элемента И подключен к соот- ветствуюи(ему разряду группы прямых информационных входов устройства, первый вход второго элемента И подключен к соответствующему разряду группы инверсных информационных входов устройства, второй вход первого элемента И объединен с вторым входом второго элемента И, выход которого

соединен с вторым входом первого эле- 40 Щим разрядам группы прямых информа- мента ИЛИ, выход первого элемента ционных входов устройства, третий и ИЛИ каждого блока фиксации единиц четвертый входы второго элемента И группы, кроме последнего, соединен с подключены к соответствуюпи1М разря- вторым входом первого элемента И пос- дам групп инверсных информационных ледующего блока фиксации единиц груп- 45 входов устройства, вторые входы третьего и четвертого элементов И динены с вторым входом первого мента И, инверсный выход тригге соединен с третьими входами пер третьего и четвертого элементов

пы, выход первого элемента ИЛИ последнего блока фиксации единиц группы , соединен с вторыми входам второго элемента И и элемента И-НЕ, второй вход первого элемента И первого блоСоставитель В.Гречнев Редактор Е.Копча Техред Л.Серлюкова Корректор aкcим шинeц

Заказ 5895/49 Тираж 704Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

/ К66-1

ка фиксации е,п.пниц группы ):одк. к входу включения режима сче.та уг:т- ройства, о 1 л и ч а PJ щ е е с я тем, что, с целью гтовышения быстродействия устройстве, в него введены три элемента ИЛИ, одноразрядный сумматор, накап;п1ваю 1щй сумматор, в каждый блок фиксапии единиц группы вве10 дены Второй элемент ИЛИ и третий и четвертый элементы И, причем выходы первого, третьего и четвертого элементов И каждого блока фиксации единиц группы соединены с соответстную15 щим входом первого, второго и третьего элементов ИЛИ соответственно, выходы первого, второго и третьего элементов ИЛИ соединены соответственно с входаьш первого операнда, второго

сумматора, выход результата и переноса которого соединен соответственно с первым и вторым разрядами информа- цио1П{ого входа накапливающего сумманого входа которого соединены с шиной нулевого потенциала устройства, выход первого элемента И соединен с тактовым входом накапливающего сумма- 0 тора, информационный выход которого является информационным выходом устройства, в блоке фиксации единиц группы выходы первого, третьего и четвертого элементов И соединены с соответствующими входами второго элемента ИЛИ, выход которого соединен с информационным входом триггера, первые входы третьего и четвертого элементов И подключены к соответствую5

тьего и четвертого элементов И объединены с вторым входом первого элемента И, инверсный выход триггера соединен с третьими входами первого, третьего и четвертого элементов И.

| Устройство для определения количества единиц в двоичном числе | 1984 |

|

SU1185340A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения количества едениц в двоичном числе | 1977 |

|

SU716041A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-15—Публикация

1986-11-26—Подача