того элемента И подключен к входу значений функции вычислителя, выход этого элемента И подключен к первому входу третьего элемента ИЛИ, к второму входу которого подключен выход juecToro элемента И, выход третьего элемента ИЛИ соединен с входом последовательного ввода информации регистра функции, установочные входы которого соединены с второй группой установочных входов вычислителя, установочные входы первого регистра коэффициентов подключены к третьей группе установочных входов вычислителя, выход этого регистра соединен с его входом последовательного ввода информации и первым входом седьмого элемента И, выход которого соединен с информационным входом второго блока формирования дополнительного кода, выхо второго элемента ИЛИ соединен с первым входом восьмого элемента И, установочные входы второго регистра коэффициентов Подключены к четвертой группе установочных входов вычислителя,- выход этого регистра соединен с его входом последовательного ввода информации и первым входом девятого элемента И, .выход которого соединен с информационным входом третьего блока формирования дополнительного кода, пятый выход блока (синхронизации соединен с вторым входом восьмого элемента И и первым входом десято.о элемента И, выход восьмого

элемента И соединен с входом уставовки в единицу третьего триггера, выход которого соединен с вторым входом седь мого элемента И, выход десятого элемента И соединен с входом установки в единицу четвертого триггера, выход которого соединен с вторым входом девятого элемента И, шестой выход блока синхронизации подключен к входам синхрониэации регистра результата, регистра функции, первого и второго регистров коэффициентов, седьмой и восьмой выходы блока синхронизации соединены соответственно с- четвертым и пятым входами блока знака, отличающийся тем, что, с целью расшир)ения функциональных возможностей за счет вычисления преобразований второго порядка, в него введен регистр промежуточный результатов, установочные входы которого подключены к пятой группе установочных входов вычислителя, вход последовательного ввода информации регистра промежуточных результатов подключен к выходу второго элемента ИЛИ, выход эуого регистра соединен с вторым входом пятого элемента И а вход синхронизации подключен к шестому выходу блока синхронизации, выход третьего элемента ИЛИ соединен с вторым входом десятого элемента И, выход регистра функции соединен со вторым входом шестого элемента И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегро-дифференциальный вычислитель | 1980 |

|

SU960813A1 |

| Интегро-дифференциальный вычислитель | 1981 |

|

SU1020823A1 |

| Интегро-дифференциальный вычислитель | 1983 |

|

SU1108445A2 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU955051A1 |

| Интегро-дифференциальный вычис-лиТЕль | 1979 |

|

SU798902A1 |

| Цифровой регулятор | 1981 |

|

SU974336A1 |

| Цифровой регулятор | 1980 |

|

SU938255A1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Цифровой регулятор | 1979 |

|

SU938253A1 |

| Устройство для определения оптимальных траекторий | 1983 |

|

SU1223240A1 |

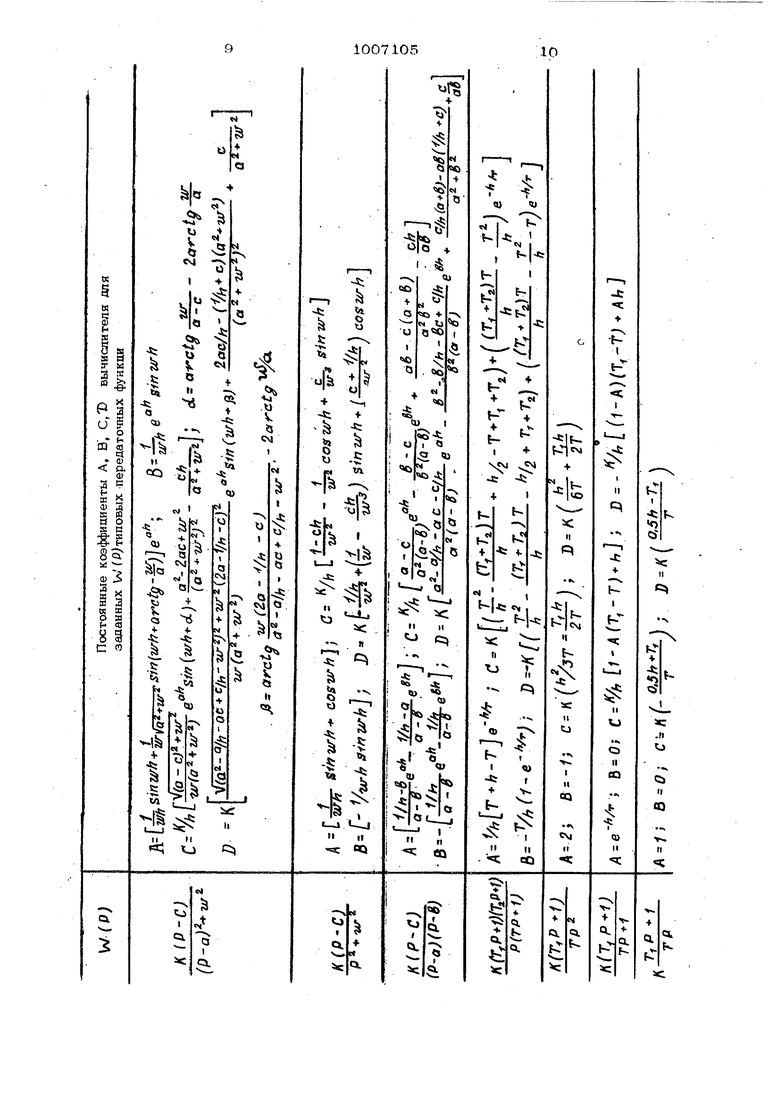

ИНТЕГРО-ДИФФЕРЕНЦИАЛЬНЫЙ ВЫЧИСЛИТЕЛЬ, содержаюий регистр результата, первый и второй регистры коэффициентов, ретостр функции, блока знака/блок синхрсйяизации, первый и второК сумматоры, три блока формирования дополнительного кода, три элемента ИЛИ, Десять элементов И, элемент задержки и четыре триггера, причем установочные входы регистра результата подключены к первой группе установочных входов вычислителя, выход регистра результата подключен к первому входу первого элемента И и через элемент задержки - к первому входу второго элемента И и ин- . формаиионному входу первого блока формирования дополнительного кода, выход которого соединен с ивфсфмационным выходом вычислителя и первым входом третьего элемента И, выходы первого и второго элементов И подключены к первсялу и ъторому входам первого элемента ИЛИ соответственно, выход которого соединен с первым входом первого сумматора, выход которого соединен с входом последовательного ввода информации регистра результата и первым входом блока знака, первый выход которого подключен к управляющему входу первого и второго блоков формирования дополнительного кода, второй выход блока знака подключен к yipравпяющему входу третьего блока формирования дополнительного кода, третий выход блока знака - к выходу знака вычислителя, выходы второго и третьего блоков формирования дополнительного кода подключены к первому и второму входу второго сумматора соответственно, выход которого соединен с вторым входом первого сумматора, второй вход.блока знака . соединен с входом знака начального значения вычислителя, первый выход блока синхронизации соединен с третьим входом блока знака, второй выход блока синхронизации соединен с входами установки в ноль первого, второго, третьего и четвертого триггеров, третий выход блока синхронизации соединен с входом установки в единицу первого триггера, прямой выход этого TiMirrepa - с вторым входом первого элемента И, а инверсный - с вторым входом второго элемента И, четвертый выход блока син}фонизации соединен сл с входо. установки в единицу второго триггера, прямей выход которого соединен с первым входом четвертого элемен та И и вторым входом третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, инверсный выход второготриггера соединен с третьими входами первого и второго элементов И и первыми входами пятого ti шестого элементов И, выход пятого элемента И соединен с вторым входом второго элемента ИЛИ, второй вход четвер

Изобретение относится к автоматике и вычислительной технике и может быть использовано для моделирования и управления динамическими объектами в различных отраслях промышленности.

Известны аналоговые интегро-диффе- ренциальные устройства, содержащие аналоговые интеграторы, сумматоры и масштабные блоки для задания коэффиоиентов передачи ГХЗ.

Недостатком аналоговых интегро-дифференциальных устройств является низкая точность вычислений выходных сигналов в случае достаточно больших значений постоянных времени, характертых для многих технологических процессов.

Известны более точные интегро-дифференциальные устройства типа цифровых дифференциальных а11ализаторов.

которые содержат ряд цифровых интеграторов, коммутируемых между собой согласно заданному интегро-дифференциальному преобразованию

Недостатками таких интегро-дифференциальных устройств являются низкое бысродействие и сложность реализации.

Наиболее близким техническим решением к предложенному является интегродифференциапьный вычислитель, содержаншй семь регистров, два сумматора, три блока формирования дополнительного кода, блок знака, блок синхронизации, четыре триггера, двенадцать элементов И, четыре элемента ИЛИ и элемент задержки Сзз.

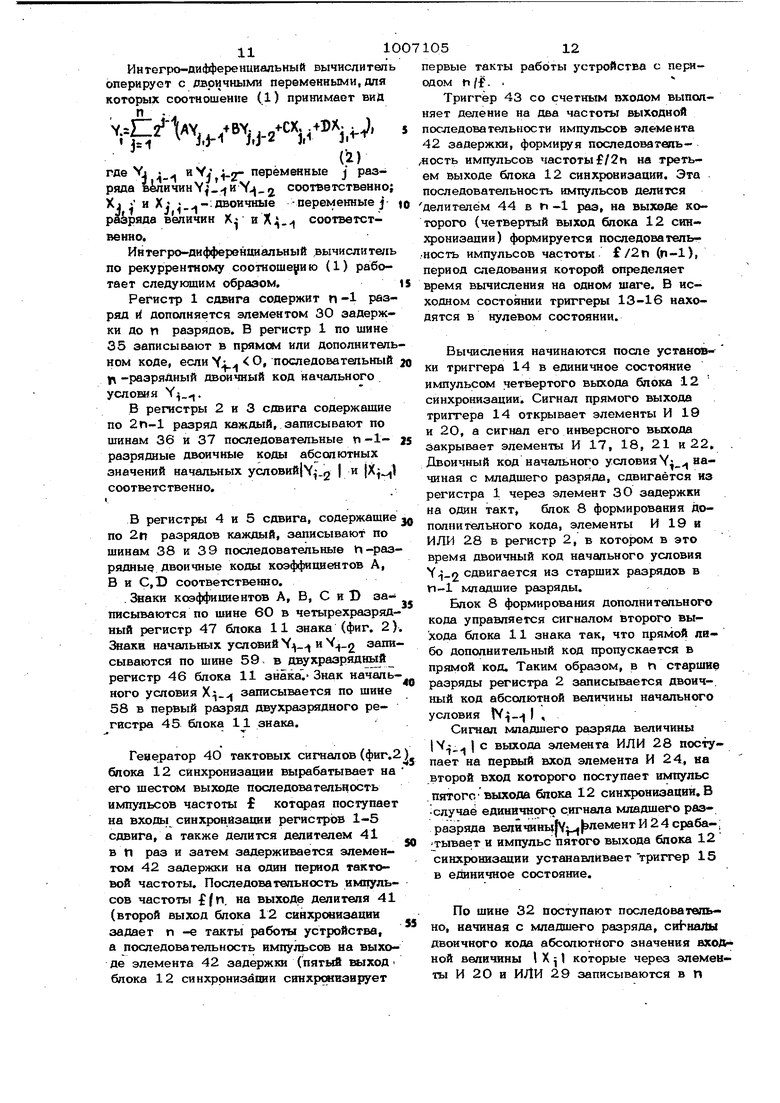

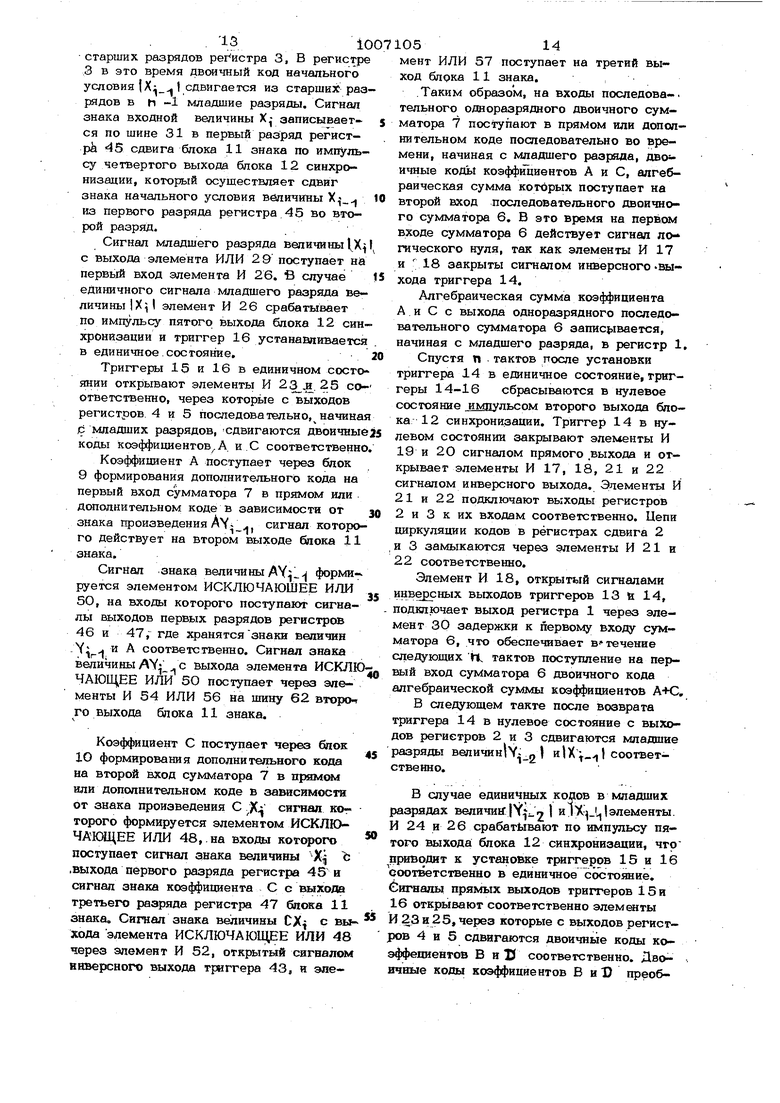

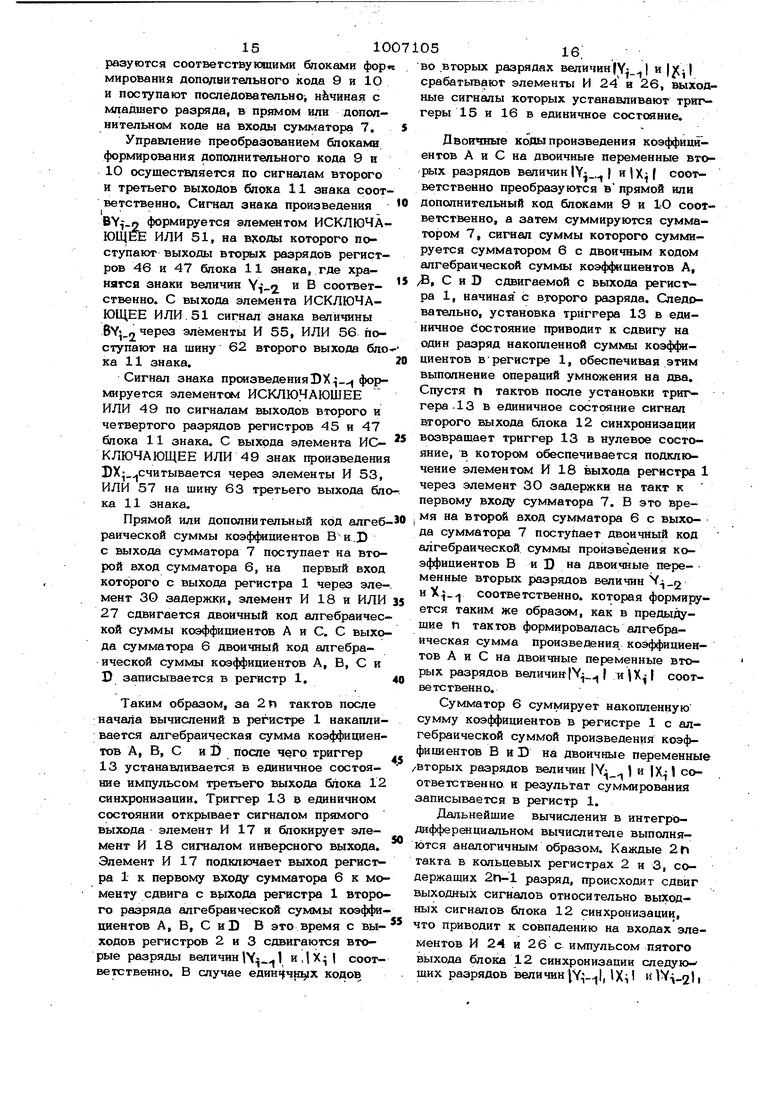

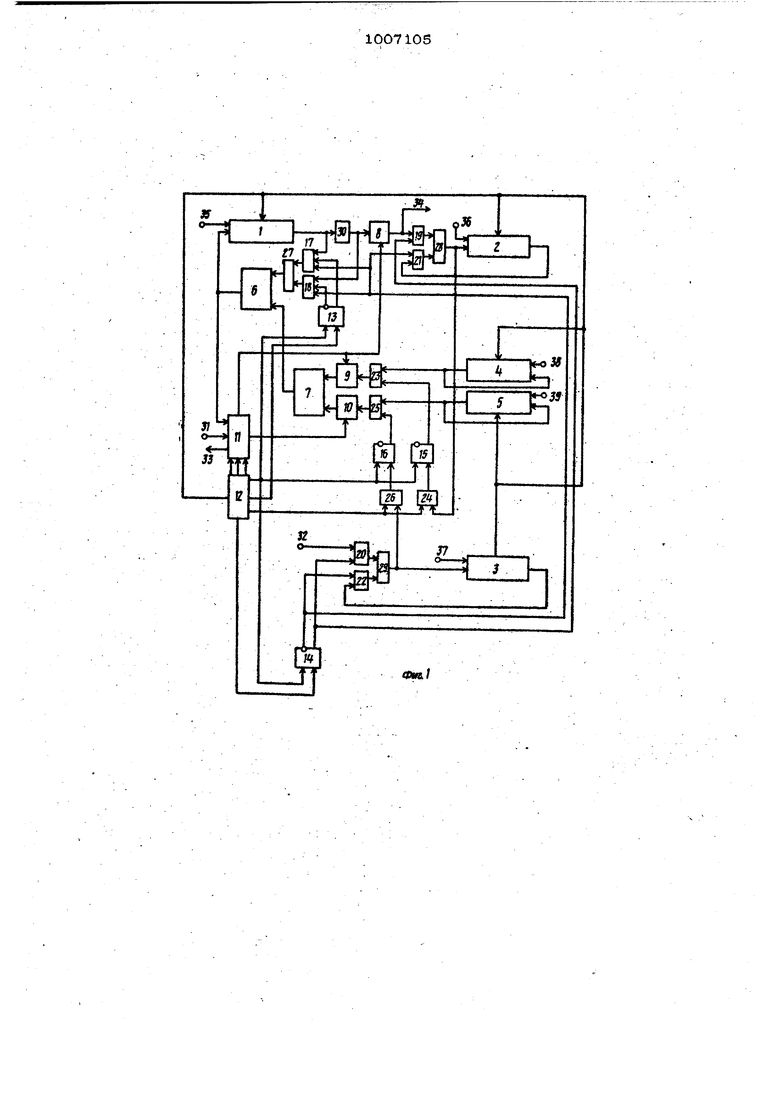

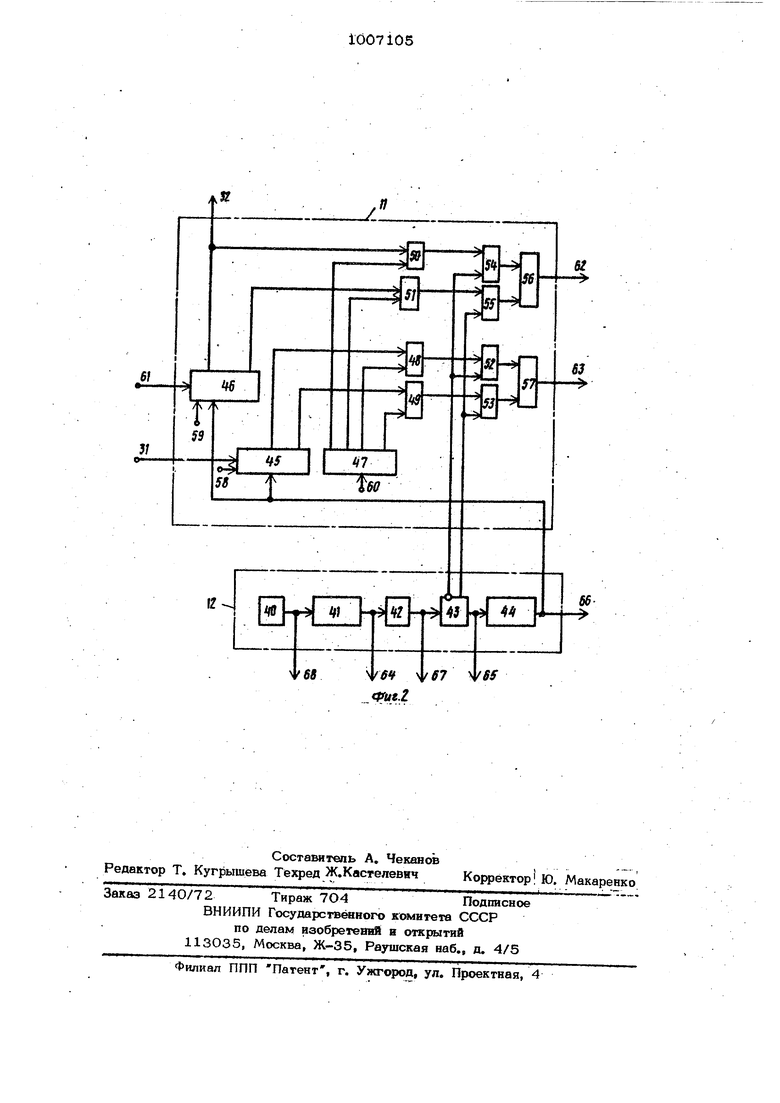

Недостатками известного вычислителя являются относительная сложность его реализаций и ограниченные функоионапь- i ные. возможное711. Целью изобретення является расширение функциональных возможностей за счет вычисления преобразований второго поряд ка,. Поставленная цель достигается тем, что ннтегро-дифференциальный вычислитель, содержащий регистр результата, первый и второй регистры коэффициентов, регистр функции, блок знака, блок синхронизации, первый и ВторсЛ сумматоры, три блока формирования дополнительного кош, три элемента ИЛИ, десять элементов И, элемент задержки и четыре..триггера, причем установочные входы регистра результата подключены к первой входов начальной установки вычисли-теля, этого регистра подключен к первокцг входу первого элемента И и через элемент задержки - к цервому входу второго элемента И и информационному вкоду первого блока формирования дополнительного кода, выход которого. соединен с информационным шлходом вычислителя и первым входом тре.тьего элементе И, выходы первого и второго элементов И подключены к neiffioiv и второму входу первого элемента ИЛИ соответственно, выход которого средьнен с первым входом первого сумматора, выход которого соедини с входом последовательного ввода информации регистра результата и первым входом блока знака, первы выход которого подключен к у1фавляюшему входу первого и второго блоков формирования дополнительного кода, второй вход блока знака подключен ic управляющему входу третьего блслса ф| п«аровавия допол нительного кода, третий выход ока знака подклкучен к выходу знака вычислителя, выходы второго и третьего блоков фо мирования дополнительного кода подключе ны к первому и второму входу второго (Сумматора соответственно, выход которого соединен с вторым входом первого -cyMMia тора, второй вход бпока знака сое.дине с входом знака начал1лого зваченйя вычислителя, первый ход блока. синхронизации соединен с гр&еьам блока знака, второй выход Cnoica син хровизации Соединен с входами устшовки 6 ноль первого, второго, lEfiE ero и чет вертого триггеров, третий выход блока жнхронизации соединен с входом установ ки в единицу первого тригг ера, прямой выход этого триггера соединен с вторым входом первого элемента И, а внверсшдй с вторым входом второго.элемента И, четвертый выход блока сии: ронизации соединен с щзюахял установки в единицу второго триггера, прямей выход которого соединен с первым входом четвертого элемента И и вторым входом Т1Эётьего элемента И, выход i которого соединен с первым входом втсфбго элемента ИЛИ, инверсный вторюго триггера соединен с третьимивходами первого и второго элементов И и первыми входами п того и шестого элементов И, выход пятого элемента И соединен с втсфым входом второго элемента ИЛИ, вто1М}й вход четвертого элемента И подключен к входу значений функции вычислителя, выход этого элемента И подключен к первому входу третьего элемента ИЛИ, к второ му входу которого подключай выход шестого элемента И, выход третьего элемента ИЛИ соединен с входю последовательного ввода информации р тистра функции, установочные входы которого соедин ы с второй установочных входов вычислителя, установочные входы первого регистра коэффициентов подключены к третьей группе установочных входов вы чиспнтеля, выход этого регистра соединен с его входом последовательного ввода информации и первым входе седьмого элемента И, выход которого соединен с информационным входом вт(ф(го блока формирования дополнительного кода, выход второго элемента ИЛИ соединен с первым BxctfioM восьмого элемента И, установочные входы второго регистра коэффициентов пошшючены к четвертой группе установочных входов шдчислителя, выход этого регистра соединен с его вхо дом последователыюго ввода информации и первым входом девятог о элемента И, выход которого соединен с информационным входом третьего блока формирования дополнительного кода, пятый выход блсяса синхронизации соединен с вторым входом восьмого элемента И и первым входом десятого элемента И, выход восьмого элемента И соешшен с входом установки в единицу третьего триггера, выход соедини с вторым входсм седьмо го элемента И, выход десятого элемента , И соединен с входом устансжкн в единиt четвертого триггера, выход котфого : соединен с вторым входом девятого элемента И, шестой выход блока синхрт(йзахши подключен к входам синхронизации регистра результата, регистра функции, ; первого и второго регистров коэффициентов, седьмой и восьмой выходы блока) синхронизации соединены соответственно 510 с четвертым и пятым .входами блока зна ка, введен регистр промежуточных резуль татов, причем установочные входы этого регистра подключены к пятой группе установочных входов вычислителя, вход последовательного ввода информации этого регистра подключен к выходу второго элемента ИЛИ, выход этого регистра соединен с вторым входом пятого элемен та И, а вход синхронизации подключен к шестому выходу блока синхронизации, вы ход третьего элемента ИЛИ соединен с .вторым входом десятого элемента И, выход регистра функции соединен с вторым входом шестого элемента И. На фиг. 1 изображена структурная схема интегро-дифференциалЪного вычислителя; на фиг, 2 - структурная схема &1ока знака и блока синхронизации. И н тегро-диффере нциал ьный вычисли тел содержит регистр 1 результата, регистр 2 промежуточных результатбв, регистр З функции, первый и второй регистры 4 и 5 коэффициентов соответственно, два сум матора 6 и 7, три блока формирования дополнительного кода 8-10, блок 11 зна ка, блок 12 синхронизации, четыре триггера 13-16, Десять элементов И 17-26 три элемента ИЛИ 27-29, элемент 30 задержки, две входные 31, 32 и две выходные 33, 34 шины, устройства, шины 35-39 ввода данных в регистры 1-5 соответственно. Блок синхронизации (фиг. 2) содержит генератор 4О тактовых сигналов, Де литель 41 частоты, элемент 42 задержки, триггер 43 со счетным входом, дели тель 44 частоты. Блок 11 знака содержит два двухразрядных регистра 45 и 46 сдвига, четырехразрядных статически регистр 47, четыре элемента ИСКЛЮЧАЮШЕЕ ИЛИ 48-51, четыре элемента И 52-55, два элемента ИЛИ 56-57, шины 58-60 ввода данных в регистры 45-47 соответственно, две входные 31, 61 и три выходные 33, 62 и 63 шины. Шины 31 и 61 являются первым и вторым вхо дами блока 11 знака соответственно. Ши ны 33, 62 и 63 являются первым, вто1ЛЫМ и третьим выходами блока 11 знака. Выходные шины 64-68 являются вт fbiM, третьим, четвертым пятым н шеетым выходами блока 12 синхронизапии. Первая входнвя шина 31 устройства соединена с первым входом блока 11, первый выход которого соединен с первой выходной шиной 33 устройства. . Выход первого сумматора 6 соединен с входом регистра 1 и вторым входом 056 блока 11 знака, второй выход которого соединен с первыми входами первого блока 8 формирования дополнительного кода, и второго блока 9 формирования дополнительного кода, а третий выход соединен с первым входом третьего блока 1О формирования дополнительного кода. Блок Г2 синхрюнизации соединен пер-. вым выходом с третьим входом блока 11 знака, вторым выходом - с первыми входами первого, второго, третьего и четвертого триггеров 13-16, причем третий выход блока 12 соединен с вторым входомтриггера 13, а четвертый выход-- с вторым входом триггера 14, Выход регистра 1 соединен с входом элемента 30 задержки и с первым входом элемента И 17, выход и второй вход которого соединен соответственно с первым входом элемента или 27 и с.прямым выходом триггера 13, Элемент ЗО задержки соединен с вторым входом блока 8 и с первым входом элемента И 18, второй вход и выход которого соединены соответственно с инверсным выходом триггера 13 и с вторым входом элемента ИЛИ 27, выход которого подключен к первому входу сумматора 6.. Триггер 14 соединен прямым выходом с первыми входами элементов И 19 и 20. Инверсный выход триггера 14 соединен с первыми входами элементов И 21 и 22 и с .третьими входами элементов И 17 Выход блока 8 соединен с второй вы- , ходной шиной 34 устройства и с вторым входом элемента И 19, выход, которого подключен к первому входу элемента ИЛИ 28, второй вход и выход которого соединены соответственно с выходом эле:мента И 21 и с входом регистра 2. Второй вход и выход элемента И 20 соединены соответственно с второй входной шиной 32 устройства и с первым входом элемента ИЛИ 29. Выход элемента И 22 соединен с вторым входом элемента ИЛИ 29, выход которого соединен с входом регистра 3. Выход регистра 4 соединен со своим входом и с первым входом элемента И 23, выход и второй вход которого соединены соответственно с вторым входом блока 9 и с выходом триггера 15. Выход элемента И 24 подключен к второму входу триггера 15. Первый и второй входы элемента И 24 соответственно соединены с выходом элемента ИЛИ 28 и с ьятым выходом блока 12 синхронизации. 7100 Выход регистра 5 соединен со своим входом и с первым входом элемента И 25, выход и второй вход которого соеди- иены соответственно с вторым входом блока 1О и с выходом триггера 16. Выход элемента И 26 подключен к второму входу триггера 16, Первый и второй входь элемента И 26 соответственно соединены с пятым выходом блока 12 синхронизации и с выходе элемента ИЛИ 29. Выходы второго и третьего блоков 9 и Ю формирования дополнительного кода соединены соответственно с первым и вторым входами сумматора 7,,выход которо.го подключен к второл у входу сумматора 6; Шины 35-39 ввода данных соединены соответственно с г гистрами 1-5, входы синхронизаши которых соединены с шеетым выходом блока 12 синхронизации. Выход регистра 2 соединен с вторым входом элемента И 21. Выход регистра 3 соединен с вторым входом элемента И 22. Выход элемента ИЛИ 29 соединен с вторым входом элемента И 26. Выход генератора 40 тактовых сигналов (фиг. 2) соединен с входом делителя 41 частоты и с шиной 68, являквдейся шестым выходом блока 12 синхронизации. Вход элемента 42 задержки соединен с №1ходом делителя 41 частоты и с шиной 64, являющейся вторым вмходом блока 12 синхронизации. Счетный вход тртггера 43 соединен с выходом элемента 12 задержки и с шиной 67, являющейся пятым выходом блока 12 синхронизации. Вход делителя 44 частоты соединен с выы соединен с выходом переноса триггера 43 и с шиной 65, являющейся третьим выходом блока 12 синхронизации. Выход делителя 44 частоты соединен с шиной 66, являющейся четвертым jBbixoflOM блока 12 синхронизации; и с шинами сдвига регистров , 45 и 46 блока 11 знака. Шины 58-60 ввода данных соединены соответственно с регистрами 45-47. Входная шина 31 соединена с информационным входсш регистра 45 сдвига, первый и вто рой выходы которого подалк 1ены сортветветственно к периым входам элементов; ИОСЛЮЧАЮЩЕЕ ЙЛИ 48 и 49. Входная шина 61 соединена с .информационным вхоД(А1 регистра 46 сдвига, первый и второй выходы которого подключены соотвес1ъенно с шинсй 39, с первым входсяй элемента ИСКЛЮЧАЮШЕЕ ИЛИ 50 и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 51. Выход и второй вход элемента ИСКЛЮЧАЮЩрЕ ИЛИ 5О соединены соответст058венно с первым входом элемента И 54 и с первым выходом статического регистра 47, . Выход и второй вход элемента ИСКЛЮгЧАЮЩЕЕ ИЛИ 51 соединены соответственно с первым входом элемента И 55 .и с вторым выходом статического регистра 47 Выход и первый и второй входы Ьлеменга ИЛИ 56 соединены соответсгвей- д шиной 62 блока 11 знака и соответственно с элементами И 54 и И 55. Выход и первый и второй входы элемента ИЛИ 57 соединены соответственно с шиной 63 блока 11 знака и соответст , элементами И 52 и 53. Выход и второй вход элемента ИС-. КЛЮЧАЮШЕЕ ИЛИ 48 соединены соответственно с первым входом И 52 и с третьим выходе статического регистра 47. Выход и второй вход элемента ИСКЛЮЧАЮШЕЕ ИЛИ 49 соединены соответственно с первым входом И 53 и чет вертым выходом статического ретасфа-47. Вторые входы элементов И 53 и И 55 соединены с прямым выходом триггера 43, инверсный выход которого соединен вторыми входами элементов И 52 и {,j 54 (фиг. 2). Интегро-дифференциальный вычислитель. для каждого i - оГийкла отрабатывает рекуррентное соотношение .-нВУ.,ч.БХ: - значения выходной вегде ,| и - значе 2 шагах вычисличины на 1, i -1 и i лений;. Х и Х.-значения входной величины на 1 и i-1 шагах вычислений; А, В, С и D- постоянные коэффициенты, значения которых зависят от шага по независимой переменной и вида реализуемого интегро-дифференциального пре- образования. Настройка интегро-даффершииального вычислителя осуществляется заданием постоянных коэффициентов А, В, С и D и начальных условий ( -л Предварительный расчет постоянных коэффициентов А, В, С и D Для часто реализуемых видов интегро-дифференцйальных преобразований выполняют по фopvIyлaм, приведенным в таблице, где К - коэффициент-усиления Т, Т, 3 Т4 - постоянные коэффициенты, 7п - viar последовательного преобразования вХоДной величины X в выходную У выбираемый кз условий заданной точности и вычислительной эффектиисости устройства. Интег1:к)-диф})еренциапьный вычислитель оперирует с лвричными переменными, для которых соотношение (1) принимает вий V HH ij-/ M i, J их; 2- переменные j разв4личинУ и соответственно; 1 I и Xj двоичные переменные j величин Х соответстИнтегро-дифференциальный вычислитель по рекуррентному соотношению (1) работает следующим образом. Регистр 1 сдвига содержит п -1 разряд ri дополняется элементом 30 задержки до п разрядов. В регистр 1 по шине 35 записывают в прямом или дополнитель ном коде, если Vi . О, последовательный -разрядный двоичный код начального условия V. в регистры 2 и 3 сдвига содержащие по 2п-1 разряд каждый, записывают по шинам 36 и 37 последовательные п -1разрядные двоичные коды абсолютных значений начальных условий1Ч.2 I соответственно. I. В регистр 4 и 5 сдвига, содержащие по 2 Г) разр$шов каждый, записывают по шинам 38 и 39 последовательные П-раз рядные двоичные коды коэффициентов А, Б и C,D соответственно. . Знаки коэффициентов А, В, С и D записываются по шине 6О в четырехразрядный регистр 47 блока 11 знака (фиг. 2) Знака начальных условий и запи сываются по шине 59. в двухраарядный регистр 46 блока 11 знака .- Знак начального условия К записывается по шине 58 в первый разряд двухразрядного регистра 45 блока 11 знака. Генератор 4О тактовых сигналов (фиг.2 блока 12 синхронизации вырабатывает на его шестс л выходе последовательность импупьсов частоты f которая поступает на входь синхронизации регистров 1-5 сдвига, а также делится делителем 41 в ti раз и затем задерживается элементом 42 задержки на один период тактовой частоты. Последовательность импульсов частоты f fn, на выходе делителя 41 (второй выход блока 12 синхровизации задает п -е такты работы устройства, а последовательность импульсов на выходе элемента 42 задержки (пятый выход блока 12 синхронизации синхронизирует Первые такты работы устройства с периодом nff. . Триггер 43 со счетным входом выполняет деление на два частоты ш 1Ходной последовательности импульсов элемента 42 задержки, форми{уя последователь- ность импульсов частотыf/2n на третьем выходе блока 12 синхронизации. Эта последовательность импульсов делится делителем 44 в п -1 раз, на выходе которого (четвертый выход блока 12 син)фонизании) формируется последовательность импульсов частоты /2п (п-1), период следования которой определяет время вычисления на одном шаге. В исходном состоянии триггеры 13-16 находятся в нулевом состоянии. Вычисления начинаются поспе установни триггера 14 в ешничное состояние импульсом четвертого выхода блока 12 синхронизации. Сигнал прямого выхода триггера 14 открывает элементы И 19 и 20, а сигнал его инверсного выхода закрывает элементы И 17, 18, 21 и 22. Двоичный код начального уеловия У- начиная с младшего разряда, сдвигается из регистра 1 через элемент ЗО задержки на один такт, блок 8 формирования дополнительного кода, элементы И 19 и ИЛИ 28 в регистр 2, в котором в это время двоичный код начального условия сдвигается из старших разрядов в п-1 младшие разряды. Блок 8 формирования дополнительного кода управляется сигналом второго выхода блока 11 знака так, что прямой либо дополнительный код пропускается в прямой код. Таким образом, в п старшие разряды регистра 2 записывается двоич-. ный код абсолютной величины начального условия 1У I , Сигаал младшего разряда величины I с выхода элемента ИЛИ 28 поступает на первый вход элемента И 24, на второй вход которого поступает импульс пятого выхода блока 12 синхронизации. В i случае единичного сигнала младшего разраз эяда велйчинь1|У| И®ментИ 24сраба-; тывает и импульс пятого выхода блока 12 синхронизации устанавливает триггер 15 в единичное состояние. По шине 32 поступают последователь но, начиная с мла;шего разряда, сиЬнаЛЫ двоичного кода абсолютного значения входной которые через элементы И 2О и ИЛИ 29 записываются в п 13i0 старших разрядов рег истра 3, В регистре 3 в это время двоичный код начального условия |Xi I сдвигается из старших раз рядов в h -1 младшие разряды. Сигнал знака входной величины X,- записывается по шине 31 в первый разряд регистpk 45 сдвига блока 11 знака по импульсу четвертого выхода блока 12 синхронизации, который осуществляет сдвиг знака начального условия величины Х, из первого разряда регистра 45 во второй разряд. Сигнал младшего разряда величины с выхода элемента ИЛИ 29 поступает на первьгй вход элемента И 26. fi случае единичного сигнала младшего разряда величины элемент И 26 срабатывает по импульсу пятого выхода блока 12 син хронизации и триггер 16 устанавиивается в единичное.состояние, Триггеры 15 и 16 в единичном состо янии открывают элементы И , 25 со ответственно, через которые с выходов регистров 4 и 5 последовательно,начина С младших разрядов, -сдвигаются двоичны коды коэффициентов А и .С соответственн Коэффициент А поступает через блок 9формирования дополнительного кода на первый вход сумматора 7 в прямом или . дополнительном коде в зависимости от знака произведения AV.| сигнал которо го действует на втором выходе блока 11 знака. Сигнал знака величиныЛУ;. форми- руется элементом ИСКЛЮЧАЮШЕЕ ИЛИ 50, на входы которого поступают сигналы выходов первых разрядов регистров 46 и 47,- где хранятся знаки величин и А соответственно. Сигнал знака величиныЛ 1 с выхода элемента ИСКЛЮ ЧАЮЩЕЕ ИЛИ 5О поступает через элементы И 54 ИЛИ 56 на шину 62 второ-г го выхода блока 11 знака. S. Коэффициент С поступает через бяок 10формирования дополнительного кода на второй вход сумматора 7 в прямом или дополнительном коде в зависимости от знака произведения С Х сигнал ког торого формируется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 48,.на входы которого поступает сигнал знака величины Х .выхода первого разряда регистра 45 и сигнал знака коэффициента С с выхода третьего разряда регистра 47 блока 11 знака. Сигнал знака величины СХ с BI хода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 48 через элемент И 52, открытый сигналом инве1юного выхода триггера 43, и эле0514мент ИЛИ 57 поступает на третий выход блока 11 знака. Таким образом, на входы последова-. тельного одноразрядного двоичного сумматора 7 поступают в прямом или дополнительном коде последовательно во времени, начиная с младшего разряда, дво ичные кодь коэффициентов А и С, алгебраическая сумма которых поступает на второй вход последовательного двоичного сумматора 6. В это время на первом входе сумматора 6 действует сигнал логического нуля, так как элементы И 17 и 18 закрыты сигналом инверсного-выхода триггера 14. Алгебраическая сумма коэффициента А и С с выхода одноразрядного последовательного сумматора 6 записывается, начиная с младшего разряда, в регистр 1. Спустя п тактов после установки триггера 14 в единичное состояние,триггеры 14-16 сбрасываются в нулевое состояние лмпульсом второго выхода блока 12 синхронизации. Триггер 14 в нулевом состоянии закрывают элементы И 19 и 20 сигналом прямого .выхода и открывает элементы И 17, 18, 21 и 22 сигналом инверсного выхода. Элементы И 21к 22 подключают выходы регистров 2 и 3 к их входам соответственно. Цепи циркуляции кодов в регистрах сдвига 2 и 3 замыкаются через элементы И 21 н 22соответственно. Элемент И 18, открытый сигналами инверсных выходов триггеров 13 и 14, подключает выход регистра 1 через элемент ЗО задержки к перъому входу сумматора 6, что обеспечивает в течение следующих it. тактов поступление на первый вход сумматора 6 двоичного кода алгебраической суммы коэффициентов А-Ю., В следующем такте после возврата триггера 14 в нулевое состояние с выходов регистров 2 и 3 сдвигаются младщие разряды величин1.2 I и) I соответственно. В случае единичных кодов в младших разрядах величин IY.JI, 2 и 1Х Ц|элементы. И 24 и 26 срабатывают по импульсу пятого выхода блока 12 синхронизации, что приводит к установке триггеров 15 и 16 соответственно в единичное состояние. Сигналь прямых выходов триггеров 15 и 16 открывают соответственно элементы И 23 и25, через которые с выходов регистров 4 и 5 сдвигаются двоичные коды ко94Фе1шентов В н 13 соответственно. Двоичные коды коэффициентов В и1) преоб15100разуются соогветствукяцими блоками фор« мированиб дополнительного кода 9 и 1О и поступают последовательно начиная с младшего разряда, в прямом или дополнительном коде на входы сумматора 7. Управление преобразованием блоками формирования дополнительного кода 9 и 10 осуществляется по сигналам второго и третьего выходов блока 11 знака соответственно. Сигнал знака произведения BY,O формируется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 51, на входы которого поступают выходы BTOf&ix разрядов регистров 46 и 47 блока 11 знака, где хранятся знаки величин В соответственно. С выхода элемента ИСКЛЮЧАЮЩЕЕ И ЛИ. 51 сигнал знака величины через элементы И 55, ИЛИ 56 поступают на шину 62 второго выхода бло ка 11 знака. Сигнал знака произведенияВХ - формируется элементсы ИСКЛЮЧАЮЩЕЕ ИЛИ 49 по сигналам выходов второго и четвертого разрядов регистров 45 и 47 блока 11 знака. С выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 49 знак произведения 1)Х- считывается через элементы И 53, ИЛИ 57 на шину 63 третьего выхода бло ка 11 знака. Прямой или дополнительный код алгебраической суммы коэффициентов Ви.3D с выхода сумматора 7 поступает на второй вход сумматора 6, на первый вход которого с выхода регистра 1 через элемент 30 задержк}, элемент И 18 и ИЛИ 27 сдвигается двоичный код алгебраической суммы коэффициентов А и С. С выхода сумматора 6 двоичный код алгебраической суммы коэффициентов А, В, С и D записывается в регистр 1. Таким образом, за 2 п тактов после начала вычислений в регистре 1 накапливается алгебраическая сумма коэффициентов А, В, С и D после чего триггер 13 устанавливается в единичное состояние импульсом третьего выхода блока 12 синхронизации. Триггер 13 в единичном состоянии открывает сигналом прямого выхода элемент И 17 и блокирует элемент И 18 сигналом инверсного выхода. Элемент И 17 подключает выход регистра 1 к первому входу сумматора 6 к мо менту сдвига с выхода регистра 1 второ го разряда алгебраической суммы коэффи циентов А, В, С иВ В это время с выходов регистров 2 и 3 сдвигаются вторые разряды величин 1У.-. 1 и, соответственно. В случае един« чн у Х кодов 0516. во вторых разрядах величин(У | и С срабатывают элементы И 24 в 26, выходные сигналы которых устанавливают триггеры 15 и 16 в единичное состояние. Двоичные коды произведения коэффициентов А и С на двоичные переменные вторых разрядов величин IY. I и|Х( соответственно преобразуются в прямой или дополнительный код блоками 9 и 1-О соответственно, а затем суммируются сумматором 7, сигнал суммы которого суммируется сумматором 6 с двоичным кодом алгебраической суммы коэффициентов А, В, С и D сдвигаемой с выхода регистра 1, начиная с второго разряда. Следовательно, установка триггера 13 в единичное Состояние приводит к сдвигу на один разряд накопленной суммы коэффициентов в регистре 1, обеспечивая этим выполнение операций умножения на два. Спустя п тактов после установки триггера -13 в единичное состояние сигнал второго выхода блока 12 синхронизации возвращает триггер 13 в нулевое состояние, в котором обеспечивается подключение элементом И 18 выхода регистра 1 через элемент ЗО задержки на такт к первому входу сумматора 7. В это время на второй вход сумматора 6 с выхода сумматора 7 поступает двоичный код алгебраической, суммы произведения коэффициентов В и D на двоичные пере- менные вторых разрядов величин иХ соответственно, которая формируется таким же образам, как в предыдущие h тактов формировалась алгебраическая сумма произведения, коэффициентов Аи С на двоичные переменные вторых разрядов величин|V I соответственно. Сумматор 6 суммирует накопленную сумму коэффициентов в регистре 1 с алгебраической суммой произведения коэффициентов В и 33 на двоичные переменные вторых разрядов величин 1У ) и |Х соответственно и результат суммирования записывается в регистр 1. Дальнейшие вычислении в интегродифференциальном вычислителе выполняются аналогичным образом. Каждые 2п такта в кольцевых регистрах 2 и 3, содержащих 2п-1 разряд, происходит сдвиг выходных сигналов относительно выходных сигналов блока 12 синхронизации, что приводит к совпадению на входах элементов И 24 и 26 с импульсом пятого выхода блока 12 синхронизации следую- щих разрядов величин , IXil 10 fX.,| a переключениетриггером ГЗ цепа кодов регистра 1 с И разрядов (с выхода элемента 30 задержки) на n.-l разряд (с выхода регистра 1) обеспечивает савчт ннформапЕИ в регнстре 1 ва один разряд относительно выходных сигналов блока 12 синхронизации. Спустя 2n(lT-l) такт после начала вычиЬ еанй в регистре 1 накапливается ,в прямом юга дополйительном коде старших разрядов выходной .У знаковый |Г1 чВ разряд которой с выхода сумматора 6 поступает на второй вход блока 11 знаки (шина 61) и Jcдвигaeтcя по сигналу, действующему на 66 блока 12 синхронизации, в первый разряд регистра 46 сдвига, из первого разряда которого в это время во второй разряд сдвигается знак величины К мсменту начала вычислений на вто- ром шаге в -1 старших разрядах регистров 2 и 3 содержатся двоичные коды величий соответственно, Вы ЧЯслеАй на втором шаге и Всех последу1сших шагах выполняются аналогичным об.разом, но с новых начальных условий, ; которые формируются )матически на предыдущем шаге вычислений. Технико-экономические преимушестеа предлагаемого интегро-дифференциального вычислителя заключаются .в расширении его функциональных возможностей, так как предлагаемый интегро-дифференциаАь05ный вычислитель позволяет вьшолнятъ интегро-дифференпиальные преобразования как первого, гак и второго порядка за висимости от выбора А, В, С и В параметров и настр Лки интегро-дйфференциального вычислителя. Прототип предложенного интегро-дифференоиальвого didчислвтеля выполняет только интегро-двфференциальные преобразования первого порядка. Предложенный ннтегро-днфференциаль)1ый вычислитель можно использовать и для линейных интегро-дифференоиальных преобразований любого порядка, для чего необходимо представить это феобразова-. ниеЪ виде провз юдени элементарных пе редаточных функшй согласно табпиш, рассчитать их параметры и начальные условия и соединить последовательно ряд одинаковых ивтегро-дифференциальных вы- числителей. В этом случае выходные шины 33 я 34 каждого предыдущего иитегро-дифференциального 1№гчислителя подключаются соответственно к входным шинам 31 и 32 последукпиего интегро-дифференциального вычислителя. Причем син:14}онизация работы всего ряда из нескольких одинаковых интегро-дифференциальных вычислителей, .реализующих каждый свою передаточную функцию осуществляется от одного и того же блока 12 синхронизации и в этом случае не требу ется дополнительных затрат оборудования.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Вычислительная техника | |||

| Справочник под ред | |||

| Г | |||

| Д | |||

| Хаски и Г | |||

| А | |||

| Корна | |||

| Т | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| С | |||

| Цифровые диффере нциал ьвые анализа торы | |||

| М,, М ашиностроение, 1968, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1921 |

|

SU84A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1983-03-23—Публикация

1981-04-17—Подача