гз

Изобретение относится т; вьгпгсли- тельной технике и может быть использовано в качестве буферного запог ш- нающего устройства для систем сбора и q6pa6oTKM информации ,.,

Цель иэобретен1-1я - гшвыиение надежности буферного яапоошнакмтего устрОЙСТВЗо

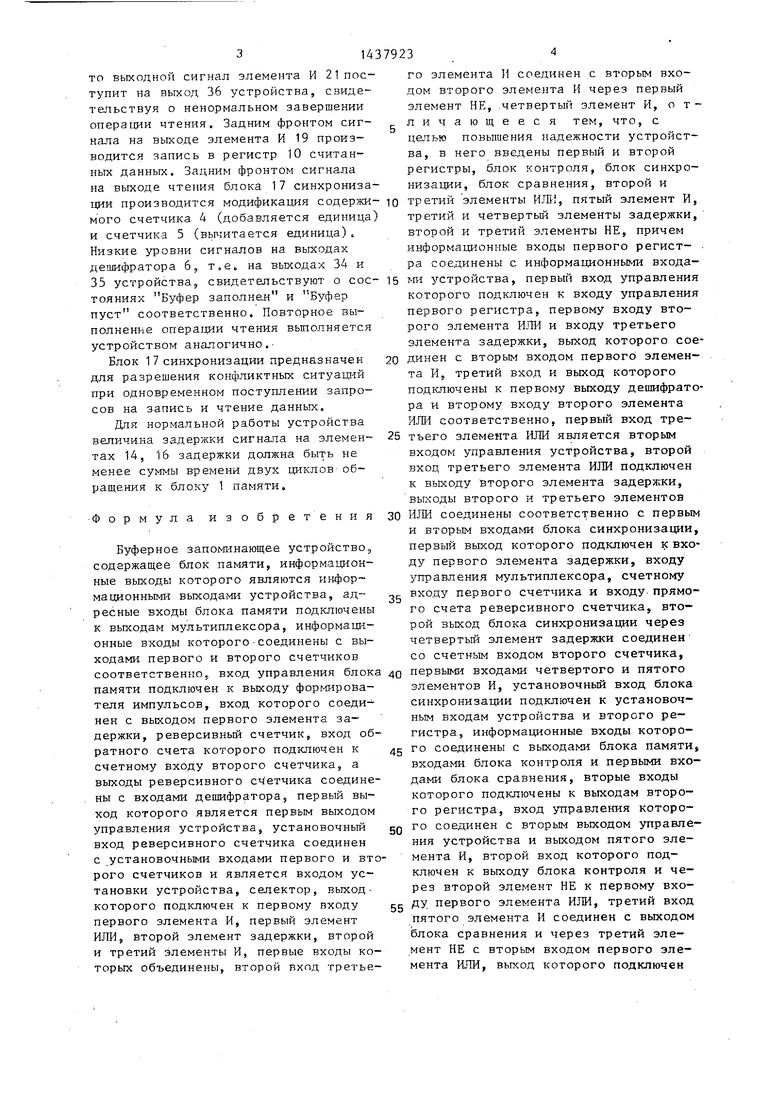

На чертеже привгдЕ}:а структурная схема предложеикого устройстза,

УстройстБО содерж гг олок t iss.,,,i-- ти. мультиплексор 2,. счетчики 3 и 4, реверсивный счетч гк 5, ;iei ; ffipa rop о, селектор 7 фор жровй агь 8 импуль- coBj регистры 9 и 10,, блок i1 сравня ния, блок 12 контроля элементы 3--1о задержки, блок 17 синхронизации,, зле-- менты И 18-22, элементы ИЛИ 23-255 элементы НЕ 26-28 j информационные вхо ды 29 и выходы 30, входы 3is32 управления, выходы 33-36 у.;равдеь г:я, BXOJ 37 установки.

Селектор 7 ксткет , ь:лпо.; чь -: ;:. виде последоват 2лько соед:п1е1-;.ньгк да- шифратора к элемента FJIH яли постоя; ного запо1.1инающего ycTpoftc Ba.. Б ка-- честве блока 12 :.10г тролл .юлсаг использован сумматор по : одулю дБа„

Устройство работает следуюищк об- разом.

Перед началом работы сигналом по входу 37 установки счетчики 3, 4 и 5 регистр 10 и блок Г/ синхроггазат.тяк устанавливаются в изглейоз состояний

При выполнении операции записи за писываемые данные поступают иа входы 29 устройства в сопровождении сигнала сопровойздения по входу 3 ; устрой-- ства, который осуществляет запись дан ных в регистр 9s Одкозремекпо с этим сигнал по входу 31 через элемент ИЛИ 23 и блок 17 сннхронизащ-vH поступает на вход )7 мультиплексора 2, которьш подключает к адресным входам блока 1 памяти вьшодь счетчио .1

ка Jj который является формироватаче текущего адреса записи даиь ых в блок 1 памяти в Сигнал с выхода блока 17 синхронизацииJ нроходй через элемент 13 задержки, поступаи;т на вкод формк рователя 8j БЬСШДНОЙ сг-м нал которого осуществляет запись данньж з блок 1 памяти Задним Фронтом сигнала-на вы ходе блока 17 си- хронизадйи произвс- дится модификация содерияного счетчк ков 3 и 5j т.е. к их содер лшыому до-- бавляется единица. Сигнал сопровож-- дения по входу 31„ задержанный на

элег -генте 14 задержки, опрашивает элемент И 18j. на выходе которого появляется сигнал при наличии состояний Буфер не заполнен и Дублирование Склевал Дублирование формируется селектором 7, на вход которого поступает адресный признак информагщонно- го канала, данные которого должны быть записаны в блок 1 памяти дважды ПС- последовательно возрастающим адресам,. Вторая запись производится при условии наличия свободной ячейки в блоке 1 памяти. Работа устройства пр этом аналогична описанному.

При обработке запроса на чтение данных:,, поступающего по входу 32 уп- равх;ения устройства, устройство работает следующим образом.

Сигнал по входу 32, проходя через элемент ИЛИ,24,, блок 17 синхронизаци и элемент 15 задержки, опрашивает эле г.; ент И 19 о Низкий уровень сигнала, прчсутствуюпЦ Ш на входе управления Ь5у,иьтиплексора 2, подключает к адресным входам блока 1 памяти выходы счетчика 4j к-оторый является формирова- гелем текущего адреса чтения,, Произ- води:тся чтение данных из блока 1 памяти о Считанные данные из блока 1 памяти контролируются на правильность блоком 12 контроля. Блок 11 сравнения сравнивает считанные данные с данными, считанньп-ш в предьиущем цикле чтения и хранящимися в регистре 10„ На выходе элемента И 19, т.е. ка. выходе 33 устройства, появляется сигнал,, который является сигналом сопровождения данных на выходах 30 З- стройства в том случае, если блок 12 контроля не обнаружит ошибки в считанных данных и эти данные будут отличаться от данных, считанных в предьщущем цршле чтения. Если же одно КЗ этих условий не выполняется, , на выходе одного из элементов НЕ 26s 275 Э- следовательно, и на выходе элемента РШИ 25 присутствует высокий уровень сигнала, то выходной сигнал элемента И 20 опрашивает эле- гчвиты И 21е22„ При наличии состояния Буфер пуст ка выходе элемента И 22 появится сигнал, поступающий через элемент 16 задержки на вход элемента ИЖ 24 как повторный запрос на чтение данных из блока 1 памяти. Если же при этом на выходе элемента НЕ 23 высокий - тэовень сигнала, т.е. имеет место состояние Буфер пуст,

3143

то выходной сигнал элемента И 21 поступит на выход 36 устройства, свидетельствуя о ненормальном завершении операции чтения. Задним фронтом сигнала на выходе элемента И 19 производится запись в регистр 10 считанных данных. Задним фронтом сигнала на выходе чтения блока 17 синхрониза

го элемента И соединен с вторым входом второго элемента Н через первый элемент НЕ, .четвертый элемент И, о т - ли чающееся тем, что, с целью повышения надежности устройства, в него введены первый и второй регистры, блок контроля, блок синхронизации, блок сравнения, второй и

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1396158A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Динамическое оперативное запоминающее устройство | 1981 |

|

SU1003142A1 |

| Устройство для сортировки информации | 1987 |

|

SU1478210A1 |

| Устройство для задания тестовых воздействий | 1988 |

|

SU1541614A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287237A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1647579A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве буферного запоминающего устройства для систем сбора и обработки информации. Цель изобретения повышение надежности буферного запоминающего устройства. Устройство содержит блок 1 памяти, мультиплексор 2, счетчики. 3 и 4, ревер- сивньш счетчик 5, дешифратор 6, селектор 7, формироватапь 8 импульсов, регистры 9 и 10, блок 11 сравнения, блок 12 контроля, элементы 13-16 задержки, блок 17 синхронизации, элементы И 18-22, элементы ИЛИ 23-25, эпементы НЕ 26-28. 1 ил.

20

ции производится модификация содержи- ю третий элементы НЛП, пятый элемент И, мого счетчика 4 (добавляется единица) и счетчика 5 (вьгчитается единица) , Низкие уровни сигналов на выходах дешифратора 6, т.е. на выходах 34 и 35 устройства, свидетельствуют о состояниях Буфер заполнен и Буфер пуст соответственно. Повторное выполнение операц 1и чтения выполняется устройством аналогично.Блок 1 7 синхронизации предназначен для разрешения конфликтных ситуаций при одновременном поступлении запросов на запись и чтение данных.

Для нормальной работы устройства величина задержки сигнала на элемен- ,тах 14, 16 задержки должна быть не менее суммы времени двух циклов обращения к блоку 1 памяти,

Формула изобретения

Буферное запоминающее устройство, содержащее блок памяти, информационные выходы которого являются информационными выходами устройства, адресные входы блока памяти подключены к выходам мультиплексора, информационные входы которого - соединены с выходами первого и второго счетчиков

третий и четвертый элементы задержки, второй и третий элементы НЕ, причем информационные входы первого регист- ра соединены с информационными входа-

15 ми устройства, первый вход управления которого подключен к входу управления первого регистра, первому входу второго элемента ИЛИ и входу третьего элемента задержки, выход которого соединен с вторым входом первого элемента И, третий вход и выход которого подключены к первому выходу дешифратора и второму входу второго элемента ИЛИ соответственно, первый вход третьего элемента ИЛИ является вторым входом управления устройства, второй вход третьего элемента ИЛИ подключен к выходу второго элемента задержки, выходы второго и третьего элементов

30 ИЛИ соединены соответственно с первым и вторьм вxoдa и блока синхронизации, первьш выход которого подключен к входу первого элемента задержки, входу управления мультиплексора, счетному входу первого счетчика и входу, прямого счета реверсивного счетчика, второй выход блока синхронизации через четвертый элемент задержки соединен со счетным входом второго счетчика.

25

35

соответственно5 вход управления блока 40 первыми входами четвертого и пятого памяти подключен к выходу формирова- элементов И, установочный вход блока

синхронизации подключен к установочным входам устройства и второго ретеля импульсов, вход которого соединен с выходом первого элемента задержки, реверсивный счетчик, вход обратного счета которого подключен к счетному входу второго счетчика, а выходы реверсивного сч етчика соединены с входами дешифратора, первый выход которого является первым выходом управления устройства, установочный вход реверсивного счетчика соединен с установочными входами первого и второго счетчиков и является входом установки устройства, селектор, выход- которого подключен к первому входу первого элемента И, первый элемент ИЛИ, второй элемент задержки, второй и третий элементы И, первые входы которых объединены, второй вход третьегистра, информационные входы которо- {g го соединены с выходами блока памяти, вxoдa ш блока контроля и первыми входами блока сравнения, вторые входы которого подключены к выходам второго регистра, вход управления которо- 5Q го соединен с вторым выходом управления устройства и выходом пятого элемента И, второй вход которого подключен к выходу блока контроля и через второй элемент НЕ к первому вхо- сс ДУ первого элемента ИЛИ, третий вход пятого элемента И соединен с выходом блока сравнения и через третий элемент НЕ с вторым входом первого элемента ИЛИ, выход которого подключен

третий элементы НЛП, пятый элемент И,

третий и четвертый элементы задержки, второй и третий элементы НЕ, причем информационные входы первого регист- . ра соединены с информационными входа-

ми устройства, первый вход управления которого подключен к входу управления первого регистра, первому входу второго элемента ИЛИ и входу третьего элемента задержки, выход которого соединен с вторым входом первого элемента И, третий вход и выход которого подключены к первому выходу дешифратора и второму входу второго элемента ИЛИ соответственно, первый вход третьего элемента ИЛИ является вторым входом управления устройства, второй вход третьего элемента ИЛИ подключен к выходу второго элемента задержки, выходы второго и третьего элементов

ИЛИ соединены соответственно с первым и вторьм вxoдa и блока синхронизации, первьш выход которого подключен к входу первого элемента задержки, входу управления мультиплексора, счетному входу первого счетчика и входу, прямого счета реверсивного счетчика, второй выход блока синхронизации через четвертый элемент задержки соединен со счетным входом второго счетчика.

гистра, информационные входы которо- го соединены с выходами блока памяти, вxoдa ш блока контроля и первыми входами блока сравнения, вторые входы которого подключены к выходам второго регистра, вход управления которо- го соединен с вторым выходом управления устройства и выходом пятого элемента И, второй вход которого подключен к выходу блока контроля и через второй элемент НЕ к первому вхо- ДУ первого элемента ИЛИ, третий вход пятого элемента И соединен с выходом блока сравнения и через третий элемент НЕ с вторым входом первого элемента ИЛИ, выход которого подключен

514379236

к второму входу четвертого элементавторого элемента И являются четверИ, выход которого соединен с первым w выходом управления устройства,

входом второго элемента И, выход вто-информационные входы блока памяти

рого элемента И подключен к входусоединены с выходами первой и второй

второго элемента задержки,,а выходгрупп первого регистра, выходы втотретьего элемента И является третьимрой группы которого соединены с вховыходом управления устройства, вто-дами селектора, рой выход дешифратора и второй вход

| Буферное запоминающее устройство | 1985 |

|

SU1251181A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1298757A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-15—Публикация

1987-01-12—Подача