8ы)(оЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Функциональный преобразователь | 1983 |

|

SU1107131A1 |

| Устройство для выбора частотных диапазонов передачи группового радиосигнала | 1982 |

|

SU1072277A1 |

| Устройство для вычисления логарифмической функции | 1988 |

|

SU1596323A1 |

| Цифровой функциональный преобразователь двух переменных | 1982 |

|

SU1115052A1 |

| Устройство для нахождения экстремумов | 1985 |

|

SU1287180A1 |

| Устройство для вычисления функции @ | 1985 |

|

SU1305671A1 |

| Устройство для вычисления параметров экспоненциальных функций | 1980 |

|

SU911524A1 |

| Синусно-косинусный функциональный преобразователь | 1980 |

|

SU888111A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1976 |

|

SU593212A1 |

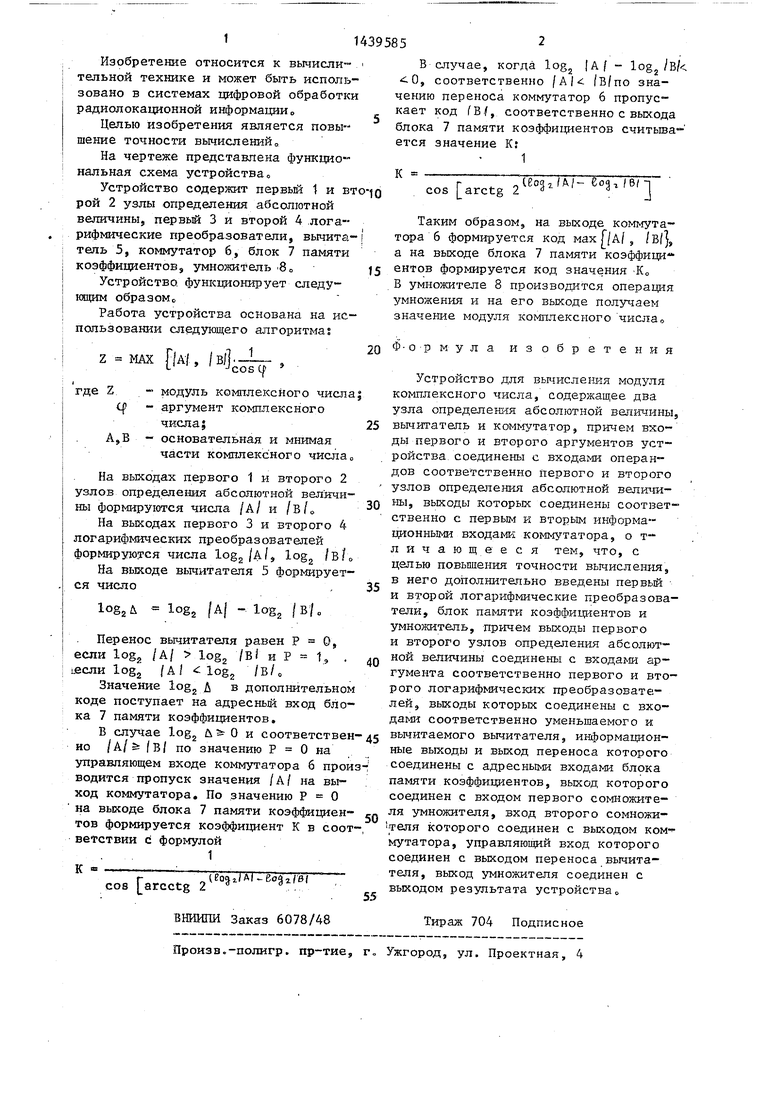

Изобретение откосится к области вычислительной техники и может быть использовано в системах цифровой обработки радиолокационной информадии. Целью изобретения является повышение точности вычислега ЕЯ, Устройство содержит первьй 1 и второй 2 узлы определения абсолютной величины, первьй 3 и второй 4 логарифмические преобразователи, вычитатель 5, коммутатор 6, блок 7 ламяти коэффидиентов, умножитель 8 о 1 ил о

СО СО СД

00 ел

Изобретение относится к вычисли- тельной технике и может быть использовано в системах цифровой обработки радиолокационной информации

Целью изобретения является повышение точности вычисленийо

На чертеже представлена функцио- нальная схема устройствао

Устройство содержит первьй t и вт рой 2 узлы определения абсолютной величины, первьй 3 и второй 4 .логарифмические преобразователи, вычитатель 5, коммутатор 6, блок 7 памяти коэффициентов, умножитель 8о

Устройства функционирует следу- нщим образомо

Работа устройства основана на использовании следующего алгоритмаS

Z МАХ

Г|А-|, /В/

1

cos С|

где Z. - модуль комплексного числа; ср - аргумент комплексного

числа; А,В - основательная, и мнимая

части комплексного числа

На выходах первого 1 и второго 2 узлов определения абсолютной величи- ны формируются числа /А/ и /В/о

На выходах первого 3 и второго 4 логарифмических преобразователей формируются числа logg /А/, logj /В/о

На выходе вычитателя 5 формируется число

« log,, |А| - logg /В/о Перенос вычитателя равен Р О,

если logj,

;ВСЛИ lOgg

/А/ log /Bi и Р 1, /А| - log /В/,

Устройство для вычисления модуля комплексного числа, содержащее два узла определения абсолютной величины

25 вычнтатель и коммутатор, причем входы первого и второго аргументов устройства, соединены с входами операндов соответственно первого и второго узлов определения абсолютной велшда30 м, выходы которых соединены соответ- ственно с первым и вторым информационными входами коммутатора, о т- личающееся тем, что, с целью повышения точности вычисления, в него дополнительно введены первьй и второй логарифмические преобразователи, блок памяти коэффициентов и умножитель, причем выходы первого и второго узлов определения абсолютной величины соединены с входами аргумента соответственно первого и второго логарифмических преобразователей, выходы которых соединены с входами соответственно уменьшаемого и

35

40

Значение log Д в дополнительном коде поступает на адресньй вход блока 7 памяти коэффициентов.

В случае log Л& О и соответствен-45 вычитаемого вычитателя, информационные выходы и .выход переноса которого соединены с адресными входами блока водится пропуск значения /А/ на выход коммутатора. По значению F О

но /А/& /В/ по значению Р О на управляющем входе коммутатора б произпамяти коэффициентов, выход которого соединен с входом первого сомножите

j |5

4395852

В случае, когда log f А f - iO, соответственно /А| /В/по значению переноса коммутатор 6 пропускает код fB.f, соответственно с выхода блока 7 памяти коэффициентов считьша- ется значение Кг

1 К

cos

arctg

г/А/- eog-i /В/

Таким образом, на выходе коммутатора 6 формируется код мах Г/А/, /В/, а на выходе блока 7 памяти коэффици ентов формируется код значения Ко В умножителе 8 производится операция умножения и на его выходе значение модуля комплексного числао

Ф-ормула изобретения

Устройство для вычисления модуля комплексного числа, содержащее два узла определения абсолютной величины,

вычнтатель и коммутатор, причем входы первого и второго аргументов устройства, соединены с входами операндов соответственно первого и второго узлов определения абсолютной велшда м, выходы которых соединены соответ- ственно с первым и вторым информационными входами коммутатора, о т- личающееся тем, что, с целью повышения точности вычисления, в него дополнительно введены первьй и второй логарифмические преобразователи, блок памяти коэффициентов и умножитель, причем выходы первого и второго узлов определения абсолютной величины соединены с входами аргумента соответственно первого и второго логарифмических преобразователей, выходы которых соединены с входами соответственно уменьшаемого и

вычитаемого вычитателя, информационные выходы и .выход переноса которого соединены с адресными входами блока

памяти коэффициентов, выход которого соединен с входом первого сомножите

| Устройство для вычисления функции @ | 1984 |

|

SU1166102A1 |

Авторы

Даты

1988-11-23—Публикация

1987-05-28—Подача