4 4iik 4 Ч СЛ

Изобретение относится к вычислительной технике и может быть использовано при разработке устройств обработки цифровой информации, осущест вляющих обработку массивов чисел.

Цель изобретения - упрощение конструкции устройства.

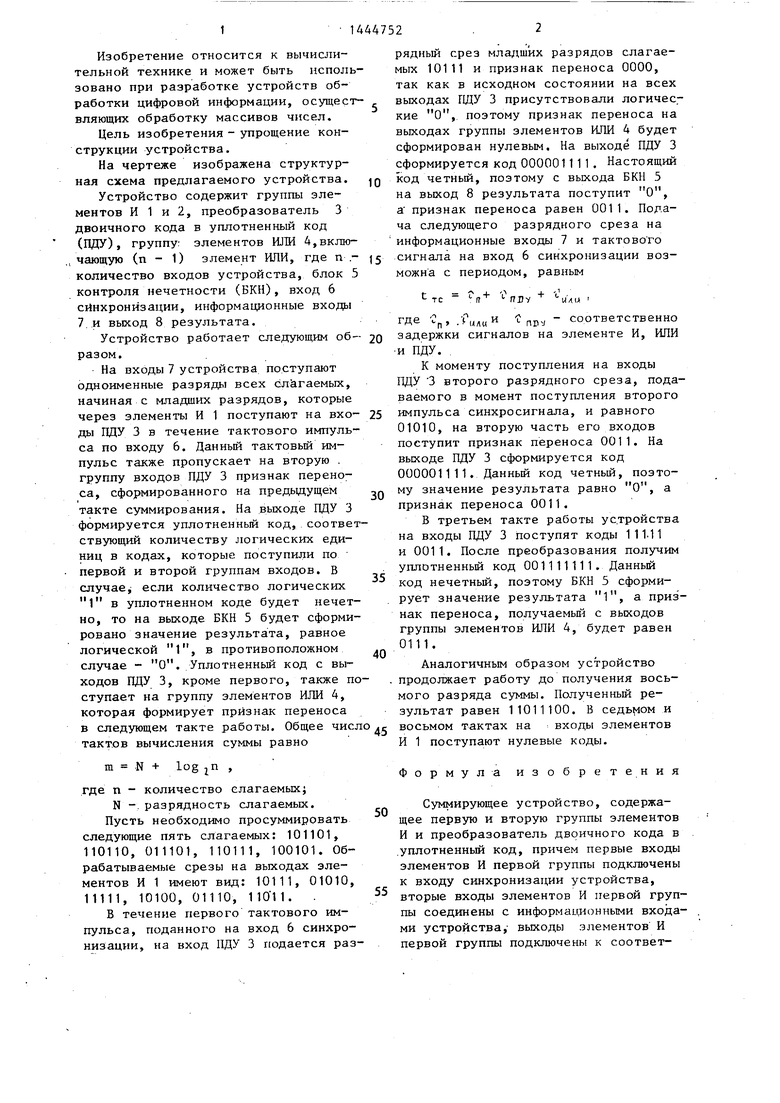

На чертеже изображена структурная схема предлагаемого устройства.

Устройство содержит группы элементов И 1 и 2, преобразователь 3 двоичного кода в уплотненный код (ПДУ), группу: элементов ШШ 4,включающую (п - 1) элемент ИЛИ, где п .- количество входов устройства, блок 5 контроля нечетности (БКН), вход 6 синхронизации, информационные входы 7.и выход 8 результата.

Устройство работает следующим об- разом.

На входы 7 устройства поступают одноименные разряды всех слс1гаемых, начиная с младших разрядов, которые через элементы И 1 поступают на вхо- ды ПДУ 3 в течение тактового импульса по входу 6. Данный тактовый импульс также пропускает на вторую . группу входов ПДУ 3 признак переноса, сформированного на предыдущем такте суммирования. На выходе ПДУ 3 формируется уплотненньй код, соответствующий количеству логических единиц в кодах, которые поступили по первой и второй группам входов. В случае если количество логических 1 в уплотненном коде будет нечетно, то на выходе БКН 5 будет сформировано значение результата, равное логической 1, в противоположном случае - О. Уплотненный код с выходов ПДУ 3, кроме первого, также поступает на группу элементов ИЛИ 4, которая формирует признак переноса в следующем такте работы. Общее числ тактов вычисления суммы равно

m N + log ,

где n - количество слагаемых; N -, разрядность слагаемых.

Пусть необходимо просуммировать следующие пять слагаемых: 101101, 110110, 011101, 110111, 100101. Обрабатываемые срезы на выходах элементов И 1 имеют вид: 10111, 01010, 11111, 10100, ото, IIO ll. .

В течение первого тактового импульса, поданного на вход 6 синхро- ниэ1ации, на вход ПДУ 3 подается разрядный срез младших разрядов слагаемых 10111 и признак переноса 0000, так как в исходном состоянии на всех выходах ГЩУ 3 присутствовали логические О, поэтому признак переноса на выходах группы элементов ИЛИ 4 будет сформирован нулевым. На выходе ПДУ 3 сформируется код 000001111. Настоящий код четный, поэтому с выхода БКН 5 на выход 8 результата поступит О, а признак переноса равен 0011. Подача следующего разрядного среза на информационные входы 7 и тактово го сигнала на вход 6 синхронизации возможна с периодом, равным

5

0

5 п Q с

5

0

5

- L + П В V

+ г

,1

где , .

fT ПВУ -U/tu

и L соответственно

задержки сигналов на элементе И, ИПИ и ПДУ.

К моменту поступления на входы ПДУ 3 второго разрядного среза, подаваемого в момент поступления второго импульса синхросигнала, и равного 01010, на вторую часть его входов поступит признак переноса 0011. На выходе ПДУ 3 сформируется код 000001111. Данный код четный, поэтому значение результата равно О, а признак переноса 0011.

В третьем такте работы устройства на входы ПДУ 3 Поступят коды 111.11 и 0011. После преобразования получим уплотненньй код 0011 11111. Данньй код нечетньй, поэтому БКН 5 сформирует значение результата 1, а приз - нак переноса, получаемьй с выходов группы элементов ИЛИ 4, будет равен 0111.

Аналогичным образом устройство продолжает работу до получения восьмого разряда суммы. Полученный результат равен 11011100. В седьмом и восьмом тактах на входы элементов И 1 поступают нулевые коды.

Формула изобретения

Суммирующее устройство, содержащее первую и вторую группы элементов И и преобразователь двоичного кода в .уплотненный код, причем первые входы элементов И первой группы подключены к входу синхронизации устройства, вторые входы элементов И первой группы соединены с информационными входами устройства,- выходы элементов И первой группы подключены к соответ 1444752

ствующим входам первой группы преоб- динены с вторыми входами элементов разователя двоичного кода .в уплот- ИЛИ группы, выходы которых подключе- ненный, отличающееся тем, ны к первым входам соответствукщих что, с целью упрощения конструкции, элементов И второй группы, вторые устройство содержит группу из п - 1 входы которых соединены с входе элементов ИЛИ, где п - количество ий- синхронизации устройства, выходы эле- формационных входов устройства, и ментов И второй группы подключены к

блок контроля нечетности, причем вы-. входам второй группы преобразователя ходы четных разрядов преобразователя ю двоичного кода в уплотненный код, двоичного кода в уплотненный код сое- выходы которого соединены с входами динены с первыми входами соответст- блока контроля нечетности, выход вующих элементов ИЛИ группы, а нечет- которого подключен к выходу резуль- ные выходы, начиная с третьего, сое- тата устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующее устройство | 1990 |

|

SU1714591A1 |

| Суммирующее устройство | 1986 |

|

SU1396139A1 |

| Ассоциативное арифметическое устройство | 1986 |

|

SU1363187A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Ассоциативное устройство для суммирования массива чисел | 1988 |

|

SU1564615A1 |

| Устройство для суммирования @ @ -разрядных двоичных чисел | 1984 |

|

SU1277095A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1994 |

|

RU2092891C1 |

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| Суммирующее устройство | 1987 |

|

SU1495784A1 |

| Устройство для суммирования N чисел | 1987 |

|

SU1462293A1 |

Изобретение относится к области вычислительной техники и может быть использовано при разработке устройств обработки цифровой информации, осуществляющих обработку массивов чисел. Целью изобретения является упро- .щение конструкции устройства. Доя достижения цели в устройство, содержащее две группы элементов И 1, 2 и преобразователь 3 двоичного кода в уплотненный код, введены дополнительно группа элементов ИЛИ 4 и блок 5 контроля нечетности. При этом цифра результата формируется на выходе блока контроля нечетности, а группа элементов ШШ формирует сдвинутый на один разряд код количества единиц для осуществления последовательного по разрядам параллельного по словам-метода суммирования. 1 ил. (Л с

| Справочник по цифровой вычислительной технике (ЭВМ и системы)/ Под ред | |||

| Б.Н.Малиновского | |||

| Киев: Техника, 1980, с | |||

| Разборное приспособление для накатки на рельсы сошедших с них колес подвижного состава | 1920 |

|

SU65A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Суммирующее устройство | 1986 |

|

SU1396139A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-07-01—Подача