g е

8

в в

7.-I

со

сю 05

00

;о

Изобретение относятся к вычисли- технике и может быть использовано при разработке быстродействующих устройств обработки цифровой информации.

Цель изобретения - упрощение устройства.

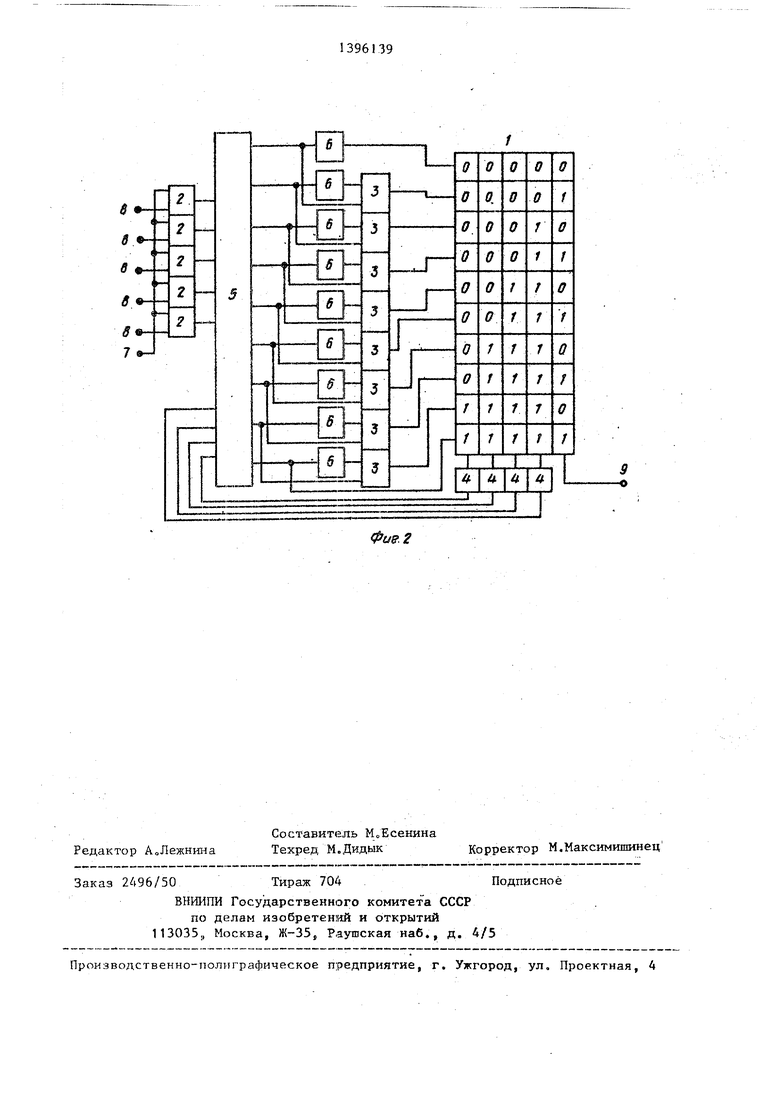

На фиГо представлена структурная схема суммирующего устройства; на фиг.2 - размещение информации в постоянном запоминающем блоке для слу чая обработки 5 операндов

Суммирующее устройство содержит постоянный запоминающий блок (ПЗБ,1 1 первую и вторую группы элементов И 2 и 3, группу элемйнтов А задержки, преобразователь 5 двоичного кода н уплотненный код (ПД7), группу элементов НЕ 6, причем первые т ходы первой группы элементов И 2 подключены к входу 7 синхронизации устройства, входы ПДУ 5 соединены с выходами соответствующих элементов 4 задержки а выходы с п -го по 2 - с вторьми вхо- дани соответствующих элементов И 3 второй группы, информационные входы 8 устройства соединенны с вторыми входами соответствун1щих элементов И 2 первой группы, входы группы эле- ментов НЕ 6 соединены С соответствзлю щими выходами ПДУ 5, а ззыходы, кроме п-го элемента НЕ б, соединены с пёр- вш-ш входами элементов И 3 второй группы, адресные входы ПЗБ 1 соеди- пены соответственно с выходом п--го элемента НЕ 6, выходами элементов Я 3 второй группы н первым выходом ОДУ 5, первый разрядный выход ПЗБ 1 соединен с выходом 9 результата устройства,, а остальные разрядные выходы подключены к входам соответ- ств тощих элементов 4 задержки.

Устройство работает следующим об- раз.ом„

На входы 8 поступают одноименные разряды всех слагаемых начиная с младших разрядов, которые через элементы И 2 поступают на входы ПДУ 5 в течение тактового импульса по входу 7. По второй части входов ПДУ 5, соединенных с выходами элементов 4 задержки, поступает признак переноса сформированного в предьщ.ущем такте суммирования., На выходе ПДУ 5 формзя руется уплотненный код, соответствующий количеству логических единиц в коде, который был псщлн па его вход.

,-

Блок, включающий группу элементов НЕ 6, элементов И 3 и связь с первого выхода ПДУ 5, предназначен для формирования унитарного кода из уплотненного. Сформированный унитарный код активизирует одну из строк ПЗБ 1, в результате зтого считываются разряд результата на выход 9 и признаки переноса в следующий такт суммирования, которые поступают на элементы 4 задержки. Общее число тактов вычисления суммы

m п , N, где п - разрядность слагаемых; N количество слагаемых.

Пусть необходимо просуммировать следузощпе пять слагаемых: 101101, 1 10110, 011101, 110111, 100101.

Обрабатываемые срезы на выходе элементов И 2 имеют вид: 10111,01010 11111, 10100, 01110, 11011.

В течение первого тактового импульса, поданного на вход 7 синхронизации, на вход ПДУ- 5 подаются разрядный срез младших разрядов слагаемых lOlil и признак переноса 0000, так как в исходном состоянии активизирована .была первая строка ПЗБ 1 . На выходе ПДУ 5 сформируется код 000001 111, а после преобразования его в унитарный получается код 000001000. Полученный унитарный код активизирует четвертую строку ПЗБ 1, при этом на выход 9 результата поступает значение о, а признак переноса равен ООП о

Величина времени задержки сигнала формируемая элементом 4 задержки,

равна:

т - т -Т , си зэ9

)5 20 25 эп 35 40

.

50

55

где Т(. - период поступления синхрои щульсов;

Т. 5 - задержка сигналов на ПДУ 5, ПЗБ 1 и блоке преобразования уплотненного кода в унитарный,

К моменту поступления на входы ПДУ 5 второго разрядного среза, подаваемого в момент подачи второго импульса синхросигнала и равного OJOIO, на вторую часть его входов поступит признак переноса ООП. На выходе ПДУ 5 сформируется код ОООООПП, а после преобразования в унитарный - 000001000. В ПЗБ 1 будет активизирована четвертая строка.

при этом значение, результата равно О, а признака переноса - ООП

В третьем такте работы устройства на вход ПДУ 5 поступит код 111110011 После преобразования получим уплотненный код 001111111, а соответствующий ему унитарный равен 001000000, По данному адресу из ИЗБ 1 будут считаны значение результата 1 и признак переноса, равный 0111,

Аналогичным образом предлагаемое устройство продолжает работу до получения восьмого разряда суммы. Полу- ченный результат равен 11011100, В седьмом и восьмом тактах на вход элементов И 2 поступают нулевые коды.

Формула изобретения

Суммирующее устройство, содержащее постоянный запоминающий блок, первую и вторую группы элементов И, группу элементов задержки, преобра- зователь двоичного кода в уплотненный код, причем первые входы элементов И первой группы подключены к входу синхронизации устройства, входы первой группы преобразователя двоич- ного кода в уплотненный код соединены с выходами соответствующих элементов задержки группы, выходы преобразователя двоичного кода в уплотненный код с п-го по второй (где п 2т-1; m - количество операндов) соединены с первыми входами соответствующих элементов И второй группы с (n-l)-ro по первьй, о т л и ч а ю- щ е е с я тем, что, с целью упрощения устройства, в него введена группа элементов НЕ, причем информационные входы устройства соединены С Вторыми входами соответствующих элементов И первой группы, входы элементов НЕ группы соединены с соответствующими выходами преобразователя двоичного кода в уплотненный код, выходы элементов НЕ группы, кроме п-го, соединены с вторыми входами соответсвующих элементов И второй группы, адресные входы постоянного запоминающего блока соединены соответственно с выходом п-го элемента НЕ группы, выходами элементов И второй группы и первым выходом пре-п образователя двоичного кода в уплотненный код, первый разрядный выход постоянного запоминающего блока соединен с выходом результата устройства, а остальные разрядные выходы подключены к входам соответствующих элементов задержки группы, выходы элементов И первой группы соединены соответственно с входами второй группы преобразователя двоичного кода в уплотненный код.

s в

6 в

7

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное арифметическое устройство | 1986 |

|

SU1363187A1 |

| Суммирующее устройство | 1990 |

|

SU1714591A1 |

| Суммирующее устройство | 1987 |

|

SU1444752A1 |

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО ПО МОДУЛЮ | 1993 |

|

RU2034328C1 |

| Суммирующее устройство | 1990 |

|

SU1784970A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Суммирующее устройство | 1987 |

|

SU1495784A1 |

| Ассоциативное суммирующее устройство | 1983 |

|

SU1174920A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1994 |

|

RU2092891C1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств обработки цифровой информации. Цель изобретения - упрощение устройства за счет измене- НИН алгоритма преобразования разряд-. ных срезов и преобразования уплотненного кода в унитарный. Суммирующее устройство содержит постоянный запоминающий блок 1, первую и вторую группы злементов И 2,3, группу зле- ментов задержки 4, преобразователь двоичного кода в уплотненный код 5. Для достижения цели изобретения в устройство введена группа злементов НЕ 6. 2 ил. I (Л

Фи&.2

| Устройство для суммирования М чисел | 1984 |

|

SU1200281A1 |

| Ассоциативное суммирующее устройство | 1983 |

|

SU1174920A1 |

Авторы

Даты

1988-05-15—Публикация

1986-11-20—Подача