Изобретение относится к автоматике и цифровой технике и предназначено для проверки сложных блоков синхронизации, контроллеров, датчиков информации, используемых в автоматизированных системах управления, обработки информации, связи.

Цель изобретения - расширение функциональных возможностей устройства за счет контроля многоразрядных пачек импульсов.

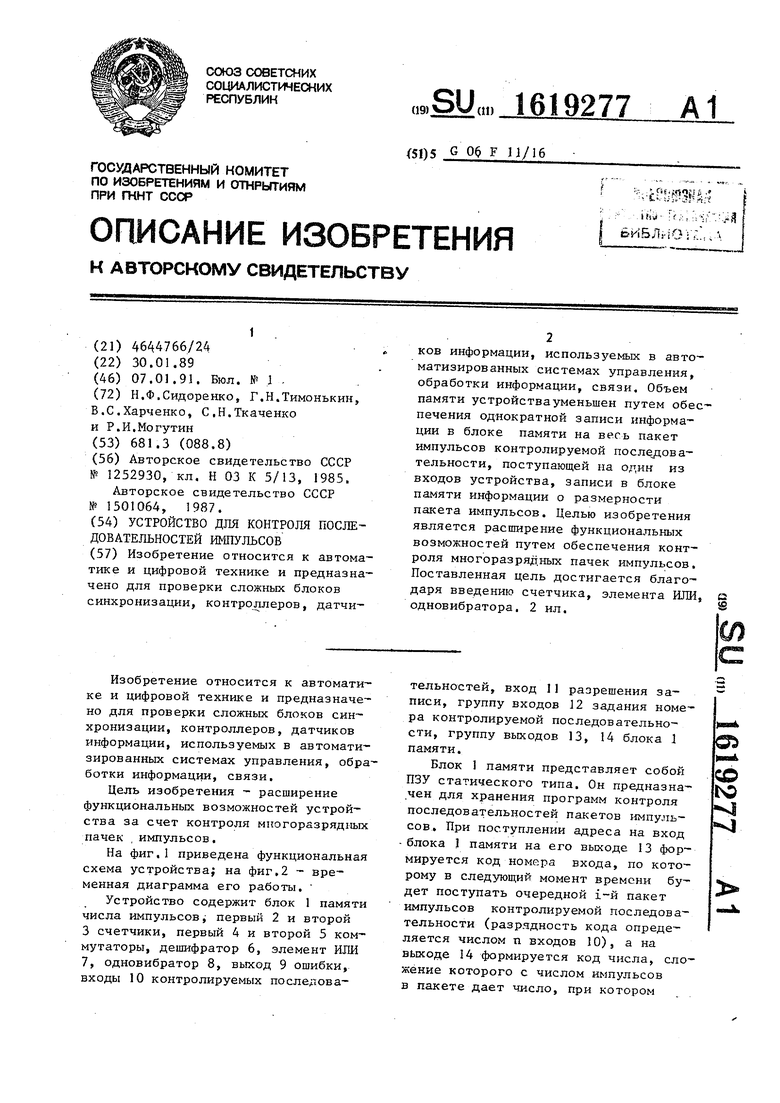

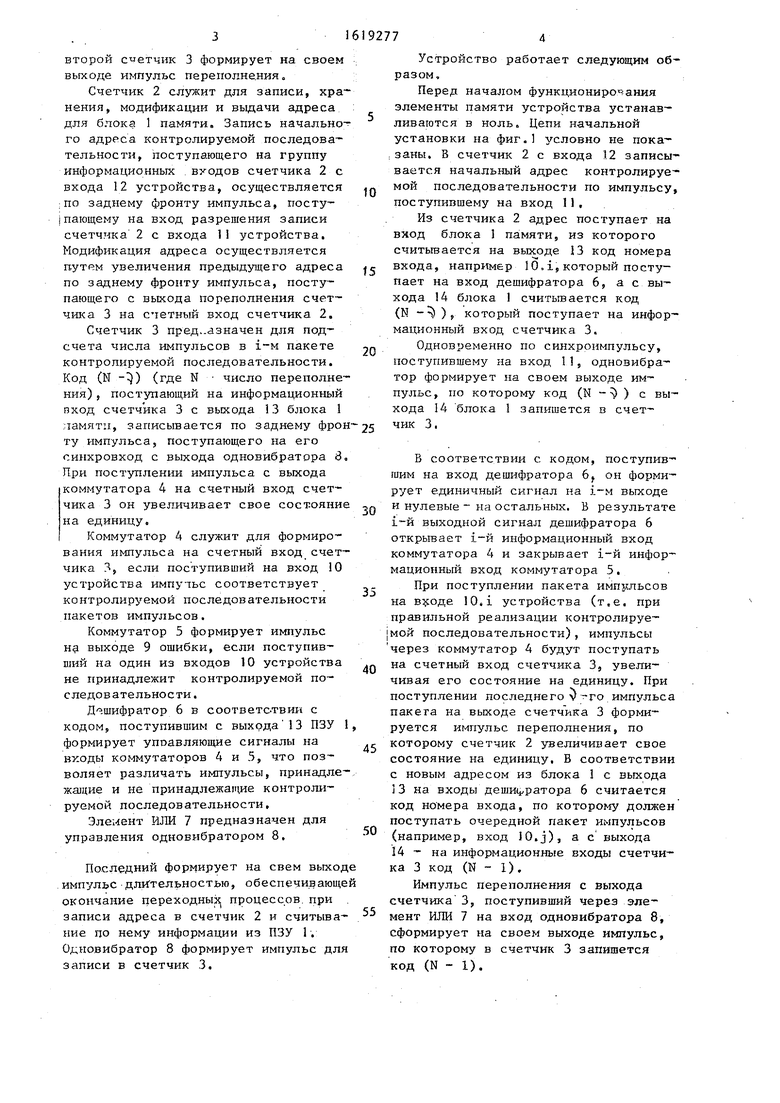

На фиг.1 приведена функциональная схема устройства; на фиг.2 - временная диаграмма его работы.

Устройство содержит блок 1 памяти числа импульсов, первый 2 и второй 3 счетчики, первый 4 и второй 5 коммутаторы, дешифратор 6, элемент ИЛИ 7, одновибратор 8, выход 9 ошибки, входы 10 контролируемых последовательностей, вход 1 разрешения записи, группу входов 12 задания номера контролируемой последовательности, группу выходов 13, 14 блока 1 памяти.

Блок 1 памяти представляет собой ПЗУ статического типа. Он предназначен для хранения программ контроля последовательностей пакетов импульсов. При поступлении адреса на вход блока 1 памяти на его выходе 13 формируется код номера входа, по которому в следующий момент времени будет поступать очередной i-й пакет импульсов контролируемой последовательности (разрядность кода определяется числом п входов 10), а на выходе 14 формируется код числа, сложение которого с числом импульсов в пакете дает число, при котором

СО

к sl

второй сметчик 3 формирует на своем выходе импульс переполнения.

Счетчик 2 служит для записи, хранения, модификации и выдачи адреса для блока 1 памяти Запись начального адреса контролируемой последовательности, поступающего на группу информационных входов счетчика 2 с входа 12 устройства, осуществляется по заднему фронту импульса, поступающему на вход разрешения записи счетччка 2 с входа 1 устройства. Модификация адреса осуществляется ггутрм увеличения предыдущего адреса по заднему фронту импульса, поступающего с выхода переполнения счетчика 3 на счетный вход счетчика 2.

Счетчик 3 предназначен для подсчета числа импульсов в i-м пакете контролируемой последовательности. Код (N -) (где N число переполнения) , поступающий на информационный вход счетчика 3 с выхода 13 блока 1 тамятп, записывается по заднему фрон ту импульса, поступающего на его синхровход с выхода одновибратора 3, При поступлении импульса с выхода коммутатора 4 на счетный вход счетчика 3 он увеличивает свое состояние на единицу.

Коммутатор 4 служит для формирования импульса на счетный вход счетчика 3, если поступивший на вход 10 устройства импульс соответствует контролируемой последовательности пакетов импульсов.

Коммутатор 5 формирует импульс нЈ выходе 9 ошибки, если поступивший на один из входов 10 устройства не принадлежит контролируемой последовательности.

Дешифратор 6 в соответствии с кодом, поступившим с выхода 13 ПЗУ 1 формирует упоавляющие сигналы на входы коммутаторов 4 и 5, что позволяет различать импульсы, принадлежащие и не принадлежащие контролируемой последовательности.

Элемент ИЛИ 7 предназначен для управления одновибратором 8.

Последний формирует на свем выход импульс длительностью, обеспечивающе

окончание переходных процессов при

записи адреса в счетчик 2 и считыва-

ние по нему информации из ПЗУ 1. Одновибратор 8 формирует импульс для записи в счетчик 3,

п

Q 5

э

0

5

0

5

0

Устройство работает следующим образом.

Перед началом функционирования элементы памяти устройства устанавливаются в ноль. Цепи начальной установки на фиг.1 условно не показаны. В счетчик 2 с входа 12 записывается начальный адрес контролируемой последовательности по импульсу, поступившему на вход 11,

Из счетчика 2 адрес поступает на вход блока 1 памяти, из которого считывается на выходе 13 код номера входа, например 10.i,который поступает на вход дешифратора 6, а с выхода 14 блока 1 считывается код (N -- )f который поступает на информационный вход счетчика 3.

Одновременно по синхроимпульсу, поступившему на вход 11, одновибра- тор формирует на своем выходе импульс, по которому код (N - ) ) с выхода 14 блока 1 запишется в счетчик 3.

В соответствии с кодом, поступившим на вход дешифратора 6 он формирует единичный сигнал на i-м выходе и нулевые - на остальных. В результате 1-й выходной сигнал дешифратора 6 открывает i-и информационный вход коммутатора 4 и закрывает i-й информационный вход коммутатора 5.

При поступлении пакета имщшьсов на входе 10.i устройства (т.е. при правильной реализации контролируе- |мой последовательности), импульсы через коммутатор 4 будут поступать на счетный вход счетчика 3, увеличивая его состояние на единицу. При поступлении последнего v го импульса пакета на выхода счетчика 3 формируется импульс переполнения, по которому счетчик 2 увеличивает свое состояние на единицу. В соответствии с новым адресом из блока 3 с выхода

13на входы дешифратора 6 считается код номера входа, по которому должен поступать очередной пакет импульсов (например, вход 10.J), а с выхода

14- на информационные входы счетчика 3 код (N - 1).

Импульс переполнения с выхода счетчика 3, поступивший через элемент ИЛИ 7 на вход одновибратора 8, сформирует на своем выходе импульс, по которому в счетчик 3 запишется код (N - 1).

5J

Если контролируемая последовательности искажена и очередной импульс поступил на другой вход (например 10.К), то этот импульс не пройдет на выход коммутатора 4, а через коммутатор 5 поступит на выход 13 устройства и сформирует сигнал ошибки (фиг. 26).

Если одновременно с импульсом, поступивши на вход, в соответствии с контролируемой последовательностью на любой другой вход поступит импульс, не принадлежащий контролируемой последовательности, то этот импульс все равно пройдет на выход коммутатора 5 и сформирует на выходе 9 сигнал ошибки.

По окончании контролируемой последовательности из блока 1 с выходов 13 и 14 будут считаны нулевые коды. В результате на всех выходах дешифратора 6 будут присутствовать нулевые сигналы, а коммутатор 5 будет открыт по всем входам. Поэтому любой импульс, поступивший на входы 10.1-10.п устройства, сформирует сигнал ошибки на выходе 9 устройства

Формула изобретения

Устройство для контроля последовательностей импульсов, содержащее блок памяти числа импульсов, первый счетчик, два коммутатора и дешифратор, причем i-й информационный вход (i 1,...,п, где п - число контролируемых последовательностей устройства) первого коммутатора соединен с i-м информационным входом второго коммутатора и является i-м входом

0

5

0

2776

контролируемой последовательности устройства, группа выходов номера контролируемой последовательности устройства соединена с группой информационных входов дешифратора, вь. ходы дешифратора соединены соответственно с управляющими входами первого коммутатора и соответственно с инверсными управляющими входами второго коммутатора, выход которого является выходом ошибки устройства,, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет контроля многоразрядных пачек импульсов, в него введен второй счетчик, элемент ИЛИ и одновибратор,, причем группа разрядных выходов первого счетчика соединена с группой адресных входов блока памяти числа импульсов, вход разрешения записи первого счетчика соединен с первым входом элемента ИЛИ и является входом разрешения записи устройства, выход элемента ИЛИ соединен с входом одновиб- ратора, выход которого соединен с входом разрешения записи второго счетчика, выход переполнения которо- го соединен со счетным входом первого счетчика и с вторым входом элемента ИЛИ, группа выходов количества импульсов пачки контролируемой последовательности блока памяти числа импульсов соединена с группой информационных входов второго счетчика, выход первого коммутатора соединен со счетным входом второго счетчика, группа информационных входов первого счетчика является группой входов задания номера контролируемой последовательности устройствл.

5

0

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательностей импульсов | 1990 |

|

SU1725373A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1651289A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1649548A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1723661A1 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1985 |

|

SU1298721A1 |

| Устройство для программного управления | 1991 |

|

SU1800445A1 |

| Устройство для передачи информации в кольцевом канале связи | 1989 |

|

SU1691864A1 |

| Устройство для контроля хода программы | 1988 |

|

SU1663612A1 |

| Устройство для контроля хода программ ЭВМ | 1987 |

|

SU1430960A1 |

Изобретение относится к автоматике и цифровой технике и предназначено для проверки сложных блоков синхронизации, контроллеров, датчи- ков информации, используемых в автоматизированных системах управления, обработки информации, связи. Объем памяти устройствауменьшен путем обеспечения однократной записи информации в блоке памяти на весь пакет импульсов контролируемой последовательности, поступающей на один из входов устройства, записи в блоке памяти информации о размерности пакета импульсов. Целью изобретения является расширение функциональных возможностей путем обеспечения контроля многоразрядных пачек импульсов. Поставленная цель достигается благодаря введению счетчика, элемента ИЛИ, одновибратора. 2 ил.

| Устройство для контроля многоканальных импульсных последовательностей | 1985 |

|

SU1252930A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля последовательностей импульсов | 1987 |

|

SU1501064A1 |

Авторы

Даты

1991-01-07—Публикация

1989-01-30—Подача