Изобретение относится к вычислительной технике и предназначено для использования в качестве специализированного вычислительного устройства.

Цель изобретения - повышение точности и быстродействия.

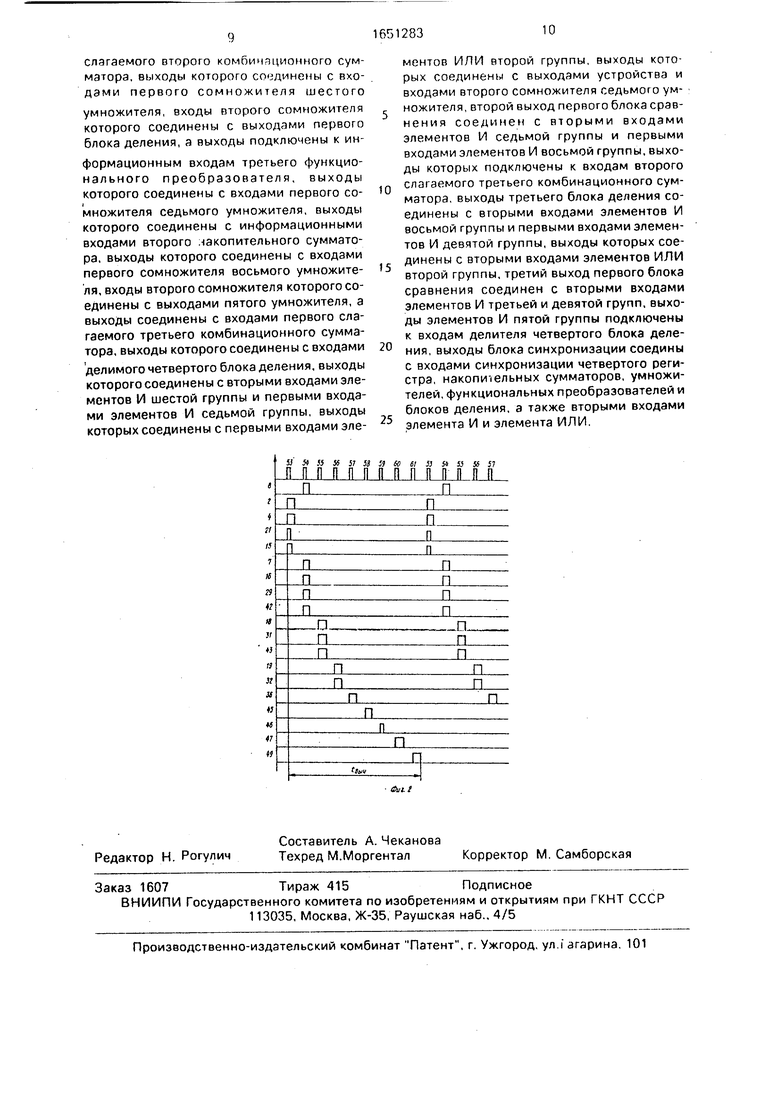

На фиг.1 изображена структурная схема предлагаемого устройства; на фиг.2 - временная диаграмма работы устройства.

Устройство состоит из первого регистра 1, первого блока 2 деления, второго регистра 3,второго блока деления, первой группы элементов НЕ 5, первого комбинационного сумматора 6, первого умножителя 7, аналого-цифрового преобразователя (АЦП) 8, элемента ИЛИ 9, элемента И 10, третьего регистра 11, первой группы элементов И 12, элемента НЕ 13, второй группы элементов И 14, четвертого регистра 15, второго умножителя 16, второй группы элементов НЕ 17, первого функционального преобразователя 18, третьего умножителя 19. пятого регистра 20, первого накопительного сумматора 21, первого блока 22 сравнения, третьей группы элементов НЕ 23, шестого регистра 24, второго блока 25 сравнения, третьей - пятой группы элементов И 26 - 28. четвертого умножителя 29, четвертой группы элементов НЕ 30, второго функционального преобразователя 31, пятого умножителя 32, первой группы элементов ИЛИ 33, пятой группы элементов НЕ 34, шестой группы элементов И 35, третьего блока 36 деления, шестой группы элементов НЕ 37, второго комбинационного сумматора 38. седьмой - девятой группы элементов И 39-41, шестого умножителя 41, третьего функционального преобразователя 43, второй группы элементов ИЛИ 44, седьмого умножителя 45, второго накопительного сумматора 46, восьмого умножителя 47, третьего комбинационного сумматора 48, четвертого блока 49 деления, тактового генератора 50, счетчика 51 импульсов и дешифратора 52, входов (шин) синхронизации 53 - 61 и блока 62 синхронизации.

Основным уравнением измерительного преобразователя скорости потока является дифференциальное уравнение первого рода,

, l«|U + r0u(t) - C0V2(t)(1)

с начальным условием ш(0) о)0, где I - момент инерции потока анемометра;

w(t) - скорость вращения ротора; го - коэффициент сил вязкого трения; Со- постоянная, зависящая от параметра анемометра;

V(t) - скорость потока.

5

,.

0 , „

Построение специализированных вычислительных устройств для решения уравнения (1) во многих практических случаях не оправдывает себя, поскольку входящая в уравнение (1) переменная w(t) имеет экспериментальное происхождение, что приводит к большим погрешностям получаемого решения при численной реализации. Поэтому весьма целесообразным является сведение уравнения (1) к эквивалентному интегральному уравнению. Такой подход к решению дифференциального уравнения (1) не только позволяет при численной реализации снизить погрешность получаемого решения, но и снижает количество вычислительных операций.

Интегральное уравнение, эквивалентное дифференциальному уравнению (1), имеет вид

J К (t-S)V(S)dS ГД) (t), (2) о

где K(t-S) - - (tab - ) т- ВТ ( s) TO i

ядро интегрального уравнения.

Уравнение (2) представляет собой интегральное уравнение Вольтерра первого рода. Использование свойства разделяемо- сти ядра позволяет представить уравнение (2) в виде

/в V(S)dS w(l) (3)

о

Устройство реализует модифицированный алгоритм численной реализации интег- рального уравнения (1) методом квадратурных сумм с использованием формулы средних прямоугольников с постоянным шагом дискретизации h const no расчетному выражению

(,л °} Г° о

-К-)те

где ,.( г)ьл,., h(,-rs узлы диск- ритизации.

В устройстве основные вычислительные операции выполняются параллельно.

Устройство начинает функционировать с приходом импульса запуска на генератор 50 импульсов. Дешифратор 52 последовательно выделяет импульсы на одном из своих выходов циклически с модулем, определяемым -коэффициентом пересчета, счетчика 51.

Рассмотрим 1-й цикл работы устройства. Перед началом работы значения коэффициентов I, го и Со заносятся соответственно в первый 1/ второй 3 и третий 11 регистры, а значения шага h и предела интегрирования Т - в регистры 20 и 24. Регистр 15, накопительные сумматоры, функциональные преобразователи, блоки деления и умножения устанавливаются в нулевое состояние. В первом такте по сигналу управления шины 53 дешифратора срабатывает АЦП 8, на вход которого управляющий сигнал шины 53 поступает через элементы. И 10 и ИЛИ 9, при этом на второй вход элемента И 10 поступает сигнал с первого выхода первого блока 22 сравнения. Следует отметить, что элемент И 10 открыт только при h 0, т.е. в начале вычисления. По этому же сигналу с шины 53 срабатывают блоки 2.4,21 и 15, на выходах которых в конце первого такта соответственно устанавливаются -р , ti

h иО,5п.

Во втором такте по сигналу управления с шины 54 дешифратора срабатывают умножители 7,16,29,42 и АЦП 8. Группа элементов И 12 открыта только в первом цикле, т.е. при h 0. При этом на выходах умножителей устанавливаются величины соответственно

K(,

i4

i

Значение + формируется на выходе I

второго комбинационного сумматора 38. В конце второго такта на выходе АЦП 8 формируется значение (tk (h), управляющий сигнал при этом поступает через элемент ИЛИ 9.

В третьем такте по сигналу управления с шины 55 дешифратора в первом 18, втором 31 и третьем 43 функциональных преобразователях формируются значения функций соответственно

-Jjrash

Г Н-JjSLt

И7

э и e -1 i

В четвертом такте по сигналу управления с шины 56 дешифратора срабатывают умножители 19 и 32, на выходах которых соответственно формируется значения

,5ЬС0х Г0

ет (

(o)-ЈL).

В пятом такте по сигналу управления с шины 57 дешифратора срабатывает блок 36 деления. Группа элементов И 26 открыта

только в первом цикле (при ti h), в остальных случаях она закрыта, а группа элементов И 27 открыта только при ti h. Группа элементов И 14 закрыта только при ti h, a в остальных случаях она открыта. По сигнаЛУ управления в этом такте в блоке 36 формируется значение

4W/-(,

, если ti h, и (Do (ti))/h, если tl h. В шестом такте по сигналу управления шины 58 дешифратора срабатывает умножитель 45. При этом группа элементов И 39 открыта, если tj h, з группа элементов И 41 открыта, если ti h, в остальных случаях она закрыта. В конце этого такта на выходе умножителя 45 получают значение

(е.Ь

если ti h, и V( тЈ), если tl - h. В седьмом такте по сигналу управления шины 59 дешифратора срабатывает второй накопительный сумматор 46. на выходе которого формируется сумма

-а Ze

.v(ti4M.

В восьмом такте по сигналу управления шины 60 срабатывает умножитель 47, на выходе которого в конце этого такта получают значение

W. -г i fn з x -p e з j + i v/, v V°a r0) з e 0Vlti4b

В девятом такте по сигналу управления шины 61 дешифратора срабатывает блок 49 деления. При этом группа элементов И 40 открыта, если ti h, а в остальных случаях она закрыта. На выходе блока 49 получают значение скорости потока на i-м шаге

(ы.1ИиДоЬЈ е 3 :2е 1ч() 4t) i}.р,

-la.(.

.которое через группу элементов 39 подается на вход второй группы элементов ИЛИ 44, выходы которых являются выходом устройства. На второй вход группы элементов ИЛИ 44 подается значение с выхода группы элементов И 41.

Блок 22 сравнения служит для управления элементами И 10, 12, (4, 27, 28, 26, 39 - 41, блок 25 сравнения - для установления момента окончания вычислений или останова устройства.

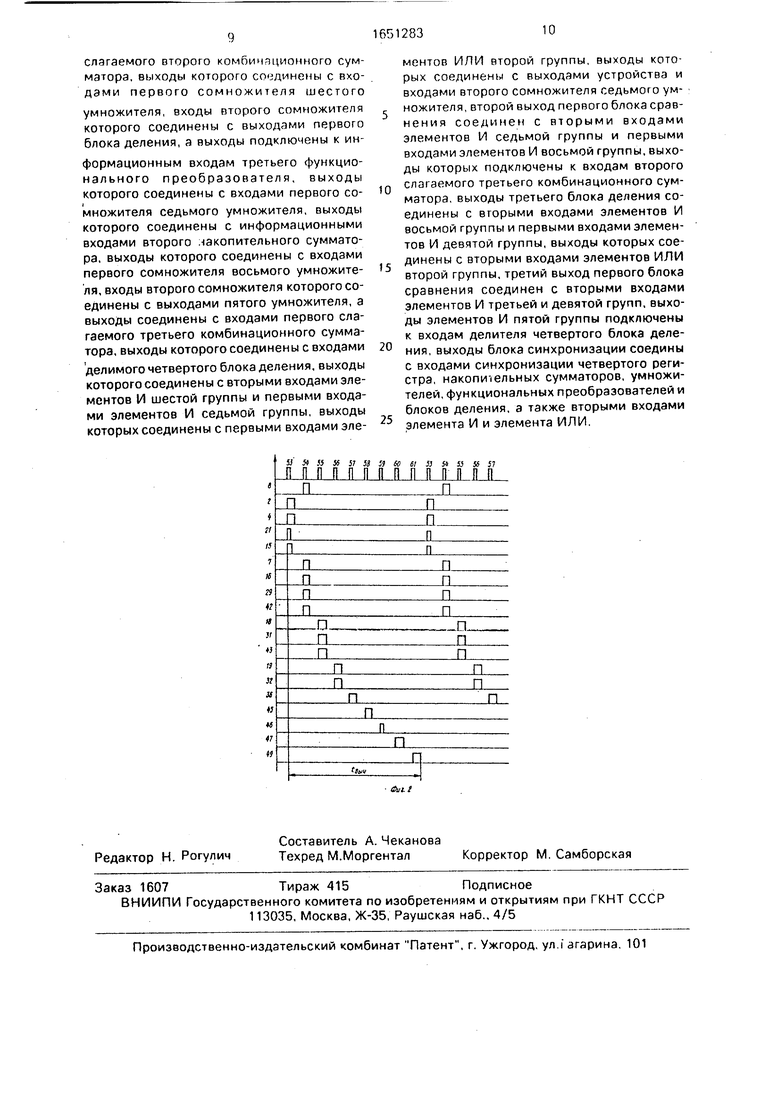

Временная диаграмма (фиг.2) иллюстрирует работу устройства, степень распараллеливания вычислительного процесса, а также уменьшение затраты времени на подготовительные работы, связанные с вычислением значений ah (0), оъ (п) и V(h/,2),

Формула изобретения - Устройство для решения интегрального Сравнения измерительного преобразователя скорости потока, содержащее первый и второй регистры, первый накопительный сумматор, первый умножитель, первый комбинационный сумматор, первую группу элементов НЕ, блок синхронизации, причем выходы первого комбинационного сумматора соединены с входами первого сомножителя первого умножителя, отличающее- с я тем, что, с целью повышения точности и быстродействия, в него введены с второго по восьмой умножители, четыре блока деления, элемент ИЛИ, элемент И, две группы элементов ИЛИ, второй и третий комбинационные сумматоры, второй накопительный сумматор, три функциональных преобразователя, два блока сравнения, аналого-цифровой преобразователь, с третьего по шестой регистры, девять групп элементов И, с второй по шестую группы элементов НЕ и элемент НЕ, причем выходы первого регистра соединены с входами делителя первого блока деления, выходы которого соединены с входами второго сомножителя первого умножителя и первого сомножителя второго умножителя, выходы второго регистра соединены с входами делимого первого блока деления и входами делителя второго блока деления, входы делимого которого соединены с выходами третьего регистра, а выходы подключены к входам элементов НЕ первой группы, выходы которых соединены с входами первого слагаемого первого комбинаци- онного сумматора, входы второго слагаемого которого подключены к выходам элементов И первой группы, информационный вход устройства соединен с информа- ционным входом аналого-цифрового преобразователя, выходы которого соединены первыми входами элементов И первой, второй групп, выходы четвертого регистра соединены с входами второго сомножителя второго умножителя, выходы которого через вторую группу элементов НЕ соединены с информацинным входом первого функционального преобразователя,

to

15

20

25

30

35

40

45

50

55

выходы которого соединены с входами первого сомножителя третьего умножителя, входы второго сомножителя которого соединены с выходами первого умножителя, а выходы соединены с первыми входами элементов И третьей группы, выходы которых соединены с первыми входами элементов ИЛИ первой группы, выходы которых соединены с входами делителя третьего блока деления, входы делимого которого подключены к выходам элементов И второй группы, выходы пятого регистра соединены с информационными входами четвертого регистра, первыми входами элементов И четвертой группы входами первой группы первого блока сравнения и информационными входами первого накопительного сумматора, выходы которого соединены с входами первого слагаемого второго комбинационного сумматора, входами второй группы первого блока сравнения и входами первой группы второго блока сравнения, входы второй группы которого подключены к выходам шестого регистра, а выход подключен к выходу Останов устройства, первый выход первого блока сравнения соединен с вторыми входами элементов И первой группы, первым входом элемента И и через элемент НЕ с вторыми входами элементов И второй группы, выход элемента И соединен с первым входом элемента ИЛИ, выход которого соединен с входом запуска аналого-цифрового преобразователя, выходы первого блока деления соединены с входами первого сомножителя четвертого умножителя, входы второго сомножителя которого подключены к выходам первого накопительного сумматора, а выходы через элементы НЕ четвертой группы соединены с информационными входами второго функционального преобразователя, выходы которого соединены с входами первого сомножителя пятого умножителя, входы второго сомножителя которого соединены с выходами первого умножителя, выходы элементов НЕ третьей группы соединены с первыми входами элементов И пятой группы, второй выход первого блока сравнения соединен с вторыми входами; элементов И четвертой и пятой групп, выходы элементов И четвертой группы соединены с вторыми входами элементов ИЛИ первой группы, выходы четвертого регистра через пятую группу элементов НЕ соединены с первыми входами элементов И шестой группы, выходы которых соединены с входами второго слагаемого второго комбинационного сумматора, выходы пятого регистра через элементы НЕ шестой группы соединены с входами третьего

9

слагаемого второго комбинационного сумматора, выходы которого соединены с входами первого сомножителя шестого умножителя, входы второго сомножителя которого соединены с выходами первого блока деления, а выходы подключены к информационным входам третьего функционального преобразователя, выходы которого соединены с входами первого соi

множителя седьмого умножителя, выходы которого соединены с информационными входами второго .накопительного сумматора, выходы которого соединены с входами первого сомножителя восьмого умножителя, входы второго сомножителя которого соединены с выходами пятого умножителя, а выходы соединены с входами первого слагаемого третьего комбинационного сумматора, выходы которого соединены с входами делимого четвертого блока деления, выходы которого соединены с вторыми входами элементов И шестой группы и первыми входами элементов И седьмой группы, выходы которых соединены с первыми входами эле1651283

10

5

0

5

ментов ИЛИ второй группы, выходы которых соединены с выходами устройства и входами второго сомножителя седьмого ум- ножителя, второй выход первого блока срав- нения соединен с вторыми входами элементов И седьмой группы и первыми входами элементов И восьмой группы, выходы которых подключены к входам второго слагаемого третьего комбинационного сумматора, выходы третьего блока деления соединены с вторыми входами элементов И восьмой группы и первыми входами элементов И девятой группы, выходы которых соединены с вторыми входами элементов ИЛИ второй группы, третий выход первого блока сравнения соединен с вторыми входами элементов И третьей и девятой групп, выходы элементов И пятой группы подключены к входам делителя четвертого блока деления, выходы блока синхронизации соедины с входами синхронизации четвертого регистра, накопительных сумматоров, умножителей, функциональных преобразователей и блоков деления, а также вторыми входами элемента И и элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения интегральных уравнений | 1987 |

|

SU1446619A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Устройство для извлечения квадратного корня | 1982 |

|

SU1136155A1 |

| Устройство для умножения чисел в непозиционной системе счисления | 1981 |

|

SU1015382A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для вычисления нелинейных интегральных операторов | 1987 |

|

SU1424017A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

Изобретение относится к вычислительной технике и предназначено для использования в качестве специализированного вычислительного устройства. Цель изобретения - повышение точности и быстродействия. Устройство содержит регистр 1, блок Шнш-6| 2 деления, регистр 3, блок 4 деления, группу элементов НЕ 5, комбинационный сумматор 6, умножитель 7, аналого-цифровой преобразователь 8, элемент ИЛИ 9, элемент И 10, ре1 гистр 11, группу элементов И 12, элемент НЕ 13, группу элементов И 14,регистр 15,умножитель 16, группу элементов НЕ 17, функциональный преобразователь 18, умножитель 19, регистр 20, накопительный сумматор 21, блок 22 сравнения, группу элементов НЕ 23, регистр 24, блок 25 сравнения, группы элементов И 26 - 28, умножитель. 29, группу элементов НЕ 30, функциональный преобразователь 31, умножитель 32, группу элементов ИЛИ 33, группу элементов НЕ 34, группу элементов И 35. блок 36 деления, группу элементов НЕ 37, комбинационный сумматор 38, группы элементов И 39 - 41, умножитель 42, функциональный преобразователь 43, группу элементов ИЛИ 44, умножитель 45, накопительный сумматор 46, умножитель 47, комбинационный сумматор 48, блок 49 деления и блок 62 синхронизации. 2 ил. Ml ТЙ-И Ј О сл го 00 OJ s)s aittrast(ft о/

| Устройство для решения интегральных уравнений | 1987 |

|

SU1446619A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1099755 | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1991-05-23—Публикация

1989-06-09—Подача