4 4

Изобретение относится к электросвязи и может быть использовано для передачи данных, подверженных воздействию помех.

Целью изобретения является повышение быстродействия устройства.

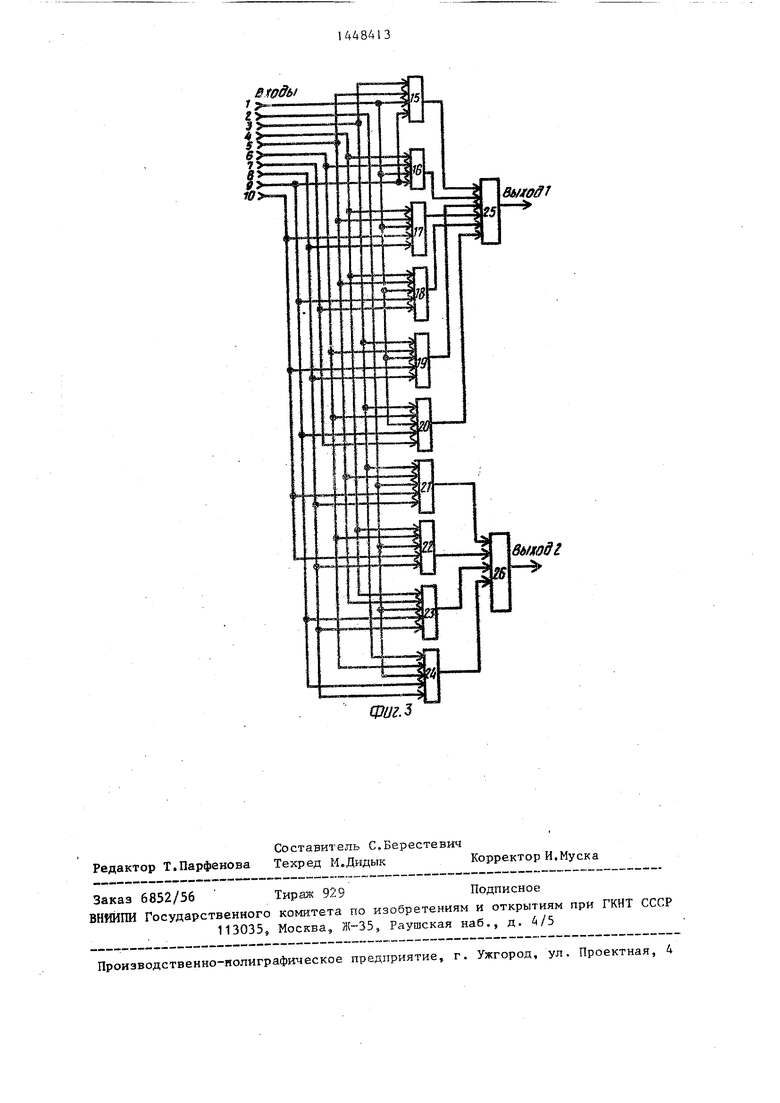

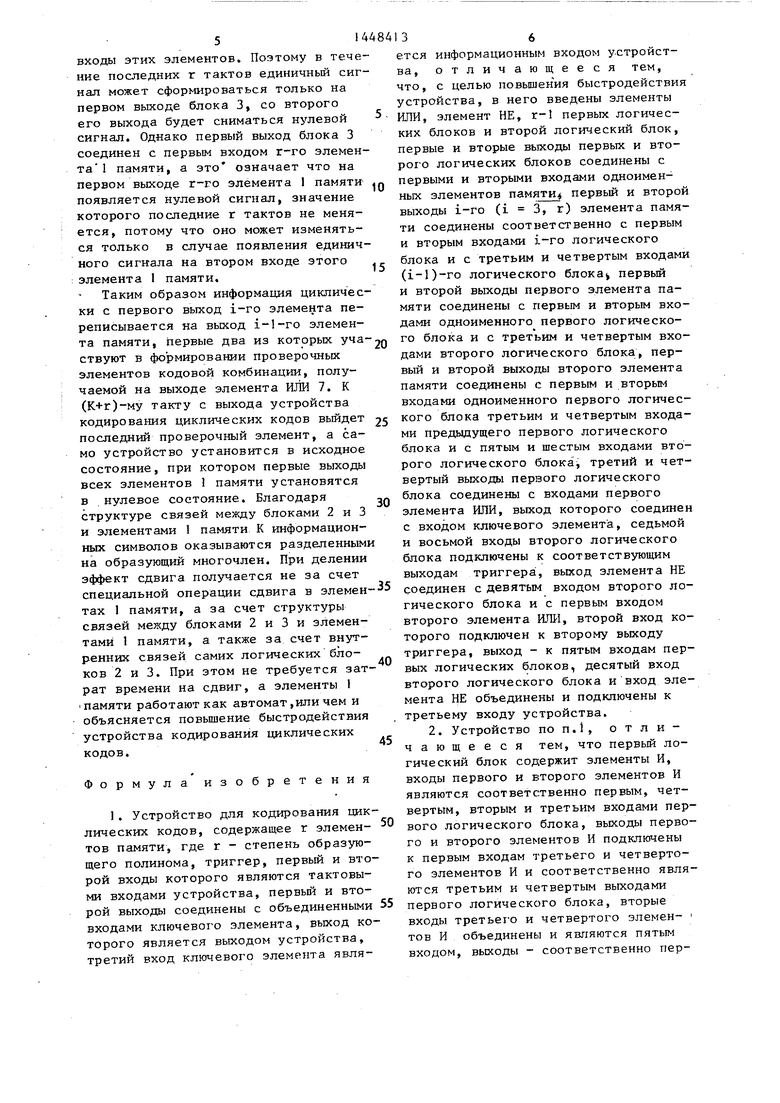

На фиг.1 представлена структурная электрическая схема предлагаемого устройства; на фиг,2 - схема логического блока первого типа; на фиг.З - то же, второго типа.

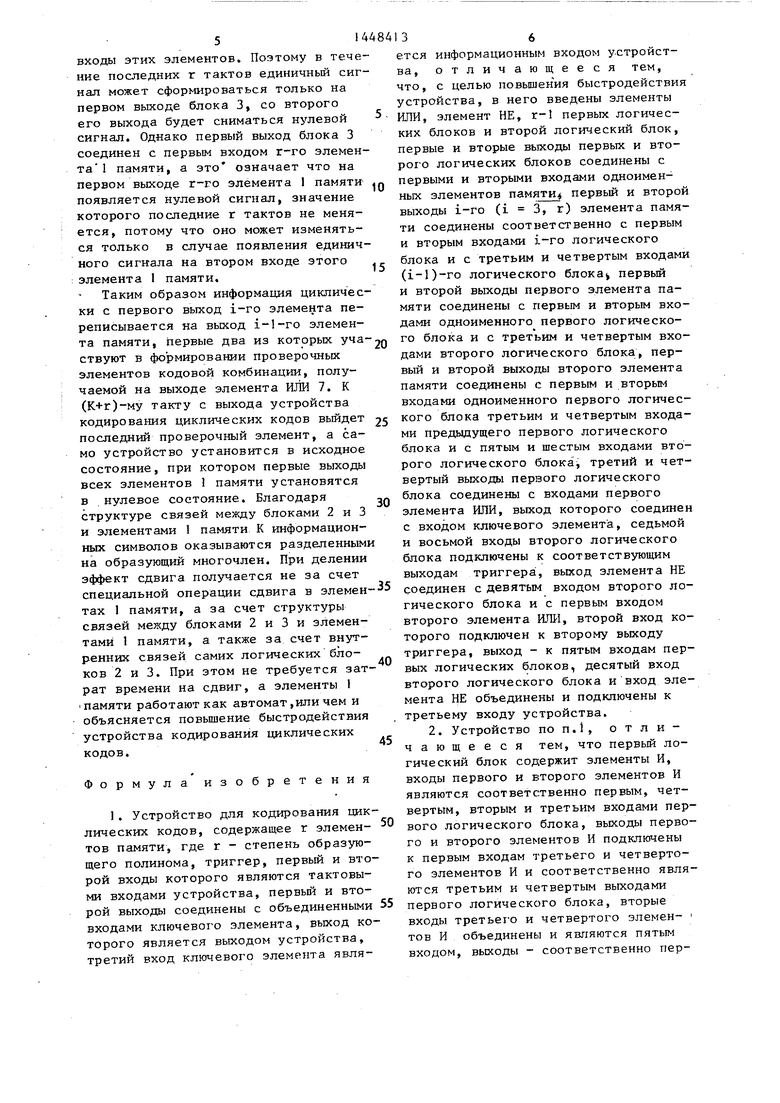

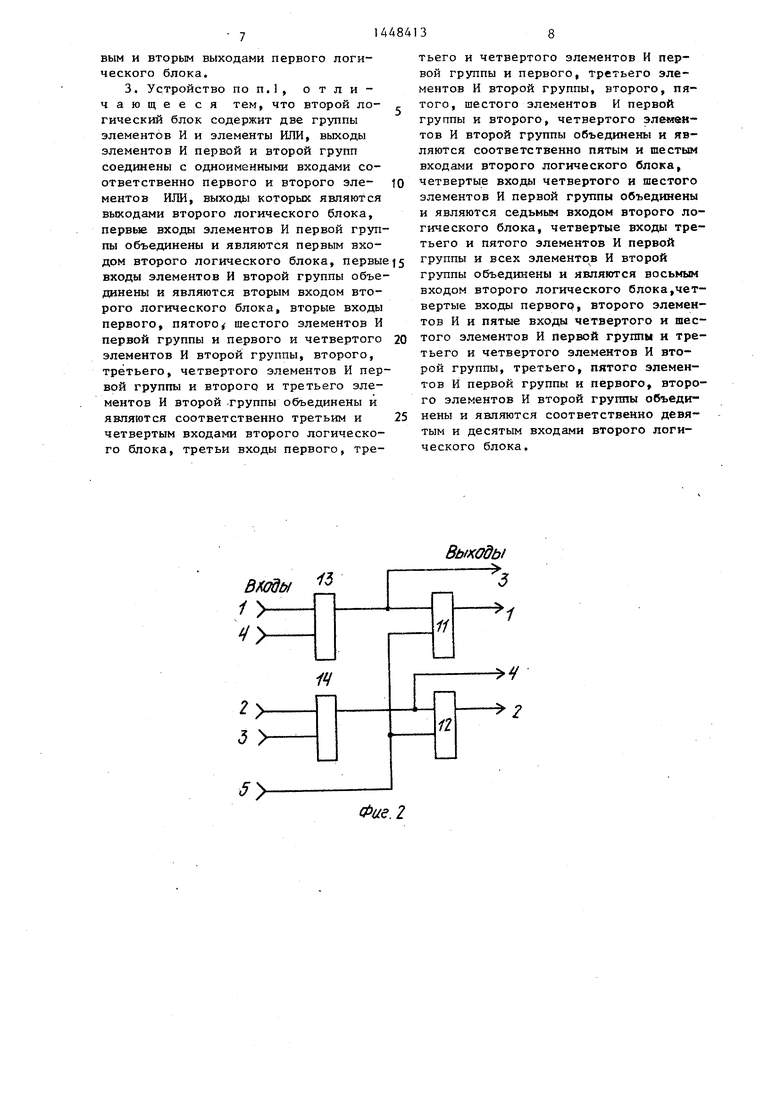

Устройство (фиг.1) содержит элементы 1.1-1.г памяти, первые логические блоки 2.1-2(г-1), второй логический бло1с 3, триггер 4, элементы НЕ 5 элементы ИЛИ 6 и 7, ключевой элемент 8, выполненный на элементе ИЛИ 9, элементах И 1D.1, 10.2. Каждый из первых логических блоков (фиг.2), содержит элементы И 11-14. Второй логический блок (фиг.З), содержит элементы И 15-24, элементы ИЛИ 25 и 26.

Устройство работает следующим об

разом.

Для кодирования циклических кодов с образующими многочленами вида X + X 1 первые логические блоки реализуют функции возбуждения

- VR; XiX,4i (или,);

Vs; X,X;,,(U,V и).

второй логический блок реализует функции возбуждения

Vft ( хД,)и, V (X,X.;VX,Xi)35

(UiU VUiUi)XKi

Vsr C(XiXiVX,X2)U V(X, ХДР , (2)

где V|;. и Vg. - функции возбуждения, 40 соответственно R- и S-входов i-го элемента памяти;

X., Х. - соответственно, состояние прямого и ин- 45 версного выхода i-ro элемента памяти; и т, Ij - соответственно, прямое и инверсное значения информационногоСП входа устройства; и, и-2 - соответственно значения прямого и инверсного выхода триггера.55 Элементы памяти служат дпя хранения промежуточных и оконча тельных результатов деления информации на образующий многочлен. Количество элементов памяти, а также логических блоков 2 и 3 равно г - максимальному показателю образующего многочлена.

Логические блоки 2 и 3 служат для реализации функций возбуждения (I и 2) выходы блоков возбуждают входы R и S элементов 1 памяти.

Элемент ИЛИ 7 служит для реализации функции выхода

Y X,,X,i,

(3)

1520

25

30

35

40 45СП55посредством которой формируются проверочные элементы кодовой комбинации.

Элементы НЕ 5 и ИЛИ 6 служат для реализации функции

f (u,vuj),

которая участвуеп; в формировании функции возбуждения (1).

В исходном состоянии первые вьтхо- ды элементов 1 памяти и выходы блоков 2 и 3 находятся з нулевом состоянии . На первом такте работы устройства на первый вход триггера 4 распределителя с первого выхода распределителя подается импульс, который переводит его в состояние, при котором со второго выхода триггера 4 распределителя на третий вход ключевого элемента 8 и восьмой вход блока 3 подается единичный сигнал. С первого выхода триггера 4 распределителя на второй вход ключевого элемента 8 и седьмой вход блока 3 подается нулевой сигнал.

На десятый вход блока 3 и одновременно на четвертый вход ключевого элемента 8 последовательно в течение К тактов подаются информационные сигналы, прохождение которых через ключевой элемент 8 разрешается с второго выхода триггера 4 распределителя сигналом. Прохождение проверочных сигналов с выхода элемента ИЛИ 7 запрещается нулевым сигналом с первого выхода распределителя.

Инверсное значение входного информационного сигнала подается с выхода элемента НЕ 5 на девятьш вход блока 3 и второй вход элемента РШИ 6, на выходе которого формируется функция (,), принимающая участие в формировании функций возбуждения (1) всех г-1-х элементов 1 памяти. Поэтому выход элемента ИЛИ 6 соединен с пятыми )зходами всех г-1-х логических блоков 2.

Так как в исходном состоянии устройства с выходов блоков 2 снимаются нулевые сигналы, на первом такте работы г-1-ые элементы 1 памяти не изменяют своего состояния.

В зависимости от вида информации, подаваемой с входа устройства кодирования циклических кодов на девятый вход блока 3 первые К тактов, в фор- мировании функции возбуждения (2) г-го элемента 1 памяти участвуют все элементы И и ИЛИ блока 3, кроме элементов И 18 и 20, прохождение сигналов через которые запрещено нулевым сигналом с седьмого входа блока 3.

В том случае если на вход устройства подан единичный сигнал, то он через элементы И 22 и ИЛИ 26 поступает на второй выход блока 3. Формиро-. ванне единичных сигналов на выходах остальных элементов И запрещено нулевым сигналом с первого входа блока 3 для элементов И 15-20 и нулевым сигналом с девятого входа блока 3 эле- ментов И 23 и 24 и нулевым сигналом с третьего входа блока 3 для элемента И 21, поэтому на первом выходе блока 3 формируется нулевой сигнал. Единичный сигнал с второго выхода блока 3 переводит первый выход г-го элемента 1 памяти в единичное состояние. На втором такте работы устройства этот единичный сигнал с первого выхода г-го элемента 1 памяти посту- пает на третий вход (r-l)-ro блока 2 в котором участвует в формировании функций возбуждения (1) (r-l)-го элемента 1 памяти. При этом, так как на второй и пятый входы (г-)-го блока 2 также подаются единичные сигналы, снимаемые со второго (инверсного) выхода (r-l)-ro элемента 1 памяти и выхода элемента ИЛИ 6 соответственно, единичный сигнал через элементы И 13 и 11 поступает на второй выход (г-1)го блока 2 и в силу связи между ним и вторым входом (г-1)-го элемента 1 памяти последний изменяет свое состояние на противоположное: на первом выходе (r-l)-ro элемента 1 памяти появляется единица, В свою очередь благодаря связи между первым выходом (r-l)-ro элемента 1 памяти и первым входом (r-l)-ro блока 2 на следующем такте работы устройства в (г-1)-м блоке 2 разрешается прохолздение сигнала с четвертого входа через элементы И 13 и 11 .на его первый выход и

о дновременно запрещается нулевым сигналом с второго выхода (г-1)-го элемента 1 памяти на второй вход (г-1)- го блока 2 прохождение сигнала с третьего входа (r-l)-ro блока 2 через элементы И 14 и 12 на его второй выход.

В дальнейшем до (К+1)-го такта работа устройства происходит аналогично; на J-M такте работы сигналы, сформированные на выходах i-ro и (i+l)-ro элементов 1 памяти, участвуют в формировании состояния i-ro элемента 1 памяти на (j+l)-M такте с помощью функций возбуждения (1) и (2), сформированных в i-м блоке на J-M такте работы устройства.

В том случае, если на первом такте работы устройства не десятый вход блока 3 подается нулевой сигнал, то он не изменяет состояния его выходов а следовательно, и не возбуждает входы г-го элемента 1 памяти. Поэтому устройство сохранит свое прежнее, исходное состояние.

На (К+1)-м такте работы устройства единичный сигнал с (К+1)-го выхода распределителя подается на второй вход триггера 4 распределителя и переводит его первый вход в единичное, а второй выход - в нулевое состояние Тем самым разрешается прохождение - сигналов в течение г тактов на выход устройства с элемента ИЛИ 7 и запрещается прохождение сигналов с входа устройства, на который последние г тактов подаются нулевые сигналы.

Выходные сигналы на выходе элемента ИЛИ 7 формируются в соответствии с функцией вызсода (3). При этом дизъюнкция второго выхода первого элемента 1 памяти и первого выхода второго элемента 1 памяти формируется элементом И 14 ; первого логического блока 2 и подается на его четвертый выход, а дизъюнкция второго выхода первого элемента 1 памяти формируется элементом И 13 первого логического блока 2 и подается на его третий выход.

Логический блок 3 последние г тактов формирует функции возбуждения (2 с помощью элементов И 15, 16, 18 и 20 на свой первый выход. Работа элементов И 17, 19, 21-24 запрещена нулевым сигналом с второго выхода триггера 4 распределителя, снимаемьм с восьмого входа блока 3 на пятые

5

входы этих элементов. Поэтому в течние последних г тактов единичный синал может сформироваться только на первом выходе блока 3, со второго его выхода будет сниматься нулевой сигнал. Однако первый выход блока 3 соединен с первым входом г-го элемента 1 памяти, а это означает что на первом выходе г-го элемента 1 памяти появляется нулевой сигнал, значение которого последние г тактов не меняется, потому что оно может изменяться только в случае появления единичного сигнала на втором входе этого ;элемента 1 памяти.

Таким образом информация циклически с первого выход i-ro элемента переписывается на вькод i-1-го элемента памяти, первые два из которых уча ствуют в формировании проверочных элементов кодовой комбинации, получаемой на выходе элемента ИЛИ 7. К (К+г)-му такту с выхода устройства кодирования циклических кодов выйдет последний проверочный элемент, а само устройство установится в исходное состояние, при котором первые выходы всех элементов 1 памяти установятся в .нулевое состояние. Благодаря структуре связей между блоками 2 и 3 и элементами 1 памяти К информационных символов оказываются разделенным на образующий многочлен. При делении эффект сдвига получается не за счет специальной операции сдвига в элемен тах 1 памяти, а за счет структуры связей между блоками 2 и 3 и элементами 1 памяти, а также за счет внутренних связей самих логических блоков 2 и 3. При этом не требуется затрат времени на сдвиг, а элементы 1 Памяти работают как автомат, или чем и объясняется повышение быстродействия устройства кодирования циклических кодов.

Формула изобретения

1. Устройство для кодирования циклических кодов, содержащее г элемен- тов памяти, где г - степень образующего полинома, триггер, первый и второй входы которого являются тактовыми входами устройства, первьй и вто2. Устройство по П.1, отли чающееся тем, что первьй л гический блок содержит элементы И, входы первого и второго элементов являются соответственно первым, че вертым, вторым и третьим входами п вого логического блока, выходы пер го и второго элементов И подключен к первым входам третьего и четверт го элементов И и соответственно яв ются третьим и четвертым выходами

рой выходы соединены с объединенньми 55 первого логического блока, вторые входами ключевого элемента, выход которого является выходом устройства, третий вход ключевого элемента являвходы третьег о и четвертого элемен тов И объединены и являются пятым входом, выходы - соответственно пе

0

5

п 5

5

0

0

5

е.тся информационным входом устройства, отличающееся тем, что, с целью повышен ия быстродействия устройства, в него введены элементы ИЛИ, элемент НЕ, г-1 первых логических блоков и второй логический блок, первые и вторые выходы первых и второго логических блоков соединены с первыми и вторыми входами одноименных элементов памяти первый и второй выходы i-ro (L 3, г) элемента памяти соединены соответственно с первым и вторым входами i-го логического блока и с третьим и четвертым входами (i-l)-ro логического блока первый и второй выходы первого элемента памяти соединены с первым и вторым входами одноименного первого логического блока и с третьим и четвертым входами второго логического блока, первый и второй выхода второго элемента памяти соединены с первым и вторым входами одноименного первого логического блока третьим и четвертым входами предыдущего первого логического блока и с пятым и шестым входами второго логического блока, третий и четвертый выходы первого логического блока соединены с входами первого элемента ИЛИ, выход которого соединен с входом ключевого элемента, седьмой и восьмой входы второго логического блока подключены к соответствующим выходам триггера, выход элемента НЕ соединен с девятым входом второго логического блока и с первым входом второго элемента ИЛИ, второй вход которого подключен к второму выходу триггера, выход - к пятым входам первых логических блоков, десятый вход второго логического блока и вход элемента НЕ объединены и подключены к третьему входу устройства.

2. Устройство по П.1, отличающееся тем, что первьй логический блок содержит элементы И, входы первого и второго элементов И являются соответственно первым, четвертым, вторым и третьим входами первого логического блока, выходы первого и второго элементов И подключены к первым входам третьего и четвертого элементов И и соответственно являются третьим и четвертым выходами

первого логического блока, вторые

входы третьег о и четвертого элемен- тов И объединены и являются пятым входом, выходы - соответственно первым и вторым выходами первого логического блока.

3. Устройство по п., отличающееся тем, что второй ло- гический блок содержит две группы элементов И и элементы ИЛИ, выходы элементов И первой и второй групп соедш ены с одноименными входами соответственно первого и второго эле- ментов ИЛИ, выходы которых являются выходами второго логического блока, первые входы элементов И первой группы объединены и являются первым входом второго логического блока, первые входы элементов И второй группы объединены и являются вторым входом второго логического блока, вторые входы первого, пяторо шестого элементов И первой группы и первого и четвертого элементов И второй группы, второго, третьего, четвертого элементов И первой группы и второго и третьего элементов И второй труппы объединены и являются соответственно третьим и четвертым входами второго логического блока, третьи входы первого, третьего и четвертого элементов И первой группы и первого, третьего элементов И второй группы, второго, пятого, шестого элементов И первой группы и второго, четвертого элементов И второй группы объединены и являются соответственно пятым и шестым входами второго логического блока, четвертые входы четвертого и шестого элементов И первой группы объединены и являются седьмым входом второго логического блока, четвертые входы третьего и пятого элементов И первой группы и всех элементов И второй группы объединены и являются восьмым входом второго логического блока,четвертые входы первого, второго элементов И и пятые входы четвертого и шестого элементов И первой группы и третьего и четвертого элементов И второй группы, третьего, пятого элементов И первой группы и первого, второго элементов И второй группы объединены и являются соответственно девятым и десятым входами второго логического блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное цифровое устройство для определения амплитуды и длительности случайных сигналов | 1983 |

|

SU1233170A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Универсальный вычислительный автомат | 1983 |

|

SU1196844A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Последовательное множительное устройство | 1981 |

|

SU1067500A1 |

| Устройство для контроля последовательности выполнения программ с оперативной корректировкой зависимостей | 1989 |

|

SU1665379A1 |

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Устройство цифровой передачи и приема телевизионного сигнала | 1985 |

|

SU1309327A1 |

Изобретение относится к технике электросвязи и может быть использовано для передачи данных, подверженных воздействию помех. Целью изобретения является повьшение быстродействия устройства. Устройство содержит элементы 1.1-1.г памяти, где г - степень образующего полинома, первые логические блоки 2.1-2(г-1), второй логический блок 3, триггер 4, элемент НЕ 5, элементы ИЛИ 6 и 7, ключевой элемент 8. 2 з.п. ф-лы, З ил.

Вьтоды

Фые.г

втды 1

i

BA/JfOffT

выяод1

Фиг.

| Устройство кодирования циклических кодов | 1973 |

|

SU510782A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Абдуллаев Д.А.,Арипов М.Н | |||

| Передача дискретных сообщений в задачах и упражнениях | |||

| М.: Радио и связь, 1985, с | |||

| Цилиндрический сушильный шкаф с двойными стенками | 0 |

|

SU79A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-12-30—Публикация

1987-01-06—Подача