w го

А Мf5:ff#

:№-

М#

Изобретение относится к вычислительной технике и может быть использовано для контроля правильности выполнения программ ЭВМ и других устройств и систем программного управления, а также для автоматизированной отладки программ и контроля очередности следования модулей программ.

Цель изобретения - повышение контроля гибкости.

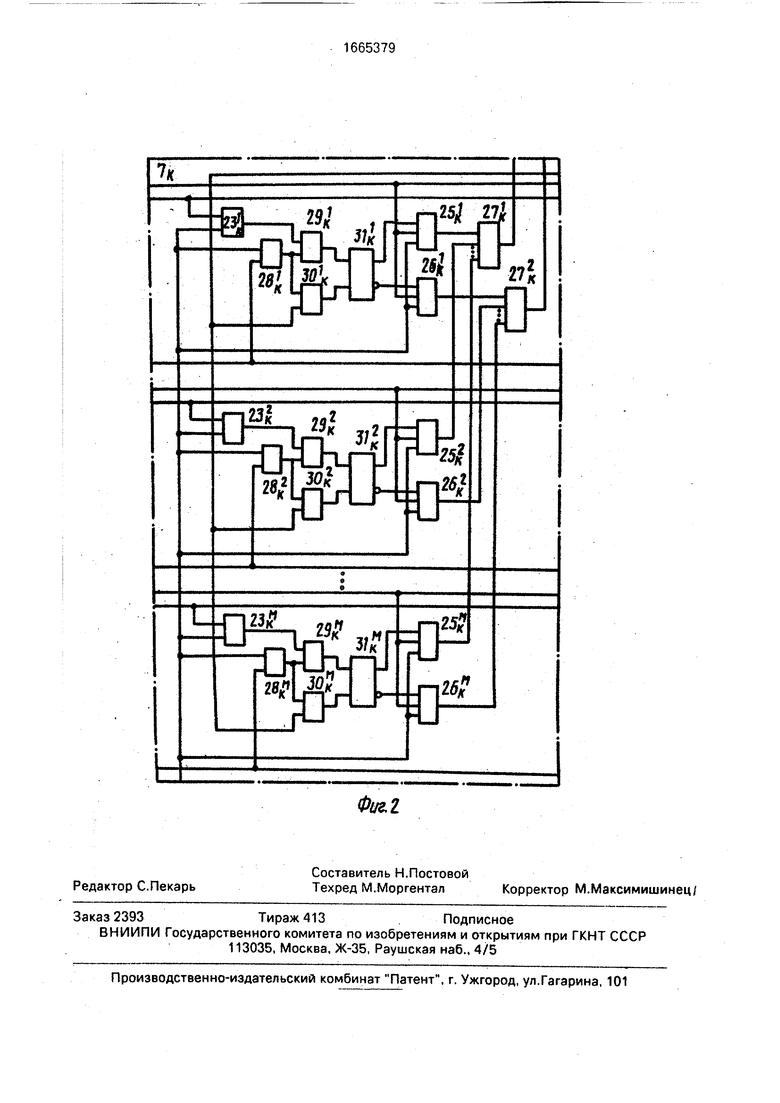

На фиг. 1 представлена структурная схема устройства; на фиг.2 - структурная схема 1-го столбца блока оперативной памяти.

Устройство для контроля последовательности выполнения программ содержит дешифратор 1, первую группу 2 элементов ИЛИ, третью группу 3 элементов И, группу 4 триггеров записи и контроля, первую группу 5 элементов И, вторую группу 6 элементов И, блок 7 оперативной памяти, элемент ИЛИ 8, вторую группу 9 элементов ИЛИ, третью группу 10 элементов ИЛИ, первую группу 11 элементов задержки, вторую группу 12 элементов задержки, четвертую группу 13 элементов И, группу 14 триггеров коррекции, первый вход 15 сброса устройства, информационный вход 16 устройства, вход 17 разрешения записи устройства, вход 18 разрешения контроля устройства, вход 19 разрешения коррекции устройства, второй вход 20 сброса устройства, выход 21 Норма контроля устройства, выход 22 Ненорма контроля устройства, первый элемент И 23 ячейки блока оперативной памяти, третий вход 24 сброса устройства, второй элемент И 25 ячейки блока оперативной памяти, третий элемент И 26 ячейки блока оперативной памяти, группу 27 элементов ИЛИ столбца блока оперативной памяти, четвертый элемент И 28 ячейки блока оперативной памяти, первый элемент ИЛИ 29 ячейки блока оперативной памяти, второй элемент ИЛИ 30 ячейки блока оперативной памяти, триггер 31 ячейки блока опе- ративной памяти, третью группу 32 элементов задержки.

Устройство функционирует в пяти режимах: 1 - подготовительный режим; 2 - режим записи зависимостей модулей программы; 3 - режим записи исходных данных; 4 - режим контроля правильности включения модуля в работу программы; 5 - режим коррекции зависимостей модулей программы.

Во время подготовительного режима сигналы поступают на первый 15, второй 20 и третий 24 входы сброса устройства, при этом триггеры записи и контроля группы 4, триггеры коррекции группы 14 и триггеры 31 блока 7 оперативной памяти устанавливаются в нулевое состояние.

На протяжении всего режима записи зависимостей модулей программы присутствует сигнал на входе 17 разрешения записи устройства, который поступает на вторые

входы элементов И 5 первой группы.

Режим записи делится на циклы, а циклы в свою очередь на такты.

На первом такте первого цикла режима записи на информационный вход 16 устрой0 ства подается номер модуля (I). Дешифратор 1 преобразует номер модуля в сигнал на i-м выходе, который через 1-й элемент задержки 32i третьей группы, 1-й элемент ИЛИ 2| первой группы и 1-й элемент И 3i третьей

5 группы устанавливает в единичное состояние 1-й триггер записи и контроля 4. С единичного выхода установившегося в единичное состояние 1-го триггера записи и контроля группы 4 сигнал поступает, во-первых, через

0 первый элемент ИЛИ 10i третьей группы на вторые инверсные входы элементов И третьей группы 3, запрещая установку других триггеров записи и контроля группы 4 в единичное состояние, во-вторых, на первый вход

5 i-ro элемента И первой группы 5 и далее на 1-й вход разрешения записи блока 7 оперативной памяти. Элементы 32 задержки третьей группы предотвращают одновременное поступление сигналов в блок 7 оперативной па0 мяти с выходов дешифратора 1 и с выходов элемента И 5 первой группы.

На втором такте первого цикла режима записи на информационный вход 16 устройства последовательно подаются номера (К)

5 модулей, которые могут быть включены в работу после i-ro модуля (номер которого поступил на информационный вход 16 на первом такте). Дешифратор 1 каждый последовательно поступающий номер преобра0 зует в сигнал на К-ом выходе, который поступает только на информативный вход блока 7 оперативной памяти (так как на вторые инверсные входы всех элементов И 3 третьей группы поступает запрещающий

5 сигнал лог. 1) и через К-й вход разрешения контроля блока 7 оперативной памяти устанавливает соответствующий триггер 31 к1 (I, К)-й ячейки блока 7 оперативной памяти в единичное состояние.

0 Единичное состояние триггера 31 к10, К)-й ячейки блока 7 оперативной памяти содержит информацию о возможности следования К-го модуля за i-м модулем программы. На третьем такте режима записи посту5 пает сигнал на первый вход 15 сброса устройства, триггеры записи и контроля группы 4 устанавливаются в нулевое состояние, на вторые инверсные входы всех элементов И третьей группы 3 запрещающий сигнал лог. 1 не поступает.

Далее устройство переходит к второму циклу режима записи (к первому такту) и т.д., пока не будут записаны все зависимости модулей программ.

В режиме записи исходных данных записывается номер первого (начального) модуля программы, который начинает выполняться в вычислительном процессе.

На информационный вход 16 устройства поступает номер i первого (начального) модуля программы. Дешифратор 1 преобразует этот номер в сигнал на l-м выходе, который через соответствующий 1-й элемент 32i задержки третьей группы, 1-й элемент ИЛИ 2 первой группы и 1-й элемент И 3 третьей группы устанавливает 1-й триггер 4| записи и контроля группы 4 в единичное состояние. Данный 1-й триггер А хранит информацию о номере модуля программы, выполняющегося в ЭВМ. С единичного выхода указанного 1-го триггера 4| записи и контроля сигнал поступает, во-первых, на вход первого элемента ИЛИ третьей группы 10 и далее на вторые инверсные входы всех элементов И третьей группы 3, запрещая установку других триггеров записи и контроля группы в единичное состояние, во-вторых, на первый вход 1-го элемента И первой группы 5 и на первый вход элементов И второй группы 6, но далее он не проходит, так как на вторые входы 1-х элементов И первой 5 и второй 6 групп разрешающий сигнал не поступает.

В течение всего режима контроля правильности включения модуля в работу присутствует сигнал на входе 18 разрешения контроля устройства, который разрешает прохождение сигнала с единичного выхода 1-го триггера записи и контроля группы 4, установленный в единичное состояние в режиме записи исходных данных.

На первом такте режима контроля на информационный вход 16 устройства поступает номер (К) запрошенного в работу модуля. Дешифратор 1 преобразует этот номер в сигнал на К-м выходе, который поступает на каждый информационный вход блока 7 оперативной памяти (так как на вторых инверсных входах элементов И третьей группы 3 присутствует запрещающий сигнал еще с периода режима записи исходных данных).

Если триггер 31 к блока 7 оперативной памяти находится в нулевом состоянии (в программе отсутствует связь между модулями I и К в данной последовательности), то сигнал с нулевого выхода триггера 31 к1 (I, К)-й ячейки блока 7 оперативной памяти через соответствующий третий элемент И 26 (I, К)-й ячейки блока 7 оперативной памяти и

второй элемент ИЛИ 27к группы К-го столбца блока 7 оперативной памяти, второй элемент ИЛИ 92 второй группы поступает на выход 22 Ненорма контроля устройства,

5 запрещая включение (К-го) модуля в работу программы.

Если триггер 31 к (,К)-й ячейки блока 7 оперативной памяти находится в единичном состоянии (К-й модуль программы мо0 жет следовать за l-м), то сигнал с единичного выхода триггера 31к (I, К}-й ячейки блока 7 оперативной памяти поступает через второй элемент И 25 (I, К)-й ячейки блока 7 оперативной памяти, первый элемент ИЛИ

5 27к группы К-го столбца блока 7 оперативной памяти, первый элемент ИЛИ 9i второй группы на выход 21 Норма контроля устройства. Этим сигналом через элемент ИЛИ 8 будут приведены в нулевое состояние

0 триггеры записи и контроля группы 4| через время, необходимое для приведения в нулевое состояние триггеров записи и контроля группы 4 через соответствующий К-й элемент 11к задержки первой группы, К-й эле5 мент ИЛИ 2к первой группы 2, К-й элемент И Зк третьей группы, устанавливается в единичное состояние К-й триггер записи и контроля группы 4 и через первый элемент ИЛИ 10i третьей группы элементом И 3

0 третьей группы запрещается установка других триггеров записи и контроля группы 4 в единичное состояние. В дальнейшем номер переписанного модуля в К-й триггер записи . и контроля группы 4 фигурирует как номер

5 последнего выполненного модуля.

Далее устройство переходит к второму такту режима контроля и т.д. Работа устройства на втором и последующих тактах режима аналогична.

0 В процессе решения задач на различных участках вычислительного процесса зависимость следования модулей программ может изменяться и возникает необходимость оперативной коррекции информации,

5 записанной в блоке 7 оперативной памяти. В течение всего режима коррекции зависимостей модулей программы присутствует сигнал на входе 19 разрешения коррекции устройства, поступающий на третьи входы

0 элементов И четвертой группы 13.

Данный режим протекает по циклам, а циклы соответственно по тактам.

На каждом цикле инвертируется состояние одной ячейки блока 7 оперативной па5 мяти, состояние триггера 31na(q, п)-й ячейки блока 7 оперативной памяти переходит в противоположное. Это говорит о том, что если модуль п программы не мог следовать за модулем а, то после коррекции он может следовать или если модулю п было разрешено выполнение после модуля q, то после коррекции такое выполнение запрещено.

На первом такте первого цикла на информационный вход 16 устройства поступает номер q модуля программы, Дешифратор 1 преобразует этот номер в сигнал на q-м выходе, который через q-й элемент 12q задержки второй группы и второй вход q-ro элемента И 13q четвертой группы устанавливает q-й триггер 4Ч коррекции группы в единичное состояние. Сигнал с единичного выхода q-ro триггера 14 коррекции поступает, во-первых, через q-й вход второго элемента ИЛИ 10q третьей группы на первые инверсные входы элементов И четвертой группы 13, запрещая установку других триггеров коррекции группы 14 в единичное состояние, во-вторых, на q-й вход разрешения оррекции блока 7 оперативной памяти.

На втором такте на информационный вход 16 устройства поступает намер п модуля, зависимость следования которого после модуля q необходимо изменить. Эта информация через n-й выход дешифратора поступает на n-й информационный вход блока 7 оперативной памяти, сигнал лог. 1 будет только на выходе четвертого элемента И 28П4 (q, п)-й ячейки блока 7 оперативной памяти, который через первые элементы ИЛИ 29ПЧ (q, п)-й ячейки блока 7 оперативной памяти, второй элемент 30nq (q. п)-й ячейки блока 7 оперативной памяти поступает на j-й и на К-й входы триггера 31nq (q, п)-й ячейки блока 7 оперативной памяти, изменяя его состояние на противоположное. s

На третьем такте сигнал поступает на второй вход 20 сброса устройства, триггеры коррекции группы 14 устанавливаются в нулевое состояние.

Далее устройство переходит к следующему циклу режима коррекции и так далее и корректируется необходимое количество ячеек блока 7 оперативной памяти. Формула изобретения 1, Устройство для контроля последовательности выполнения программ с оперативной корректировкой зависимостей, содержащее дешифратор, первую группу элементов ИЛИ, вторую группу элементов ИЛИ, первую группу элементов И, вторую группу элементов И. первую группу элементов задержки, группу триггеров записи и контроля, блок оперативной памяти, причем - выходы группы выходов Норма контроля блока оперативной памяти соединены с соответствующими входами первого элемента ИЛИ второй группы и входами соответствующих элементов задержки первой группы, выходы которых соединены с первыми входами элементов ИЛИ первой группы, выход первого элемента ИЛИ второй группы является выходом Норма контроля устройства, группа выходов Ненорма контроля блока

оперативной памяти соединена с входами второго элемента ИЛИ второй группы, выход которого является выходом Ненорма контроля устройства, выходы триггеров записи и контроля группы соединены соответ0 ственно с первыми входами элементов И первой группы, группа выходов которой соединена с группой входов разрешения записи блока оперативной памяти, группа входов разрешения контроля блока опера5 тивной памяти соединена с группой выходов второй группы элементов И, входы группы информационных входов блока оперативной памяти соединены с соответствующими выходами дешифратора, вход

0 которого является информационным входом устройства, отличающееся тем, что, с целью повышения гибкости контроля, в него введены третья группа элементов И, элемент ИЛИ, третья группа элементов

5 ИЛИ, вторая группа элементов задержки, четвертая группа элементов И, группа триггеров коррекции, третья группа элементов задержки, причем первый вход элемента ИЛИ является первым входом сброса уст0 ройства, выходы дешифратора соединены с соответствующими входами элементов задержки второй и третьей групп, выходы элементов задержки третьей группы соединены с вторыми входами элементов

5 ИЛИ первой группы, выходы которых соединены с первыми входами элементов И третьей группы, инверсные вторые входы которых соединены с выходом первого элемента ИЛИ третьей группы, входы которого

0 соединены с прямыми выходами группы триггеров записи и контроля, входы установки в 1 которых соединены с соответствующими выходами элементов И третьей группы, входы установки в О группы триг5 герое записи и контроля объединены и соединены с выходом элемента ИЛИ, второй вход которого соединен с выходом первого элемента ИЛИ второй группы, прямые выходы группы триггеров коррекции соединены

0 с соответствующими входами группы входов разрешения коррекции блока оперативной памяти и с соответствующими входами второго второго элемента ИЛИ третьей группы, выход которого соединен с инверс5 ными первыми входами элементов И четвертой группы, вторые входы которых соединены с выходами элементов задержки второй группы, третьи входы элементов И четвертой группы объединены для подклю- чения к входу разрешения коррекции устройства, входы начальной установки триггеров коррекции группы объединены и соединены с вторым входом сброса устройства, входы установки в 1 триггеров коррекции группы соединены с соответствующими вы- ходами элементов И четвертой группы, вход сброса блока оперативной памяти подключен к третьему входу сброса устройства, вторые входы элементов И первой группы объединены для подключения к входу раз- решения записи устройства, вторые входы элементов И второй группы объединены для подключения к входу разрешения контроля устройства.

2. Устройство по п. 1. о т л и ч а ю щ е е- с я тем, что блок оперативной памяти содержит матрицу М, К ячеек, первую группу К элементов ИЛИ, вторую группу К элементов или, причем с первого по К-й входы разрешения контроля i-й строки матрицы объединены для подключения к соответствующему i-му входу группы входов разрешения контроля блока оперативной памяти, с первого по К-й входы разрешения записи i-й строки матрицы объединены для подключе- ния к соответствующему i-му входу группы входов разрешения записи блока оперативной памяти, с первой по К-й входы разреше- ния коррекции i-й строки матрицы объединены для подключения к соответст- вующему i-му входу группы входов разрешения коррекции блока оперативной памяти, с первого по М-й информационные входы 1-го столбца матрицы объединены для подключения соответствующему i-му входу группы информационных входов блока оперативной памяти, входы сброса ячеек матрицы объединены для подключения к входу сброса блока оперативной памяти, выход Норма контроля ячейки блока оператив- ной памяти i-й строки j-ro столбца соединен с i-входом 1-го элемента ИЛИ первой группы, выходы которой образуют группу выходов Норма контроля блока оперативной памяти, выход Ненорма ячейки блока оперативной памяти i-й строки j-ro столбца соединен с i-входом j-ro элемента ИЛИ второй группы, выходы которой образуют группу выходов Ненорма контроля блока оперативной памяти.

3. Устройство поп.1,отличающее- с я тем, что каждая ячейка блока оперативной памяти содержит четыре элемента И, два элемента ИЛИ, триггер, причем первый вход первого элемента И является входом разрешения записи ячейки блока оперативной памяти, второй вход первого элемента И, первые входы второго, третьего, четвертого элементов И объединены для подключения к информационному входу ячейки блока оперативной памяти, второй вход третьего элемента И соединен с нулевым выходом триггера, единичный выход которого соединен с вторым входом второго элемента И, третий выход которого и третий выход третьего элемента И объединены для подключения к входу разрешения контроля ячейки блока оперативной памяти, выход первого элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого и первый вход второго элемента ИЛИ соединен с выходом четвертого элемента И, второй вход которого является входом разрешения коррекции ячейки блока оперативной памяти, выход первого элемента ИЛИ соединея с единичным входом триггера, нулевой вход которого соединен с выходом второго элемента ИЛИ. второй вход которого является входом сброса ячейки блока оперативной памяти, выход второго элемента И является выходом Норма контроля ячейки блока оперативной памяти, выход третьего элемента И является выходом Ненорма контроля ячейки блока оперативной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности выполнения программ | 1988 |

|

SU1674134A1 |

| Устройство для контроля последовательности выполнения программ | 1985 |

|

SU1254493A1 |

| Резервированное устройство для контроля и управления | 1991 |

|

SU1830535A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля правильности выполнения программ ЭВМ и других устройств и систем программного управления, а также для автоматизированной отладки программ и контроля очередности следования модулей программ. Целью изобретения является повышение гибкости контроля. Поставленная цель достигается за счет возможности коррекции зависимостей модулей программ в блоке оперативной памяти как в выборочном режиме, так и в режиме контроля последовательности выполнения программ. Устройство для контроля последовательности выполнения программ с оперативной корректировкой зависимости содержит дешифратор 1, группы 2, 9, 10 элементов ИЛИ, группы 5, 6, 3, 13 элементов И, группу 4 триггеров записи и контроля, блок 7 оперативной памяти, группу 14 триггеров коррекции, группы 11, 12, 32 элементов задержки. 2 з.п.ф-лы, 2 ил.

| Устройство для контроля выполненияпРОгРАММы | 1979 |

|

SU842823A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля последовательности выполнения программ | 1985 |

|

SU1254493A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1991-07-23—Публикация

1989-04-04—Подача