СП

Изобретение относится к цифровой ычислительной технике и предназна- чено для использования в универсальных и специа11изированных вычислительных устройствах.

Цель изобретения - повышение достоерности работы устройства.

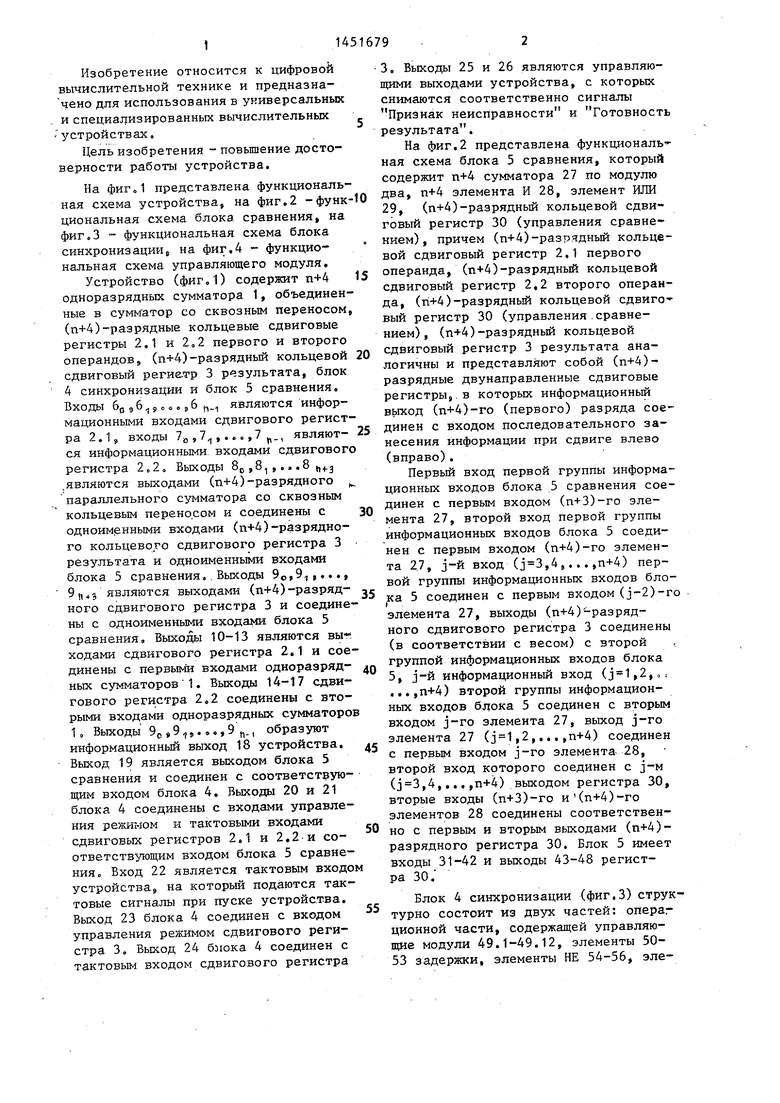

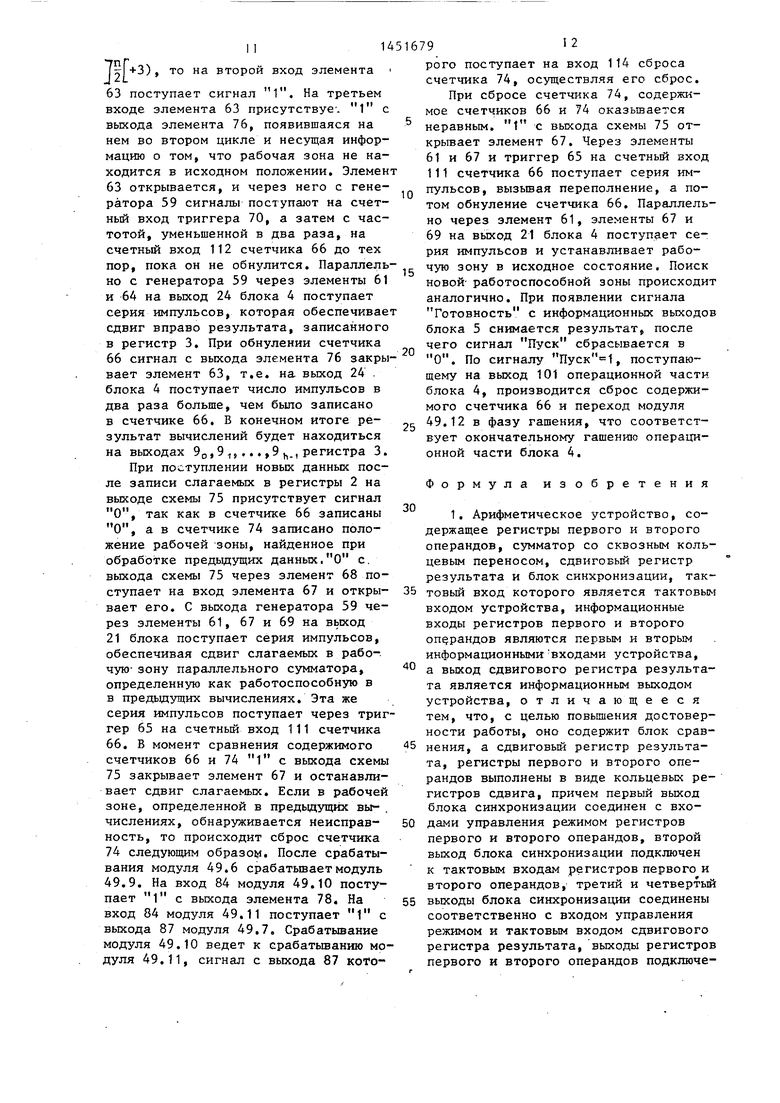

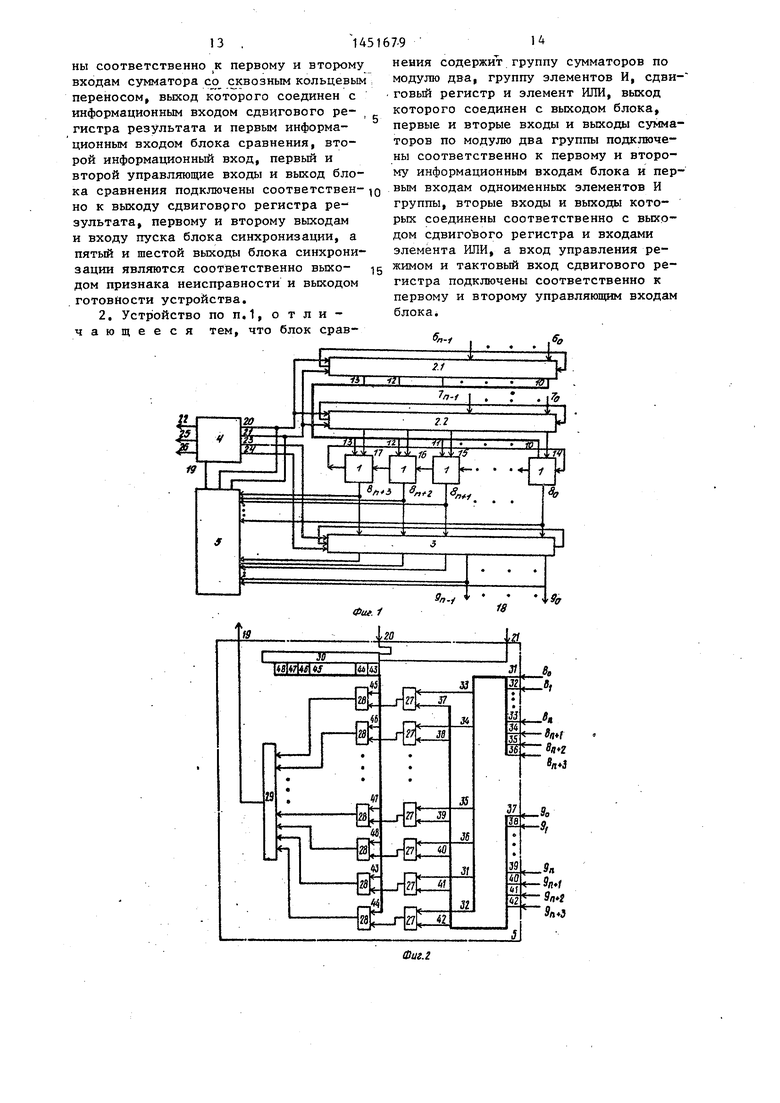

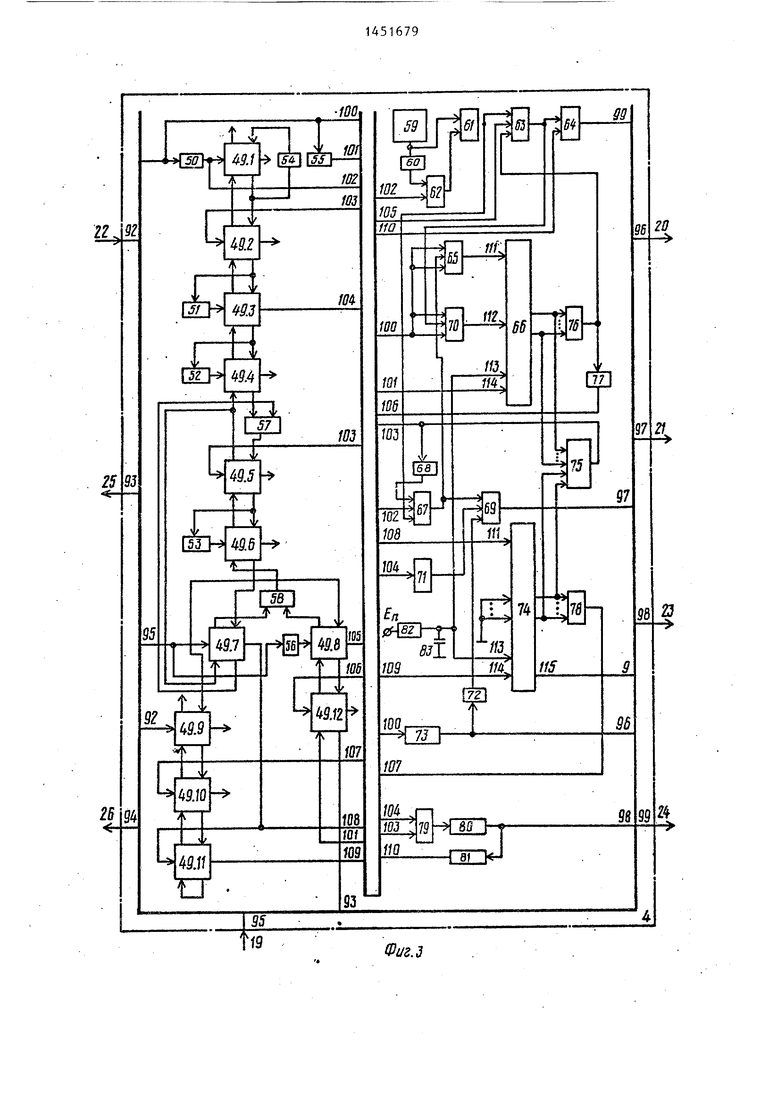

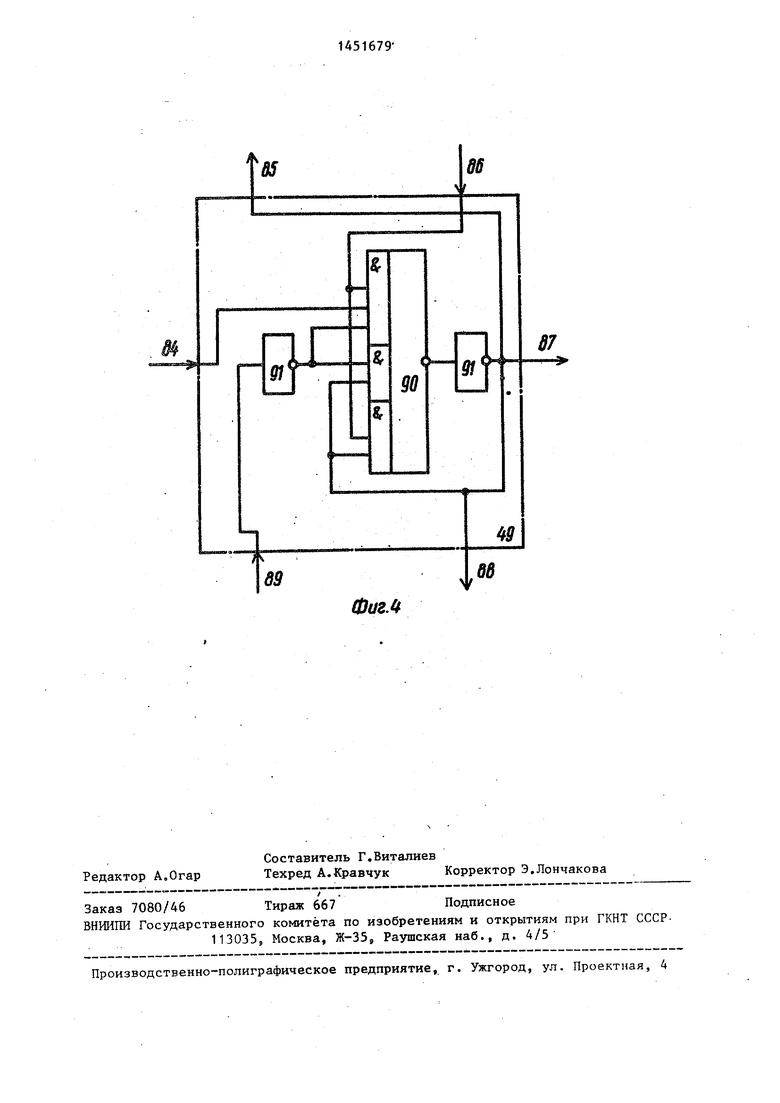

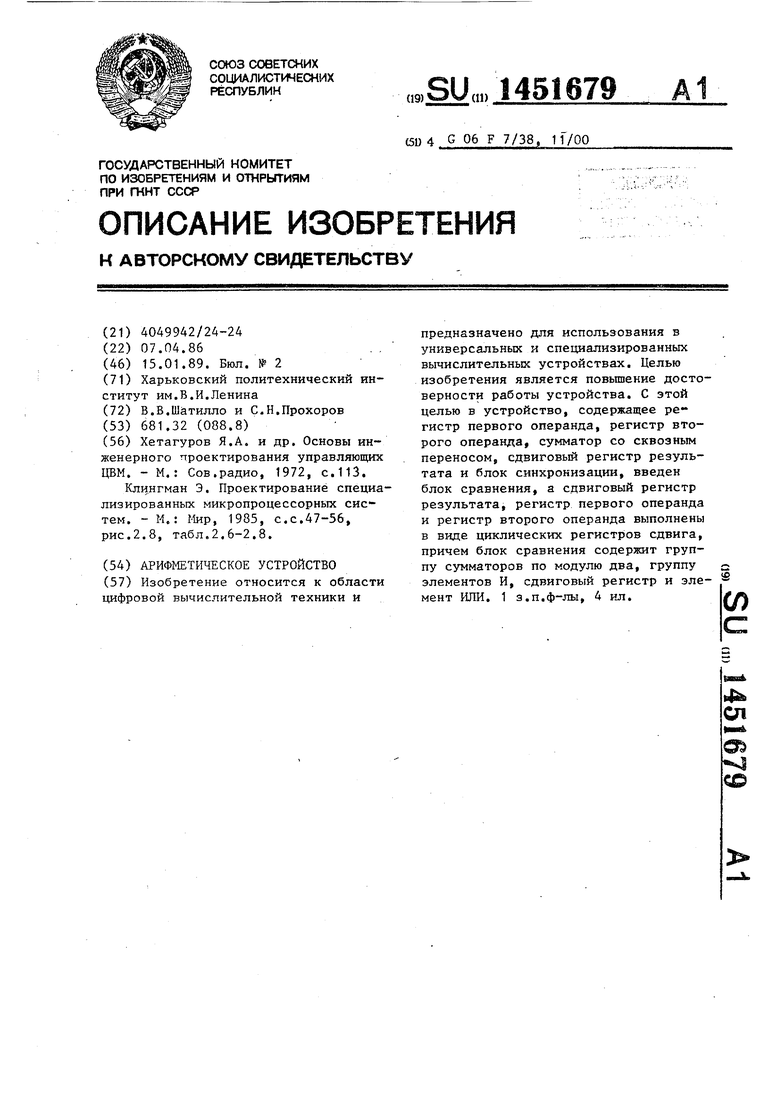

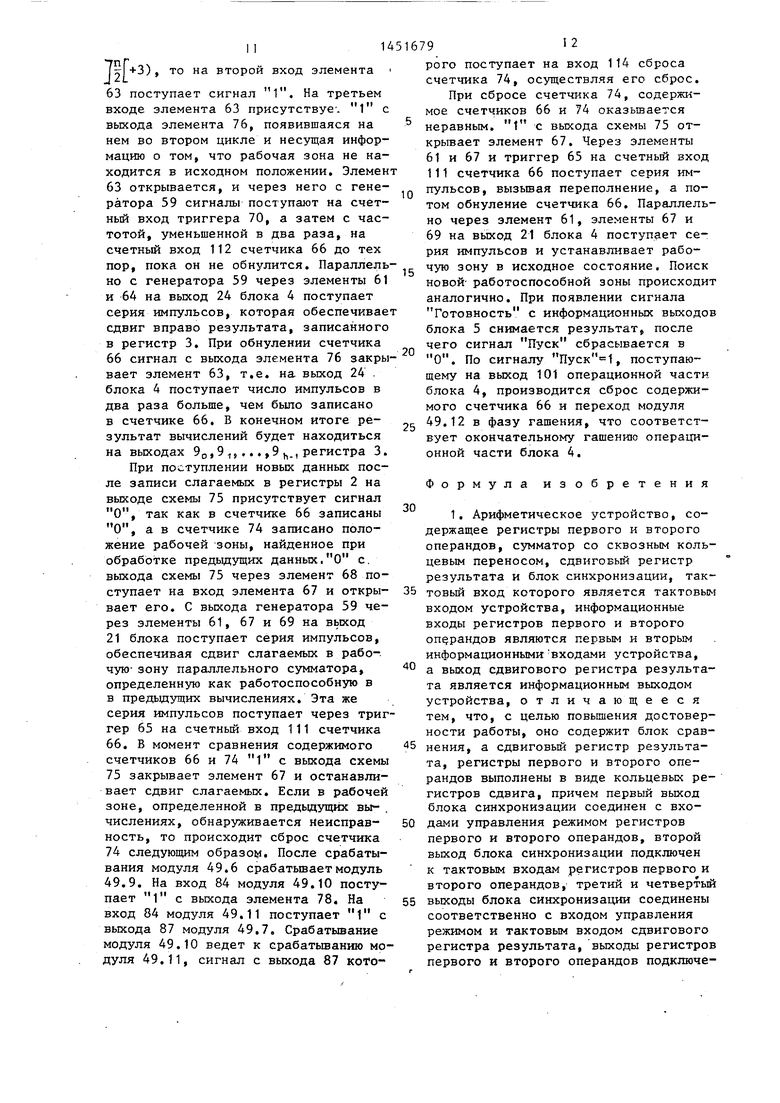

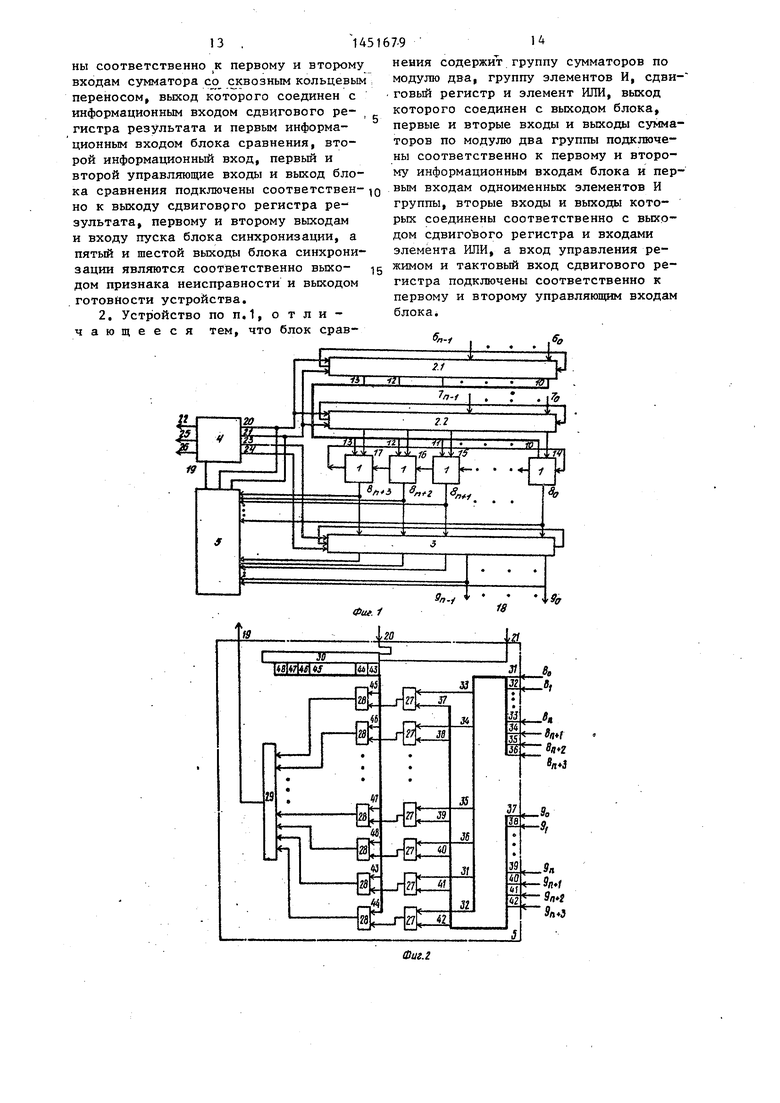

На фиг„1 представлена функциональная схема устройства, на фиг.2 -функ-Ю циональная схема блока сравнения, на фиг.З - функциональная схема блока синхронизациив на фиг.4 - функциональная схема управляющего модуля.

Устройство (фиг,1) содержит п+4 15 одноразрядных сумматора 1, объединенные в сумм атор со сквозным переносом, (п+4)-разрядные кольцевые сдвиговые регистры 2.1 и 2,2 первого и второго операндов, (п-ь4)-разрядный кольцевой 20 сдвиговый региетр 3 результата, блок 4 синхронизации и блок 5 сравнения. Входы 6о 9 6 5 6 f,i являются инфор- мационньши входами сдвигового регистра 2,1, входы 7о,7,...,7 ., являют- 25 ся информационными входами сдвигового регистра 2.2, Выходы 8 ,8, ,.. .8 . ,являются выходами (п+4)-разрядного параллельного сумматора со сквозным кольцевым переносом и соединены с 30 одноименными входами (п+4)-разрядного кольцевого сдвигового регистра 3 результата и одноименными входами блока 5 сравнения..Выходы 90,9,,..., 9 являются выходами (п+4)-разряд- ного сдвигового регистра 3 и соединены с одноименными входами блока 5 сравнения. Выходы 10-13 являются выходами сдвигового регистра 2.1 и соединены с первьп входами одноразряд- Q ных сумматоров 1. Выходы 14-17 сдвигового регистра 2,2 соединены с вторыми входами одноразрядных сумматоров 1, Выходы 9о,9,..,,9,., образуют информадионньш выход 18 устройства. дз Выход 19 является выходом блока 5 сравнения и соединен с соответствующим входом блока 4. Выходы 20 и 21 блока 4 соединены с входами управления режимом и тактовыми входами сдвиговых регистров 2.1 и 2.2и соответствующим входом блока 5 сравнения с Вход 22 является тактовым входом устройстваа на который подаются тактовые сигналы при пуске устройства. Вькод 23 блока 4 соединен с входом управления режимом сдвигового регистра 3, Выход 24 блока 4 соединен с тактовым входом сдвигового регистра

55

з

3, Выходы 25 и 26 являются управляющими выходами устройства, с которых снимаются соответственно сигналы Признак неисправности и Готовность результата.

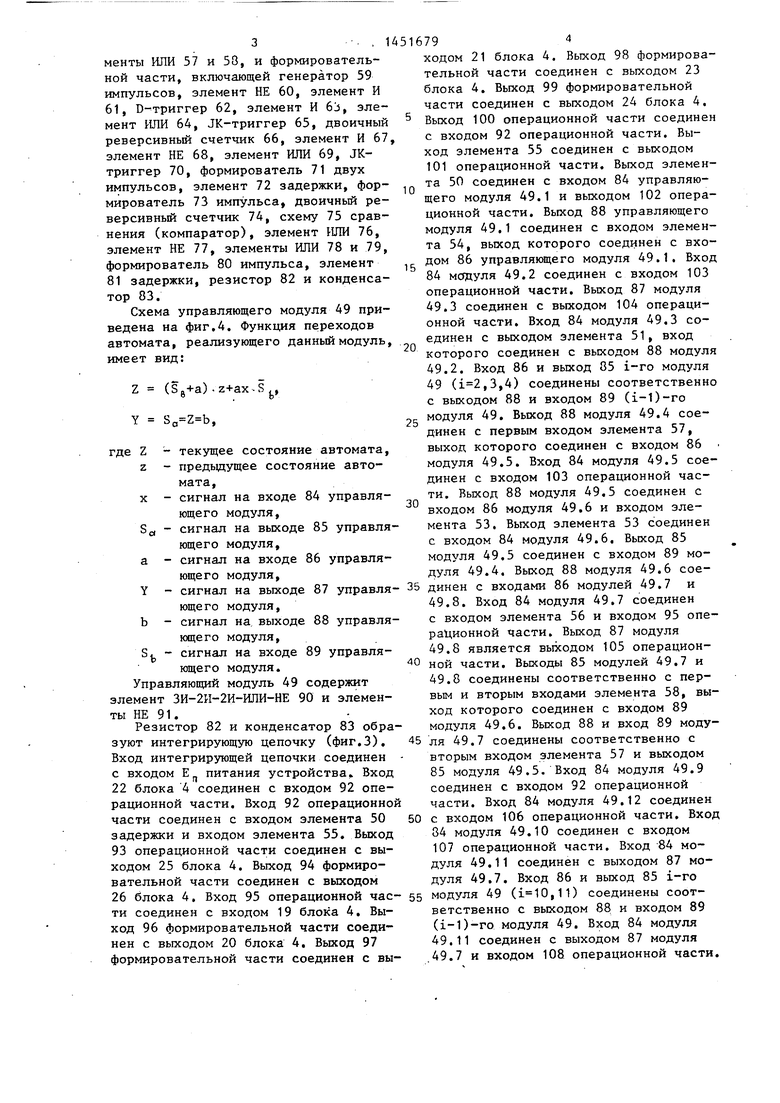

На фиг.2 представлена функциональная схема блока 5 сравнения, который содержит п+4 сумматора 27 по модулю два, п+4 элемента И 28, элемент ИЛИ 29, (п+4)-разрядный кольцевой сдвиговый регистр 30 (управления сравнением) , причем (п+4)-разрядный кольцевой сдвиговый регистр 2.1 первого операнда, (п+4)-разрядный кольцевой сдвиговый регистр 2,2 второго операнда, (ri+4)-разрядный кольцевой сдвиговый регистр 30 (управления.сравнением) , (п+4)-разрядный кольцевой сдвиговый регистр 3 результата аналогичны и представляют собой (п+4)- разрядные двунаправленные сдвиговые регистры,, в которых информационный вьгсод (п+4)-го (первого) разряда соединен с входом последовательного занесения информации при сдвиге влево (вправо).

Первый вход первой группы информационных входов блока 5 сравнения соединен с первым входом (п+3)-го элемента 27, второй вход первой группы информационных входов блока 5 соединен с первым входом (п+4)-го элемента 2.7, j-й вход (,4,...,п+4) первой группы информационных входов блока 5 соединен с первым входом (j-2)-ro элемента 27, выходы (п+4)-разрядного сдвигового регистра 3 соединены (в соответствии с весом) с второй .. группой информационных входов блока 5, j-й информационный вход (,2,o .,.,п+4) второй группы информационных входов бдока 5 соединен с вторым входом j-ro элемента 27, выход j-ro элемента 27 (,2,...,п+4) соединен с первым входом j-ro элемента 28, второй вход которого соединен с j-M (,4,...,п+4) выходом регистра 30, вторые входы (п+3)-го и (п+4)-го элементов 28 соединены соответственно с первым и вторым выходами (п+4)- разрядного регистра 30. Блок 5 имеет входы 31-42 и выходы 43-48 регистра 30.

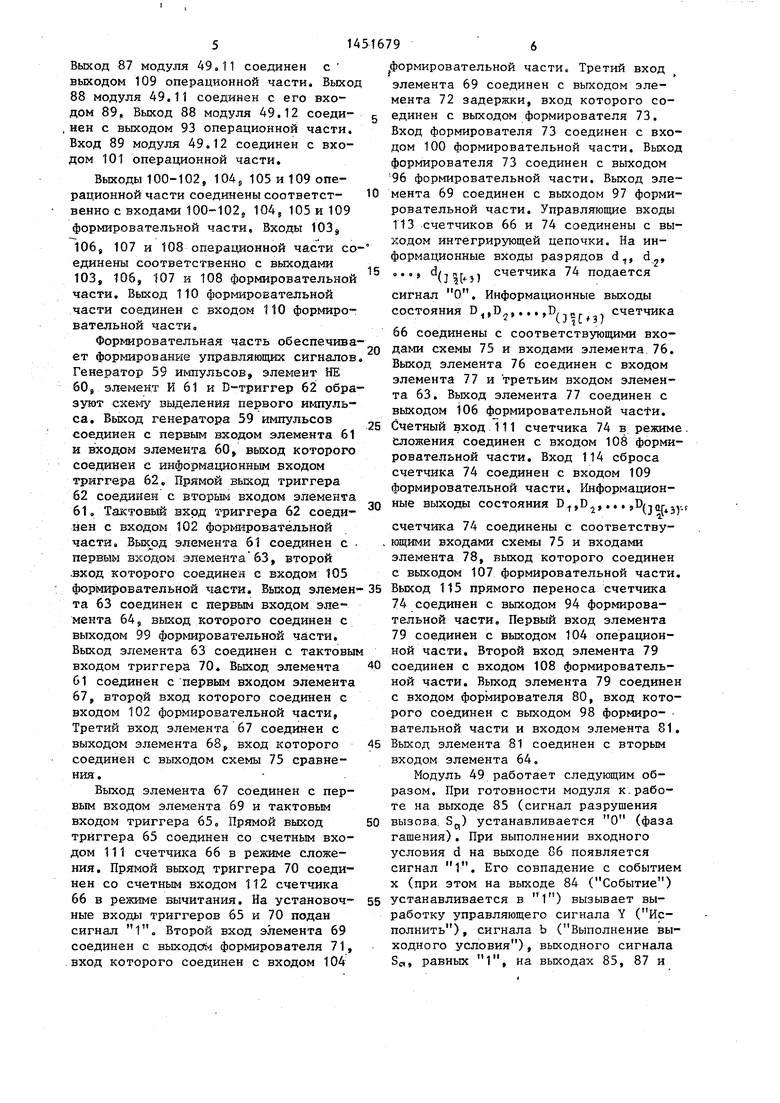

Блок 4 синхронизации (фиг.З) структурно состоит из двух частей: операг ционной части, содержащей управляющие модули 49.1-49.12, элементы 50- 53 задержки, элементы НЕ 54-56, эле5

менты ИЛИ 57 и 58, и формирователь- ной части, включающей генератор 59 импульсов, элемент НЕ 60, элемент И 61, D-триггер 62, элемент И 6J, элемент ИЛИ 64, JK-триггер 65, двоичный реверсивный счетчик 66, элемент И 67 элемент НЕ 68, элемент ИЛИ 69, JK- триггер 70, формирователь 71 двух импульсов, элемент 72 задержки, формирователь 73 импульса, двоичный реверсивный счетчик 74, схему 75 сравнения (компаратор), элемент ИЛИ 76, элемент НЕ 77, элементы ИЛИ 78 и 79, формирователь 80 импульса, элемент 81 задержки, резистор 82 и конденсатор 83.

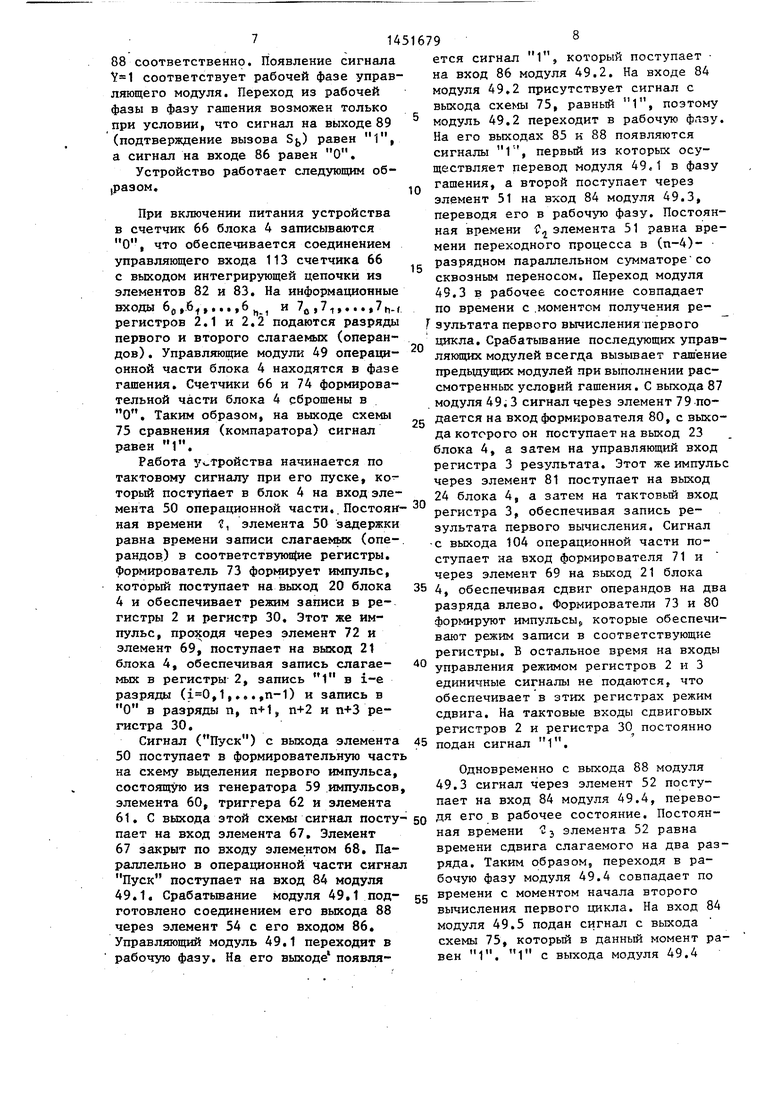

Схема управляющего модуля 49 приведена на фиг.4. Функция переходов автомата, реализующего данный модуль, имеет вид:

Z (Sg+a)-z+ax-S Y ,

Ь

где Z - текущее состояние автомата, Z - предьщущее состояние автомата,

X - сигнал на входе 84 управляющего модуля,

Set - сигнал на выходе 85 управляющего модуля,

а - сигнал на входе 86 управляющего модуля,

Y - сигнал на выходе 87 управляющего модуля,

b - сигнал на, выходе 88 управляющего модуля,

S, - сигнал на входе 89 управляющего модуля.

Управляющий модуль 49 содержит элемент ЗИ-2И-2И-ИЛИ-НЕ 90 и элементы НЕ 91.

Резистор 82 и конденсатор 83 образуют интегрирующую цепочку (фиг.З). Вход интегрирующей цепочки соединен - с входом Е питания устройства Вход 22 блока 4 соединен с входом 92 операционной части. Вход 92 операционной части соединен с входом элемента 50 задержки и входом элемента 55. Выход 93 операционной части соединен с выходом 25 блока 4. Выход 94 формиро- вательной части соединен с выходом

84 мсщуля 49.2 соединен с входом 103 операционной части. Выход 87 модуля 49.3 соединен с выходом 104 операционной части. Вход 84 модуля 49.3 соединен с выходом элемента 51, вход которого соединен с выходом 88 модул 49.2. Вход 86 и выход 85 i-ro модуля 49 (,3,4) соединены соответственн с выходом 88 и входом 89 (i-l)-ro модуля 49. Выход 88 модуля 49.4 соединен с первым входом элемента 57, выход которого соединен с входом 86 модуля 49.5. Вход 84 модуля 49.5 сое динен с входом 103 операционной части. Выход 88 модуля 49.5 соединен с входом 86 модуля 49.6 и входом элемента 53. Выход элемента 53 соединен с входом 84 модуля 49.6. Выход 85 модуля 49.5 соединен с входом 89 модуля 49.4. Выход 88 модуля 49.6 соединен с входами 86 модулей 49.7 и 49.8. Вход 84 модуля 49.7 соединен с входом элемента 56 и входом 95 опе рационной части. Выход 87 модуля 49.8 является выходом 105 операционной части. Выходы 85 модулей 49.7 и 49.8 соединены соответственно с первым и вторым входами элемента 58, вы ход которого соединен с входом 89 модуля 49.6. Выход 88 и вход 89 моду

45 ля 49.7 соединены соответственно с вторым входом элемента 57 и выходом 85 модуля 49.5. Вход 84 модуля 49.9 соединен с входом 92 операционной части. Вход 84 модуля 49.12 соединен с входом 106 операционной части. Вхо 84 модуля 49.10 соединен с входом 107 операционной части. Вход 84 модуля 49.11 соединен с выходом 87 мо дуля 49.7. Вход 86 и выход 85 i-ro

30

35

40

50

TC.J.J. V l V- Atil.l « V- . . ,, .

26 блока 4. Вход 95 операционной час- 55 модуля 49 (,11) соединены соотти соединен с входом 19 блока 4. Выход 96 формировательной части соединен с выходом 20 блока 4. Выход 97 формировательной части соединен с выветственно с выходом 88 и входом 89 (i-l)-ro модуля 49. Вход 84 модуля 49.11 соединен с выходом 87 модуля 49.7 и входом 108 операционной част

, ,

10

20

25

- йходом 21 блока 4. Выход 98 формирова- тельной части соединен с выходом 23 блока 4. Выход 99 формировательной части соединен с выходом 24 блока 4, Вьгход 100 операционной части соединен с входом 92 операционной части. Выход элемента 55 соединен с выходом 101 операционной части. Выход элемента 50 соединен с входом 84 управляющего модуля 49.1 и выходом 102 операционной части. Выход 88 управляющего модуля 49.1 соединен с входом элемента 54, выход которого соединен с входом 86 управляющего модуля 49.1. Вход

84 мсщуля 49.2 соединен с входом 103 операционной части. Выход 87 модуля 49.3 соединен с выходом 104 операционной части. Вход 84 модуля 49.3 соединен с выходом элемента 51, вход которого соединен с выходом 88 модуля 49.2. Вход 86 и выход 85 i-ro модуля 49 (,3,4) соединены соответственно с выходом 88 и входом 89 (i-l)-ro модуля 49. Выход 88 модуля 49.4 соединен с первым входом элемента 57, выход которого соединен с входом 86 модуля 49.5. Вход 84 модуля 49.5 соединен с входом 103 операционной части. Выход 88 модуля 49.5 соединен с входом 86 модуля 49.6 и входом элемента 53. Выход элемента 53 соединен с входом 84 модуля 49.6. Выход 85 модуля 49.5 соединен с входом 89 модуля 49.4. Выход 88 модуля 49.6 соединен с входами 86 модулей 49.7 и 49.8. Вход 84 модуля 49.7 соединен с входом элемента 56 и входом 95 операционной части. Выход 87 модуля 49.8 является выходом 105 операционной части. Выходы 85 модулей 49.7 и 49.8 соединены соответственно с первым и вторым входами элемента 58, выход которого соединен с входом 89 модуля 49.6. Выход 88 и вход 89 моду45 ля 49.7 соединены соответственно с вторым входом элемента 57 и выходом 85 модуля 49.5. Вход 84 модуля 49.9 соединен с входом 92 операционной части. Вход 84 модуля 49.12 соединен с входом 106 операционной части. Вход 84 модуля 49.10 соединен с входом 107 операционной части. Вход 84 модуля 49.11 соединен с выходом 87 модуля 49.7. Вход 86 и выход 85 i-ro

30

35

40

50

. . ,, .

модуля 49 (,11) соединены соответственно с выходом 88 и входом 89 (i-l)-ro модуля 49. Вход 84 модуля 49.11 соединен с выходом 87 модуля 49.7 и входом 108 операционной части.

10

15

51451679

Выход 87 модуля 49,11 соединен с выходом 109 операционной части. Выход 88 модуля 49,11 соединен с его входом 89, Выход 88 модуля 49.12 соеди- ней с выходом 93 операционной части. Вход 89 модуля 49,12 соединен с вхоом 101 операционной части.

Выходы 100-102, 104f, 105 и 109 операционной части соединены соответственно с входами 100-1025 104s 105 и 109 формировательной части. Входы 103

106, 107 и 108 операционной части со-° единены соответственно с выходами 103, 106, 107 и 108 формировательной части. Выход 110 формировательной части соединен с входом tlO формировательной части,

Формировательная часть обеспечивает формирование управляющих сигналов. Генератор 59 импульсов, элемент НЕ

60,элемент И 61 и В-триггер 62 образуют схемз выделения первого импульса. Выход генератора 59 импульсов соединен с первым входом элемента 61 и входом элемента 60, выход которого соединен е информационным входом триггера 62, Прямой выход триггера

62 соединен с вторым входом элемента

61,Тактовый вход триггера 62 соединен с входом 102 форм1 роватёльной части, Выход элемента 61 соединен с первым вкодом. элемента 63, второй .вход которого соединен с входом 105

фо эл ме ед Вх до 96 ме ро хо

20

си со

да эл та вы 25 Сч Сл ро сч ны

сч ющ эл с

30

формировательной части. Третий вход элемента 69 соединен с выходом элемента 72 задержки, вход которого соединен с выходом формирователя 73, Вход формирователя 73 соединен с входом 100 формировательной части. Выход формирователя 73 соединен с выходом 96 формировательной части. Выход элемента 69 соединен с выходом 97 формировательной части. Управляющие входы 113 счетчиков 66 и 74 соединены с выходом интегрирующей цепочки. На информационные входы разрядов d

т

()

счетчика 74 подается

сигнал О . Информационные выходы состояния D ,D ,,,,,D, „ счетчика

(.

66 соединены с соответствуюпщми входами схемы 75 и входами элемента. 76, Выход элемента 76 соединен с входом элемента 77 и третьим входом элемента 63, Выход элемента 77 соединен с выходом 106 фррмировательной чactи, Счетный вход 111 счетчика 74 в режиме. Сложения соединен с входом 108 формировательной части. Вход 114 сброса счетчика 74 соединен с входом 109 формирозательной части. Информационные выходы состояния DI,D.J, .. . j..p

счетчика 74 соединены с соответствующими входами схемы 75 и входами элемента 78, выход которого соединен с выходом 107 формировательной части.

| название | год | авторы | номер документа |

|---|---|---|---|

| Центральный процессор | 1980 |

|

SU890400A1 |

| Процессор | 1984 |

|

SU1200294A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Устройство для выполнения операций умножения и деления | 1986 |

|

SU1403061A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

Изобретение относится к области цифровой вычислительной техники и предназначено для использования в универсальных и специализированных вычислительных устройствах. Целью изобретения является повьшение достоверности работы устройства. С этой целью в устройство, содержащее ре гистр первого операнда, регистр второго операнда, сумматор со сквозным переносом, сдвиговый регистр результата и блок синхронизации, введен блок сравнения, а сдвиговый регистр результата, регистр первого операнда и регистр второго операнда выполнены в виде циклических регистров сдвига, причем блок сравнения содержит группу сумматоров по модулю два, группу элементов И, сдвиговый регистр и элемент ИЛИ. 1 з.п.ф-лы, 4 ил. (Л

формировательной части. Выход элемен-35 Выход 115 прямого переноса счетчика та 63 соединен с первым входом эле 74 соединен с выходом 94 формировамента 64, выход которого соединен с выходом 99 формировательной части. Выход элемента 63 соединен с тактовы входом триггера 70. Выход элемента 61 соединен с первым входом элемента 67, второй вход которого соединен с входом 102 формировательной части, Третий вход элемента 67 соединен с выходом элемента 68, вход которого соединен с выходом схемы 75 сравнения.

Выход элемента 67 соединен с первым входом элемента 69 и тактовым

входом триггера 65„ Прямой выход триггера 65 соединен со счетным входом 111 счетчика 66 в режиме сложения. Прямой выход триггера 70 соединен со счетным входом 112 счетчика 66 в режиме вычитания. На установочные входы триггеров 65 и 70 подан сигнал 1. Второй вход элемента 69 соединен с выходов формирователя 71, вход которого соединен с входом 104

0

0

тельной части. Первый вход элемента 79 соединен с выходом 104 операционной части. Второй вход элемента 79 соединен с входом 108 формировательной части. Выход элемента 79 соединен с входом формирователя 80, вход которого соединен с выходом 98 формиро- вательной части и входом элемента 81.

5 Выход элемента 81 соединен с вторым входом элемента 64.

Модуль 49 работает следующим образом. При готовности модуля к.работе на выходе 85 (сигнал разрушения вызова, Sj,) устанавливается О (фаза гашения), При выполнении входного условия d на выходе 86 появляется сигнал 1. Его совпадение с событием X (при этом на выходе 84 (Событие)

5 устанавливается в 1) вызывает выработку управляющего сигнала Y (Исполнить) , сигнала b (Выполнение выходного условия), выходного сигнала Sd, равных 1, на выходах 85, 87 и

88 соответственно. Появление сигнала соответствует рабочей фазе управляющего модуля. Переход из рабочей фазы в фазу гашения возможен только при условии, что сигнал на выходе 89 (подтверждение вызова Sj,) равен 1, а сигнал на входе 86 равен О.

Устройство работает следующим об- (Раэом.

При включении питания устройства в счетчик 66 блока 4 записываются О, что обеспечивается соединением управляющего входа 113 счетчика 66 с выходом интегрирующей цепочки из элементов 82 и 83. На информационные входы 6д 6,,,, ,6 и 7д ,7,,. .,7., регистров 2.1 и 2.2 подаются разряды первого и второго слагаемых (операндов) . Управляющие модули 49 операционной части блока 4 находятся в фазе гашения. Счетчики 66 и 74 формирова- тельной части блока 4 сброшены в О. Таким образом, на выходе схемы 75 сравнения (компаратора) сигнал равен 1.

Работа устройства начинается по тактовому сигналу при его пуске, который поступает в блок 4 на вход элемента 50 операционной части. Постояк ная времени , элемента 50 задержки равна времени записи слагаемых (oneрандов) в соответствуюп{ие регистры. Формирователь 73 формирует импульс, который поступает на выход 20 блока 4 и обеспечивает режим записи в регистры 2 и регистр 30. Этот же импульс, проходя через элемент 72 и элемент 69, поступает на выход 21 блока 4, обеспечивая запись слагаемых в регистры- 2, запись 1 в i-е разряды (,1,.,.,п-1) и запись в О в разряды п, n+l, п+2 и п+3 регистра 30.

Сигнал (Пуск) с выхода элемента 50 поступает в формировательную част на схему вьщеления первого импульса, состоящую из генератора 59 импульсов элемента 60, триггера 62 и элемента 61. С выхода этой схемы сигнал посту пает на вход элемента 67. Элемент 67 закрыт по входу элементом 68, Параллельно в операционной части сигна Пуск поступает на вход 84 модуля 49.1, Срабатьшание модуля 49,1 под- готовлено соединением его выхода 88 через элемент 54 с его входом 86, Управляющий модуль 49.1 переходит в рабочую фазу. На его выходе появля

10

15

20

25

50 55

1679

ется сигнал 1, который поступает на вход 86 модуля 49.2. На входе 84 модуля 49.2 присутствует сигнал с выхода схемы 75, равный 1, поэтому модуль 49.2 переходит в рабочую фазу. На его выходах 85 и 88 появляются сигналы , первый из которых осуществляет перевод модуля 49И в фазу гашения, а второй поступает через элемент 51 на вход 84 модуля 49.3, переводя его в рабочую фазу. Постоянная времени 0 элемента 51 равна времени переходного процесса в (п-4)- разрядном параллельном сумматоре со сквозным переносом. Переход модуля 49.3 в рабочее состояние совпадает по времени с .моментом получения ре- Г зультата первого вычисления первого цикла. Срабатьтание последующих управляющих модулей всегда вызывает гашение предьщу Цих модулей при выполнении рассмотренных услоеий гашения. С выхода 87 модуля 49.3 сигнал через элемент 79 подается на вход формирователя 80, с выхода которого он поступает на выход 23 блока 4, а затем на управляющий вход регистра 3 результата. Этот же импульс через элемент 81 поступает на выход 24 блока 4, а затем на тактовый вход регистра 3, обеспечивая запись результата первого вычисления. Сигнал с выхода 104 операционной части поступает на вход формирователя 71 и через элемент 69 на выход 21 блока 4, обеспечивая сдвиг операндов на два разряда влево. Формирователи 73 и 80 формируют импульсы которые обеспечивают режим записи в соответствующие регистры. В остальное время на входы управления режимом регистров 2 и 3 единичные сигналы не подаются, что обеспечивает в этих регистрах режим сдвига. На тактовые входы сдвиговых регистров 2 и регистра 30 постоянно подан сигнал 1.

35

40

45

Одновременно с выхода 88 модуля 49.3 сигнал через элемент 52 поступает на вход 84 модуля 49.4, переводя его в рабочее состояние. Постоянная времени С э элемента 52 равна времени сдвига слагаемого на два разряда. Таким образом, переходя в рабочую фазу модуля 49.4 совпадает по времени с моментом начала второго вычисления первого цикла. На вход 84 модуля 49.5 подан сигнал с выхода схемы 75, который в данный момент равен 1. 1 с выхода модуля 49.4

145167910

49,7, модуль срабатывает и формирует . сигнал, который увеличивает содержимое счетчика 74 и параллельно через элемент 79 поступает на вход формирователя 80. Сигнал с выхода формирователя 80 поступает на выход 23 блока 4 и через элемент 81 на выход 24 блока 4 и аналогично описанному обеспечивает запись результата второго вычисления в регистр 3, первьш результат при этом теряется,

При увеличении содержимого счетчика 74 возникает рассогласование с

10

через элемент 57 поступает на вход 86 модуля 49.5 и обеспечивает его срабатывание. 1 с выхода 88 модуля 49,5 поступает на вход 86 и через элемент 53 на вход 84 модуля 49,6, обеспечивая его срабатьгоание. Постоянная времени f4 элемента 53 равна ti - ij+t,, где t - время сравнения результатов вычислений в блоке 5, Срабатьшание модуля 49,6 совпадает по времени с моментом окончания второго вычисления и первого цикла.

После окончания первого цикла, который содержит два вычисления, выпол- i содержимым счетчика 66 и на выходе ненных в рабочей зоне (п+4)-разряд- схемы 75 появляется О, которьш некого параллельного сумматора, различающихся по положению в сумматоре на два разряда, получают два результата, первый из которых записан в регистре JQ 3, а второй находится на выходах 80, 8,,.,,8, параллельного сумматора. На выходах 44, 43, 47 и 48 регистра 30 после первого цикла вычислений находятся О. Эти О .блокируют по вы- 25 тотой поступают на вход 111 счетчика ходам первьш, второй, (п+3)-й и 66, Когда содержимое счетчика 66 уве- (п+4)-й элементы 28, что обеспечи- личивается на единицу, то рассогласо- вает сравнение результата только в «« «ЯУ счетчиками 66 и 74 исче- пределах рабочей зоны,- соответствующей первому циклу вычислений, ЗО

Если результаты вычислений совпали, на выходе 19 блока 5 сравнения через время t присутствует сигнал, равный О, Он поступает в операционную часть блока 4 на вход элемента 56, выход которого соединен с входом 84 модуля 49,8, На вход 86 модуля 49,8 с выхода 88 модуля 49,6 подан сигнал 1, который вызьшает его сра40

сет информацию о неготовнос1и рабочей зоны. Этот сигнал, проходя через элемент 68, открывает элемент 67,

Р1мпульсы генератора 59 через схему выделения первого импульса, элементы 61 и 67 поступают на счетный вход триггера 65. С выхода триггера 65 импульсы в два раза меньшей часзает. На выходе схемы 75 появляется сигнал 1, который закрывает элемент

батывание. Сигнал с выхода 87 модуля 49.8 поступает на второй вход элемента 63. Элемент 63 блокирован О с

67, Единица 1 с выхода схемы 75 поступает на вход 88 модуля 49.5 и обеспечивает его срабатывание. Через время- ii срабатьшает модуль 49,6. Этот момент времени совпадает с временем окончания второго цикла, которое состоит из одного вычисления. Отличие второго и последующих циклов от первого состоит в том, что для сравнения используется результат, полученный в предьщущем цикле.

После окончания второго цикла блок 5 осуществляет сравнение результатов вычислений. Если результаты не совпаПосле окончания второго цикла блок 5 осуществляет сравнение результатов вычислений. Если результаты не совпавыхода элемента 76, так как на выходе

счетчика 66, записывающем информацию

о положении рабочей зоны относитель- дают, осуществляется сдвиг слагаемых

но исходного положения, находятся следующий цикл вычислений, и так

до тех пор, пока результаты не совпадут. Если число циклов вычислений, записываемых в счетчике 74, превышает

О. С выхода элемента 77, вход которого соединен с элементом 76, снимается сигнал, который несет информацию о том, в пределах каких разрядов регистра 3 находится результат вычислений. Он подается на вход 84 модуля i49,12, срабатывание которого форми- |рует сигнал Готовность результата.

Если результаты не совпадают вследствие неисправности в параллельном сумматоре, с выхода 19 блока 5 через время ,t, снимается сигнал, равный Он подается на вход 84 модуля

50 , что соответствует всем возможным положениям рабочей зоны параллельного сумматора, то в этом случае на выходе 115 счетчика 74 появляется 1, которая поступает на выход 25 блока 4 и является сигналом Признак неисправности,

Если результаты вычислений в i-м цикле вычислений совпали (,2,.,.,.

содержимым счетчика 66 и на выходе схемы 75 появляется О, которьш нетотой поступают на вход 111 счетчика 66, Когда содержимое счетчика 66 уве- личивается на единицу, то рассогласо- «« «ЯУ счетчиками 66 и 74 исче-

сет информацию о неготовнос1и рабочей зоны. Этот сигнал, проходя через элемент 68, открывает элемент 67,

Р1мпульсы генератора 59 через схему выделения первого импульса, элементы 61 и 67 поступают на счетный вход триггера 65. С выхода триггера 65 импульсы в два раза меньшей чассодержимым счетчика 66 и на выходе схемы 75 появляется О, которьш нетотой поступают на вход 111 счетчика 66, Когда содержимое счетчика 66 уве- личивается на единицу, то рассогласо- «« «ЯУ счетчиками 66 и 74 исче-

зает. На выходе схемы 75 появляется сигнал 1, который закрывает элемент

содержимым счетчика 66 и на выходе схемы 75 появляется О, которьш нетотой поступают на вход 111 счетчика 66, Когда содержимое счетчика 66 уве- ичивается на единицу, то рассогласо- «« «ЯУ счетчиками 66 и 74 исче-

67, Единица 1 с выхода схемы 75 поступает на вход 88 модуля 49.5 и обеспечивает его срабатывание. Через время- ii срабатьшает модуль 49,6. Этот момент времени совпадает с временем окончания второго цикла, которое состоит из одного вычисления. Отличие второго и последующих циклов от первого состоит в том, что для сравнения используется результат, полученный в предьщущем цикле.

После окончания второго цикла блок 5 осуществляет сравнение результатов вычислений. Если результаты не совпа1 Г+3, что соответствует всем возможным положениям рабочей зоны параллельного сумматора, то в этом случае на выходе 115 счетчика 74 появляется 1, которая поступает на выход 25 блока 4 и является сигналом Признак неисправности,

Если результаты вычислений в i-м цикле вычислений совпали (,2,.,.,.

Ту|+3), то на второй вход элемента

63 поступает сигнал 1. На третьем входе элемента 63 присутствуе-. 1 с выхода элемента 76, появившаяся на нем во втором цикле и несущая информацию о том, что рабочая зона не находится в исходном положении. Элемен 63 открывается, и через него с генератора 59 сигналы поступают на счетный вход триггера 70, а затем с частотой, уменьшенной в два раза, на счетный вход 112 счетчика 66 до тех пор, пока он не обнулится. Параллельно с генератора 59 через элементы 61 и 6А на выход 24 блока 4 поступает серия импульсов, которая обеспечивае сдвиг вправо результата, записанного в регистр 3, При обнулении счетчика 66 сигнал с выхода элемента 76 закрывает элемент 63, т.е. на выход 24 . блока 4 поступает число импульсов в два раза больше, чем было записано в счетчике 66. В конечном итоге результат вычислений будет находиться на выходах 9,9 „.. .,9 ., регистра 3. При поступлении новых данных после записи слагаемьпс в регистры 2 на выходе схемы 75 присутствует сигнал О, так как в счетчике 66 записаны О, а в счетчике 74 записано положение рабочей зоны, найденное при обработке предыдущих данных.О с. выхода схемы 75 через элемент 68 поступает на вход элемента 67 и открывает его. С выхода генератора 59 через элементы 61, 67 и 69 на вькод 21 блока поступает серия импульсов, обеспечивая сдвиг слагаемых в рабочую- зону параллельного сумматора, определенную как работоспособную в в предыдущих вычислениях. Эта же серия импульсов поступает через триггер 65 на счетный вход 111 счетчика 66. В момент сравнения содержимого счетчиков 66 и 74 1 с выхода схемы 75 закрывает элемент 67 и останавливает сдвиг слагаемых. Если в рабочей зоне, определенной в предьщущих вы-, числениях, обнаруживается Неисправность, то происходит сброс счетчика 74 следующим образом. После срабатывания модуля 49.6 срабатьшаетмодуль 49.9. На вход 84 модуля 49.10 поступает 1 с выхода элемента 78. На вход 84 модуля 49.11 поступает 1 с выхода 87 модуля 49.7. Срабатывание модуля 49.10 ведет к срабатыванию модуля 49.11, сигнал с выхода 87 коТо

5

0

5

рого поступает на вход 114 сброса счетчика 74, осуществляя его сброс. При сбросе счетчика 74, содержимое счетчиков 66 и 74 оказьшается неравным, t с выхода схемы 75 открывает элемент 67. Через элементы 61 и 67 и триггер 65 на счетньй вход 111 счетчика 66 поступает серия импульсов, вызьшая переполнение, а потом обнуление счетчика 66. Параллельно через элемент 61, элементы 67 и 69 на выход 21 блока 4 поступает серия импульсов и устанавливает рабочую зону в исходное состояние. Поиск новой- работоспособной зоны происходит аналогично. При появлении сигнала Готовность с информационных выходов блока 5 снимается результат, после чего сигнал Пуск сбрасывается в О. По сигналу , поступающему на выход 101 операционной части блока 4, производится сброс содержимого счетчика 66 и переход модуля 49.12 в фазу гащения, что соответствует окончательному гашению операционной части блока 4.

Формула изобретения

ности работы, оно содержит блок срав- нения, а сдвиговый регистр результата, регистры первого и второго операндов выполнены в виде кольцевых регистров сдвига, причем первый выход блока синхронизации соединен с вхо- дами управления режимом регистров первого и второго операндов, второй выход блока синхронизации подключен к тактовым входам регистров первого и второго операндов, третий и четвертый выходы блока синхронизации соединены соответственно с входом управления режимом и тактовым входом сдвигового регистра результата, выходы регистров первого и второго операндов подключе13

ны соответственно к первому и второму входам сумматора со сквозным кольцевым переносом, выход которого соединен с информационным входом сдвигового ре- , гистра результата и первым информационным входом блока сравнения, второй информационньпй вход, первый и второй управляющие входы и выход блока сравнения подключены соответственно к выходу сдвиговрго регистра результата, первому и второму выходам и входу пуска блока синхронизации, а пятый и шестой выходы блока синхронизации являются соответственно выхо- дом признака неисправности и выходом готовности устройства.

2, Устройство по п.1, о т л и - чающееся тем, что блок срав , Q5

5167-9 1

нения содержит группу сумматоров по модулю два, группу элементов И, сдвиговый регистр и элемент ИЛИ, выход которого соединен с выходом блока, первые и вторые входы и выходы сумматоров по модулю два группы подключены соответственно к первому и второму информационным входам блока и первым входам одноименных элементов И группы, вторые входы и выходы которых соединены соответственно с выходом сдвигового регистра и входами элемента ИЛИ, а вход управления режимом и тактовый вход сдвигового регистра подключены соответственно к первому и второму управляющим входам блока.

5 Л-/

dS

69

дб

&7

90

68

ФигЛ

| Хетагуров Я.А | |||

| и др | |||

| Основы инженерного проектирования управляющих ЦВМ | |||

| - М.: Сов.радио, 1972, с.113 | |||

| Клингман Э | |||

| Проектирование специализированных микропроцессорных систем | |||

| - М.: Мир, 1985, с.с.47-56, рис.2.8, табл.2.6-2.8. |

Авторы

Даты

1989-01-15—Публикация

1986-04-07—Подача