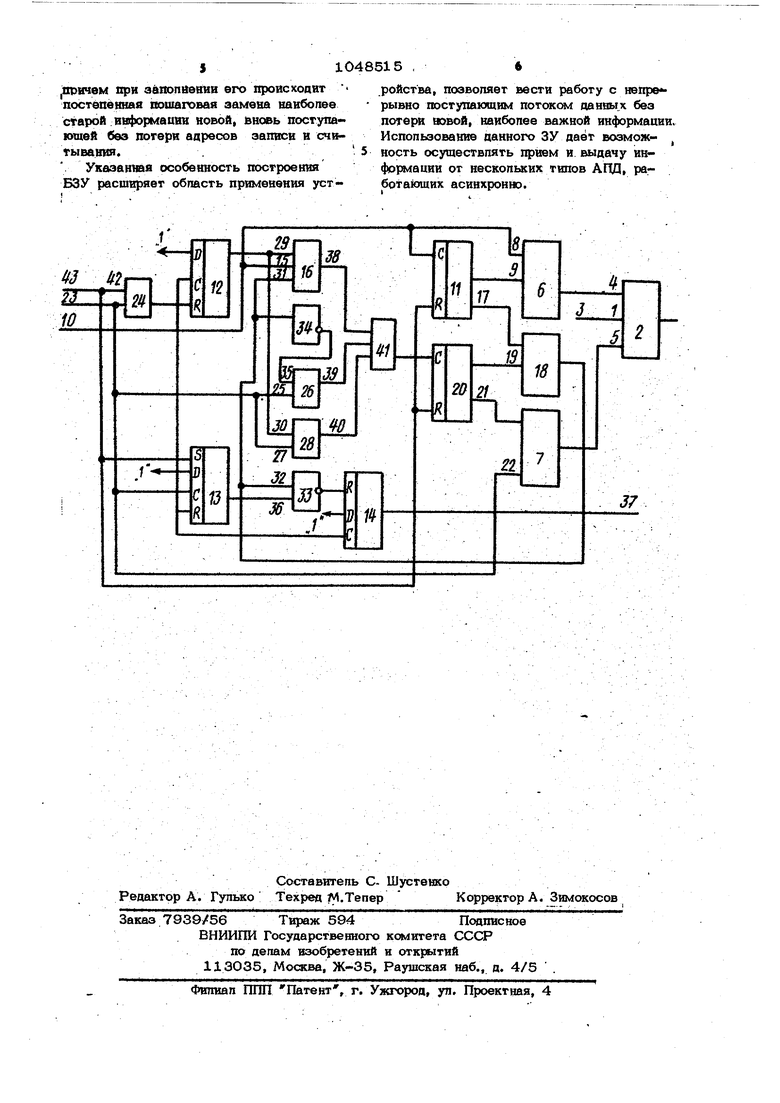

11 изобретение относится к запоми1шк щим устройствам и может быть использовано в системах приема и передачи дис кретной информации. Известно буферное запоминающее устрьйство (БЗУ), содержащее накопитель, блоки формирования адресов записи и считывания, схему сравнения адресов записи и считывания, элементы И и ИЛИ в котором индикация занятости осуществляется путем сравнения адресов записи и считывания l . Недостатком этого БЗУ является прекращение записи новой информации при заполнении наколителя. Наиболее близким по технической сущности к изобретению является буферное запоминающее устройство, содержащее накопитель, счетчик записи, счетчик сч тывания, схемь сравнения, элементы И и ИЛИ, триггеры и дешифрато{И)1. После заполнения накопитегш (достижения счетчиком записи максимального значения), формируетсясигнал переполнения.И запись вновь поступающей информации прекращается. Потери адреса записи .при неравномерном поступлении сигналов . записи и считывания не происходит 2, Недостатком такого устройства является потеря новой, наиболее важной информации при ее непрерывном дальнейшем поступлении. Целью изобретения является расширение области применения за счет запоминания информации, поступающей после переполнения накопителя. Поставлейная цель достигается тем, что в буферном запоминающем устройстве содержащем Накопитель, информационные входы и вы ходы которого являются соответственно информационными входами и выходами устройства, первый и второй адресные входы накопителя подключены к выходам соответственно первого и второго дешифраторов, первые входы первого и второго дешифраторов являются соответственно первым и вторым управля ющими входами устройства, второй вход первого дешифратора подключен к первому выходу первого счетчика, второй вход второго подключен к первому выходу второгчэ счетчика, вторые выходы первого и второго счетчиков подклк чены к входам блока сравнения, тактовый вход первого счетчика подключен к перво му входу первого дешифратора, триггеры, элементы И, элементы ИЛИ, элемент ИНЕ и элемент НЕ, тактовый вход второго счетчика подключен к выходу первого эле 15 мента ИЛИ, первый вход которого подключен к выходу первого элемента И, второй и третий входы первого элемента ИЛИ подключены к выходам соответственно второго и третьего элементов И, входы которых подключены к первому входу второго элемента ИЛИ и к первому входу второго дешифратора, второй вход второго элемента И подключен к выходу элемента НЕ, вход которого подключен к выходу блока сравнения, к первому входу четвертого элемента И и к первому входу первого элемента И, второй вход которого подключен к выходу первоготриггера и -к второму входу третьего элемента И, третий вход первого элемента И подключен к тактовым входам nej вого и третьего триггеров, /к сбросовому входу второго триггера и к тактовому входу первого счетчика, второй вход второго элемента ИЛИ является третьим управляющим входом устройства и подключен к установочному входу второго триггера, к сбросовым входам первого и второго счетчиков, выход второго элемента ИЛИ подключен к сбросовому входу первого триггера, выход третьего триггера является управляющим выходом устройства. На чертеже, приведена структурная схема предл,агаемого устройства. Устройство содержит инфо|ыационный вход 1 накопителя 2, информационный вход 3 устройства, управляющие входы 4 и 5 накопителя 2, дешифраторы 6 и 7, входы 8 и 9 дешифратора б, управтмющий вход 1.0, счетчик 11, триггеры 12-14, вход 15 элемента И 16, выход 17 счетчика 11, блок 18 сравнения, вход 19 блока 18 сравнения, счетчик 2О, выход 21 счетчика 20, вход 22 дешифратора 7, управляющий вход 23, элемент ИЛИ 24, вход 25 элемента И 26, вход 27 элемента И 28, выход первого триггера 12, подключенный к входу 28 элемента И 16,, вход 30 элемента И 28, вход 31 элемента И 16,- вход 32 элемента И-НЕ 33, элемент НЕ 34, вход 35 элемента И 26, вход 36 элемента И 33, управляющий выход 37, выходы 38-40 элементов И, элемент ИЛИ 4-1, вход 42 элемента ИЛИ 24 и управляющий вход 43 устройства. Работа устройства происходит следукущим образом. В исходный момент после воздействия сигнала начальной установки (НУ), поступйкшего на вход 43, триггеры 12 и 14, счетчики 11 и 20 находятся в нуле31BOM, a триггер 13 - в единичном состоя НИИ. При одинаковых состояниях счетчиков 11. и 20 на выходе бпока 18 сравнения устанавливается высокий потенциал. Сигнал, поступающий с выхода блока 18 сравнения через элемент НЕ 34 на вход 35 элемента И 26, запрещает прохождение импульсов считывания через элемент И 26 и далее через элемент ИЛИ 41 на тактовый вход счетчика 20, определяющего адрес считывания, до npit,хода первого импульса, записи. Сигнал с выхода- триггера 12, поступающий на вход ЗО элемента И 28, также запрещает прохождение импульса считывания на вход счетчика 20 до прихода сигна1ла записи. После первого тлпупьса записи состоя ние счетчика 11 изменяется, и на выходе блока 18 сравнения формируется низкий потенциал, инверсное значение котррого разрешает прохождение сигнала считывания через элемент И 26, элемент ИЛИ 41 на тактовый вход счетчи-f ка 2О. По первому импульсу записи триггер 1 12 устанавливается в; единичнре состоя- ние, триггер 13 устанавливается в нулевое состояние, разрешая тем самым работу триггера 14, по концу импульсов записи на выходе триггера 14 формируется сигнал наличия информации. Сигнал считывания, поступающий на вход 23, изменяет состояние триггеров 12 и 13 и счетчика 2О считывания. На вход счетчика 20 сигнал считывания п ступает через элемент И 26 и элемент ИЛИ 41. Триггер 12 устанавливается в нулевое состояние по началу сигнала считывания, а триггер 13 в единичное состояние по концу импульса считывания. С выхода элемента И-НЕ 33 нулевой уровень поступает на сбросовый вход триггера 14, и триггер 14 устанавливается в нулевое состояние. Таким образом, формирование сигнала заканчивается до прихода следую1цего импульса записи. При цоочередном поступлении импупьгсов записи и считывания происходит постоянное пошаговое продвижение счетчшш 11 адреса записи и счетчика 2О адреса считывания., С выхода счетчика 11 импульсы г i поступают на вход 9 дешифратора 6. С выхода дешифратора сигналы поступают на адресный вход 4 накопителя 2. С выхода счетчика 20 импульсы считывания 5154 поступают Hai вход дешифратора 7, . с выхода которого сигналы дагаьшв поступают на адресный вход 5 накоп теля 2. Таким образом, осуществляется запись и считывание информации в накопитель. Если после первого импульса записи до полного заполнения накопителя 2 не поступает ни одного импульса считывания на вход 23, то после записи последнего бита информации счетчик 11 устанавливается в исходное, одинаковое со счетчиком 2О, состояние. Выход триггера 12 находится при этом в единичном состояНИИ, и на бход 29 элемента И 16 посту пае т разрешающий высЪкий потенциал. После того, как состояния счетчиков 11 и 2О станут одинаковыми, с выхода блока сравнения 18 на вход 31 элемента И 16 поступает единичный сигнал, и следуюший импульс записи, поступающий с входа 1О на вход 15 элемента И 16, проходит через элемент ИЛИ 41 на тактовый вход счетчика 20 и подвигает его на один шаг. Таким образом, в этом случае (от-. сутствия сигналов считывания) осуществляется пошаговое подтягивание счетчика 20 за счетчиком 11 сигналами . Запись вновь поступающей информации происходит на место наиболее старой информации. Если, в общем случае, пооле некоторого импульса записи сигналы считывания перестают поступать, го заполнение накопителя происходит до тех пор, пока состояния счетчиков 11 и 20 не станут одинаковыми. При одинаковом состоянии счетчиков 11 и 20 с выхода блока 18 сравнения вход 31 элемента И 16 поступает высокий потенциал, разрешающий прохож- дение следующего импульса записи на вход счетчика 2О и продвижение его на один шаг. Таким образом, при неравномерном- поступлении сигналов считывания не происходит потерт нювой информации при заполнении накопителя, а возобновление считывания всегда начинается с наиболее старой информации, так как при подтягивании состояния счетчшса 2О вслед за счетчиком 11 потеря адреса записи и считывания не происходит. Отсутствие остановки счетчика зашан си при достижении им максимального значения и введение управления продвиженивм счетчика 20 сигналами записи позволяет записывать любой необход1ь мый объем информации в накопитель.

, при запопйвйии его происходит постёпёккая пошаговая замена ваибопее старой информации новой, ьвовь поступающей без потери адресов записи и считывания.

Указаииая особенность построения БЗУ расширяет область применения уст1 3

ройства, позволяет вести работу с непре рывно поступающим noTOKc vi данаы.х без потери ВОВОЙ, наиболее важной информации. Использование данногч} ЗУ дает возмож- , ность осуществлять прием и ил дач у инфopvfaции от нескольких тнпов AFIJEIi ра6ота1ощих асинхронно. 1Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1982 |

|

SU1019495A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1646001A1 |

| Буферное запоминающее устройство | 1977 |

|

SU733017A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1111202A1 |

| Буферное запоминающее устройство | 1974 |

|

SU493805A1 |

| Буферное запоминающее устройство | 1976 |

|

SU583478A1 |

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

| Буферное запоминающее устройство | 1981 |

|

SU993333A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1444893A1 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

БУФЕРНОЕ- ЗАПОМИНАКЛЦЕЕ УСТРОЙСТВО, содержащее накотггепь, информационные входы и выходы которого являются соответственно информационными входами и выходами устройства, первый и второй адресные входы накопитегш поо кпючены к выходам соответственно первого и второго дешифраторов, первые входы первого и второго дешифраторов являются соответственно первым в вторым управляющими входами устройства, второй вход первого дешифратора пощсюочен к первому выходу . счетчика, второй вход второго дешиф тора подключен к Первому выходу второго счетчика, вторые выходы первого и второго счетчиков подключены к входам блока сравнения, тактовый вход первого счетчика подключен , к первому входу первого дешифратора, триггерь, элементы Н, элементы ИЛИ, элемент И-НЕ и элемент НЕ, о т и в чающееся, тем, что, с хюлыо ij -vj - ,- -,.,.,. / расшнр«1ия областя применения за счет запсмннания информации, поступаюшей после переполненвя накопителя, тактовый вход второго счетчика подключен к выходу первого элемента ИЛИ, первь1й ьход которого подключен к выходу первого апемента И, второй и третий входы 1)ервого элемента ИЛИ подключены к выходам соответственно второго в третьего элементов И, первые входы KOTOI&IX 1годклк чевы к первому входу второго элемента ИЛИ и к первому входу второго дешифратора, второй вход второго элемента И подключен к выходу элемента НЕ, вход которого подключен к выходу блока срав§ нения, к первс лу входу четвертого элемента И и к первому входу первого алегО) мента И, второй вход которого подкюо чен к выходу первого триггера и к втос рому входу третьего элемента И, третий вход первого элемента И подключен к а тактовым входам в третьего триггеров, сбросовому входу вторсач) триггера в к тактовому входу первого счетчика, второй вход второго элемента ОИЛИ является третьим управляющим вхоi дсял устройства в подключен к установоч90 ному эходу второго триггера и к сбросо:;i сл вым входам первого в второго счетчиков, выход второго элемента ИЛИ подключен к сбросоому входу первого триггера, выход третьего триггера является- управляющим входсм устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Буферное запоминающее устройство | 1976 |

|

SU583476A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-10-15—Публикация

1982-04-09—Подача