Изобретение относится к вычислительной технике и может найти.применение в схемах встроенного контроля логических блоков, в частности ПЛМ.

Цель изобретения - расширение функциональных возможностей.

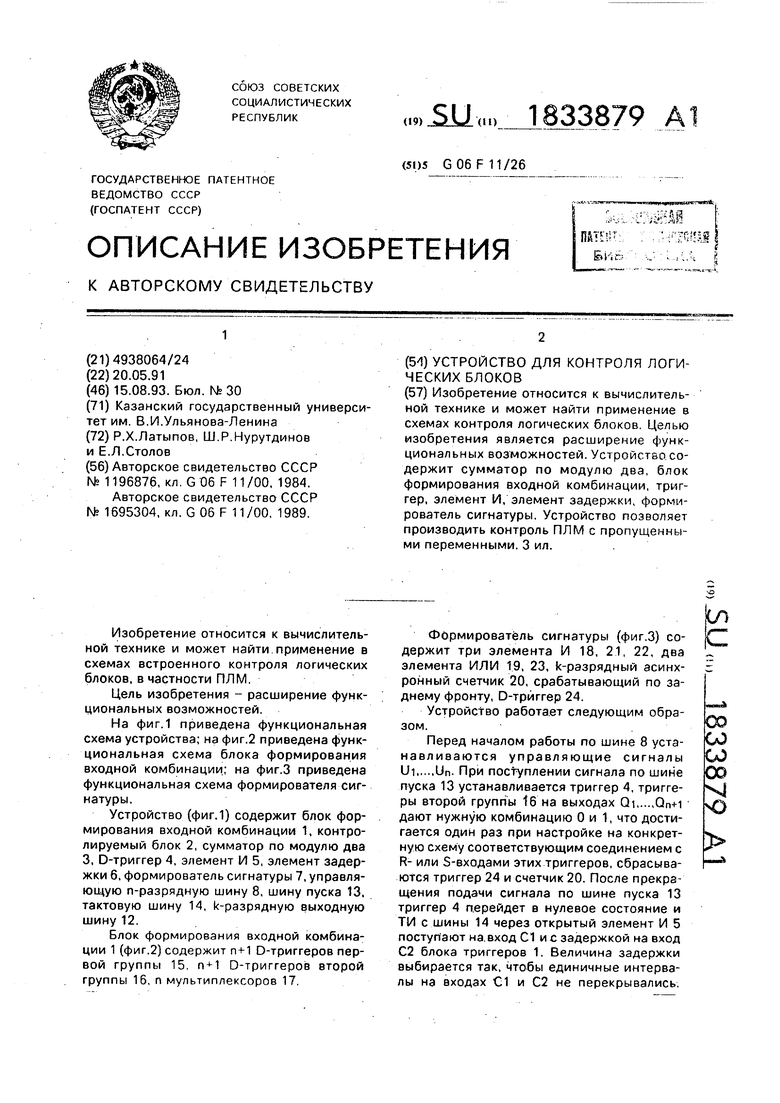

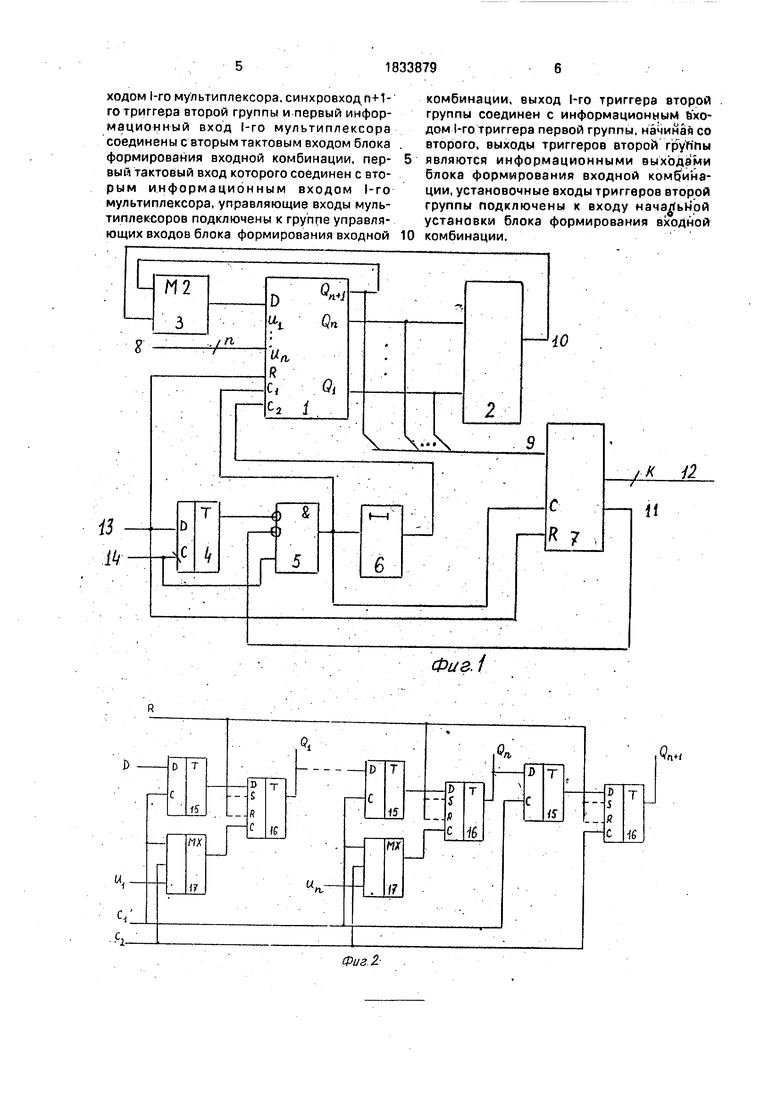

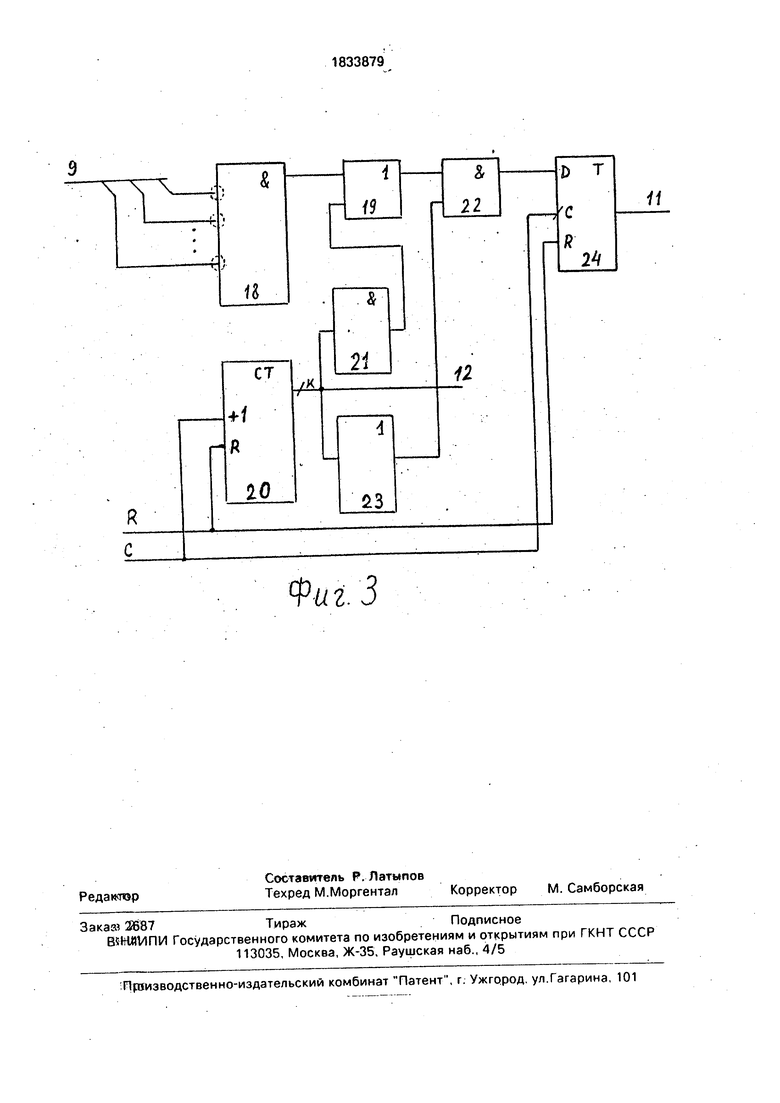

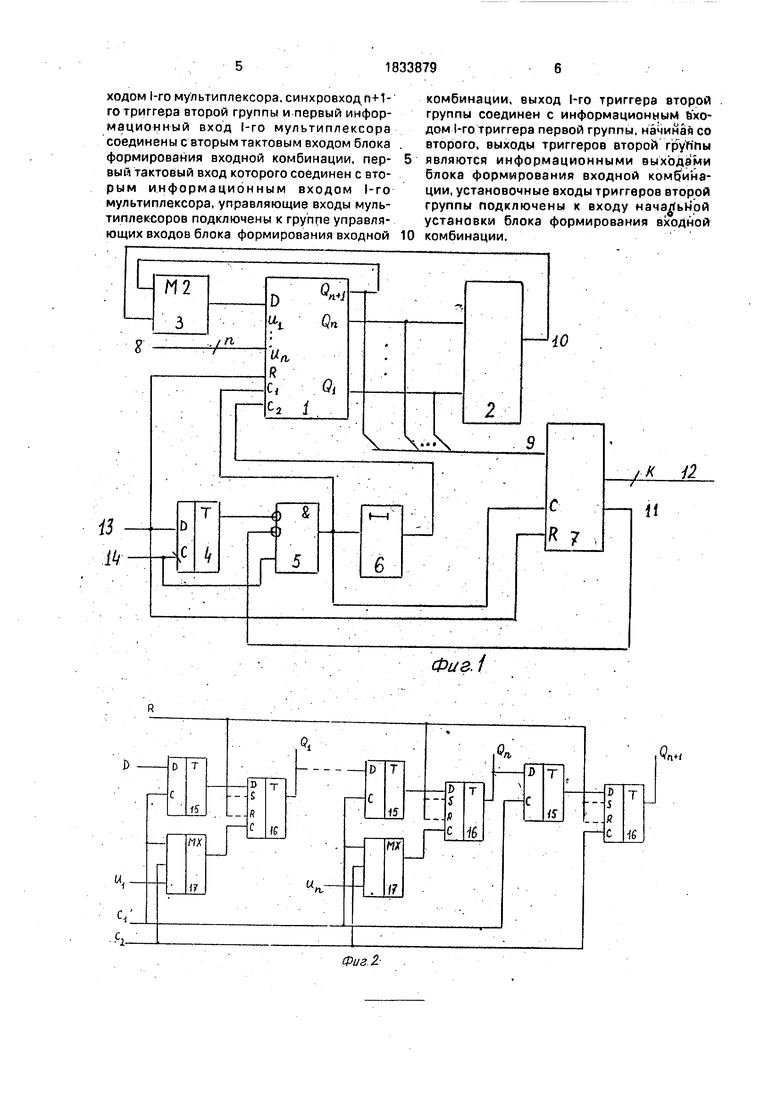

На фиг.1 приведена функциональная схема устройства; на фиг.2 приведена функциональная схема блока формирования входной комбинации; на фиг.З приведена функциональная схема формирователя сигнатуры.

Устройство (фиг.1) содержит блок формирования входной комбинации 1, контролируемый блок 2, сумматор по модулю два 3, D-триггер 4, элемент И 5, элемент задержки 6, формирователь сигнатуры 7, управляющую n-разрядную шину 8, шину пуска 13. тактовую шину 14, k-разрядную выходную шину 12.

Блок формирования входной комбинации 1 (фиг.2) содержит п+1 D-триггеров первой группы 15. п-Ч D-триггеров второй группы 16. п мультиплексоров 17.

Формирователь сигнатуры (фиг.З) содержит три элемента И 18, 2.1, 22, два элемента ИЛИ 19, 23, k-рэзрядный асинхронный счетчик 20, срабатывающий по заднему фронту, D-трйггер 24.

Устройство работает следующим образом.

Перед началом работы по шине 8 устанавливаются управляющие сигналы

UiUn- При поступлении сигнала по шине

пуска 13 устанавливается триггер 4, триггеры второй группы 16 на выходах QiQn+i

дают нужную комбинацию 0 и 1, что достигается один раз при настройке на конкретную схему соответствующим соединением с R- или S-входами этих триггеров, сбрасываются триггер 24 и счетчик 20. После прекращения подачи сигнала по шине пуска 13 триггер 4 перейдет в нулевое состояние и ТИ с шины 14 через открытый элемент И 5 поступают на.вход С1 и с задержкой на вход С2 блока триггеров 1. Величина задержки выбирается так, чтобы единичные интервалы на входах С1 и С2 не перекрывались.

(Л

С

со со со

00 XI

ю

Нулевой сигнал с выхода счетчика 20 через элемент ИЛИ 23 поступает на вход элемента И 22 и блокирует поступление единичного сигнала с выхода элемента И 18, настроенного на начальное состояние устройства в течение первого тактового импульса. ТИ поступают на накапливающий вход счетчика 20, увеличивая его содержимое на единицу,

n-разрядный сигнал с выходов СИQrvH

блока 1 поступает на соответствующие вхо- ды блока 2, а выход блока 2 и выход Оп+1 блока 1 суммируются сумматором по модулю два 3 и поступают на D-вход блока 1. Одновременно сигналы с выходов блока 1 поступают на входы элемента И 9 формиро- вателя 7. При появлении на выходах блока 1 начальной комбинации, а на выходе сумматора 3 нужного сигнала, либо при появлении двоичной комбинации 11...11 на выходе счетчика 20, единичный сигнал с выхода эле- мента И 21 через элемент ИЛИ 19 установит D-триггер 24 в единичное состояние. Одновременно единичный сигнал с выхода 11 триггера 24 запирает элемент И 5, устройство прекращает работу. После этого содер- жимое счетчика 20 по шине 12 поступает на выход устройства и сравнивается с эталоном. Если содержимое счетчика совпадаете эталоном, то блок считается исправным, в противном случае блок 2 неисправен,

Приме р. Рассмотрим проверку стол бцов Й-матрицы ПЛМ, зависящей от переменных. Предполагается, что и имеется доступ к m прямым и m инвертированным входам ПЛМ . Входы ПЛМ подклю- чаются к выходам Qi...Qn блока 1 следующим образом: 1-й прямой вход - к QI, а 1-й инвертированный вход - к Qm+i. Таким образом, способ подключения входов ПЛМ к выходам блока триггеров не зависит от способа .программирования столбцов. Начальное состояние при проверке столбцов ПЛМ равно 11...1. Блок 18 есть элемент И. Пусть проверяемый столбец реализует терм x.n,...xik, xji..,xjk. Тогда на управляющие вхо- ды l iIk, J1jk подаются 1, а на остальные управляющие входы подаются 0. Далее для простоты рассмотрим конкретное значение для m и терма. Пусть m 3, и терм есть хгхз. Тогда переходы состоя- ний 01. 02, 03, 04, 05, 06. 07 для исправного столбца равны 1111111 0011111 1100001 - 1111110 1111111, Таким образом,через 4 такта работы устройство для исправного столбца остановится, эталонное содержимое счетчика равно 4. Допустим, что имеется неисправность -отсутствие переменной Х2 в терме. Тогда переходы состояний имеют вид 1111111 - 0011111 +00.00001 -

1100000 00 П 110 - 1100001 - 1111110 1111111. Устройство остановится через 7 тактов и по содержимому счетчика определяется неисправность устройства.

Формул а изобретения Устройство для контроля логических блоков, содержащее сумматор по модулю два/триггер, элемент И, причем вход пуска устройства подключен к D-входу триггера, прямой выход которого соединен с первым инверсным входом элемента И, о т л и ч а ю- щ е е с я тем, что, с целью расширения области-применения, в устройство введены блок формирования входной комбинации, формирователь сигнатуры, элемент задержки, причем первый вход сумматора по модулю два соединен с (п+1)-м вы ходом блока формирования входной комбинации, .второй вход сумматора по модулю два является входом устройства для подключения к выходу контролируемого блока, выход сумматора по модулю два соединен с информационным входом блок-а формирования входной комбинации, группа входов задания режима которого является группой управляющих входов устройства, пер-- вый и второй тактовые входы и вход начальной установки блока формирования входной комбинации соединены соответ-- ственно с выходом элемента и,, выходом элемента задержки и входом пуска устрой- ства, n-выходов блока формирования входной комбинации соединены с информационными входами формирователя сигнатуры и являются выходами устройства для подключения к входам контролируемого- блока, синхровход и вход начальной.установки формирователя сигнатуры соединены соответственно с выходом элемента И и входом пуска устройства, группа выходов формирователя сигнатуры является группой выходов результата контроля устройства, выход конца работы формирователя сигнатуры соединен с вторым инверсным вхо-- дом элемента И, блок формирования входной комбинации-содержит две группы из п+1 триггеров и группу из п мультиплексоров, причем информационный вход первого триггера первой группы подключен к- информационному входу блока формирования входной комбинации, выход 1-го триггера первой группы (, п+1) соединен с информационным входом i-ro триггера второй группы, синхровходы триггеров пер вой группы соединены с первым такто- вым в-ходом блока формирования входной комбинации, синхровход i-ro триггера второй группы, кроме п+1-го. соединен с выходом 1-го мультиплексора, синхровход п+1- го триггера второй группы и первый информационный вход 1-го мультиплексора соединены с вторым тактовым входом блока формирования входной комбинации, первый тактовый вход которого соединен с вторым информационным входом 1-го мультиплексора, управляющие входы мультиплексоров подключены к группе управляющих входов блока формирования входной

0

комбинации, выход 1-го триггера второй группы соединен с информационным входом 1-го триггера первой группы,начиная со второго, выходы триггеров второй группы являются информационными выходами блока формирования входной комбинации, установочные входы триггеров второй группы подключены к входу нача ьн рй установки блока формирования входной комбинации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1401462A1 |

| Устройство для встроенного тестового контроля | 1986 |

|

SU1324029A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

Изобретение относится к вычислительной технике и может найти применение в схемах контроля логических блоков. Целью изобретения является расширение функциональных возможностей. Устройство, содержит сумматор по модулю два, блок формирования входной комбинации, триггер, элемент И, элемент задержки, формирователь сигнатуры. Устройство позволяет производить контроль ПЛМ с пропущенными переменными. 3 ил.

Фиг. 1

. 3

| Устройство для контроля цифровых блоков | 1984 |

|

SU1196876A1 |

| Устройство для контроля логических блоков | 1989 |

|

SU1695304A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-08-15—Публикация

1991-05-20—Подача