Г

Изобретение относится к автоматике и вычислительной технике и может использоваться в цифровых системах автоматического управления позиционированием перемещающихся объектов.

Цель изобретения - повышение быстродействия системы за счет формирования уплотненной параболической, гистограммы торможения.

Сущность изобретения состоит в новой дисциплине функционирования системы, позволяющей повысить Коэффициент заполнения параболической диаграммы выходных сигналов преобразователя код-напряжение в функции, кода разности заданного и текущего положений объекта, что ведет к со- кпащению времени торможения объекта.

31А6

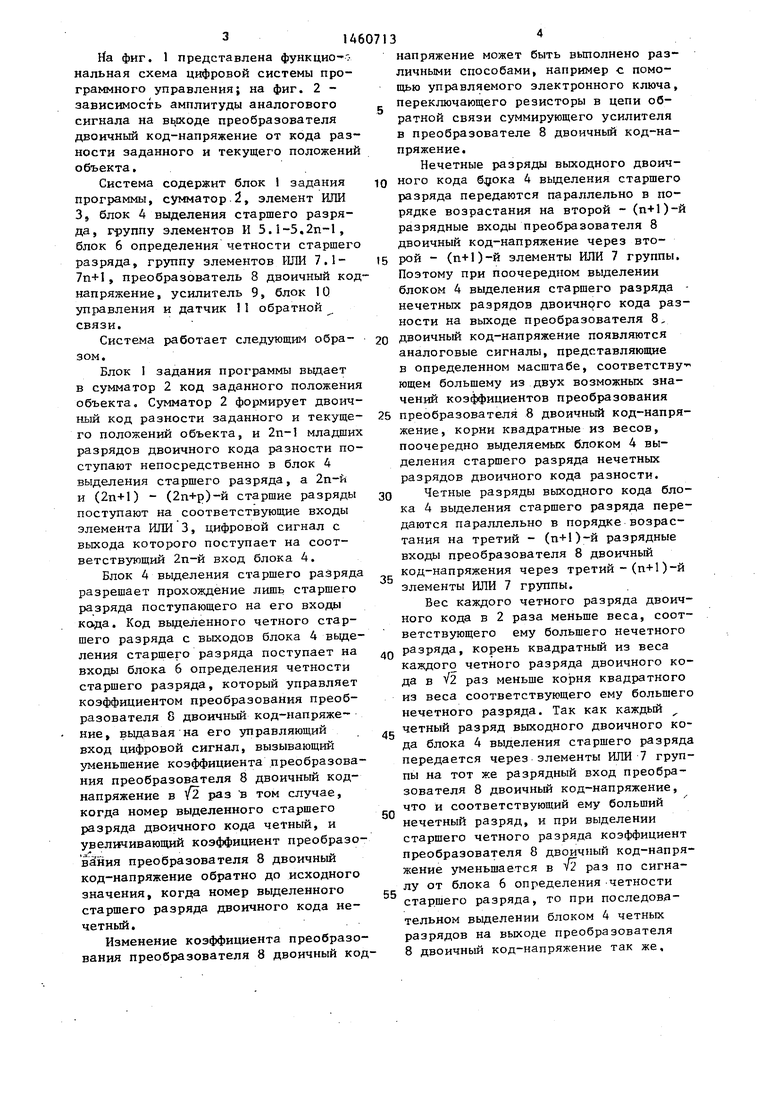

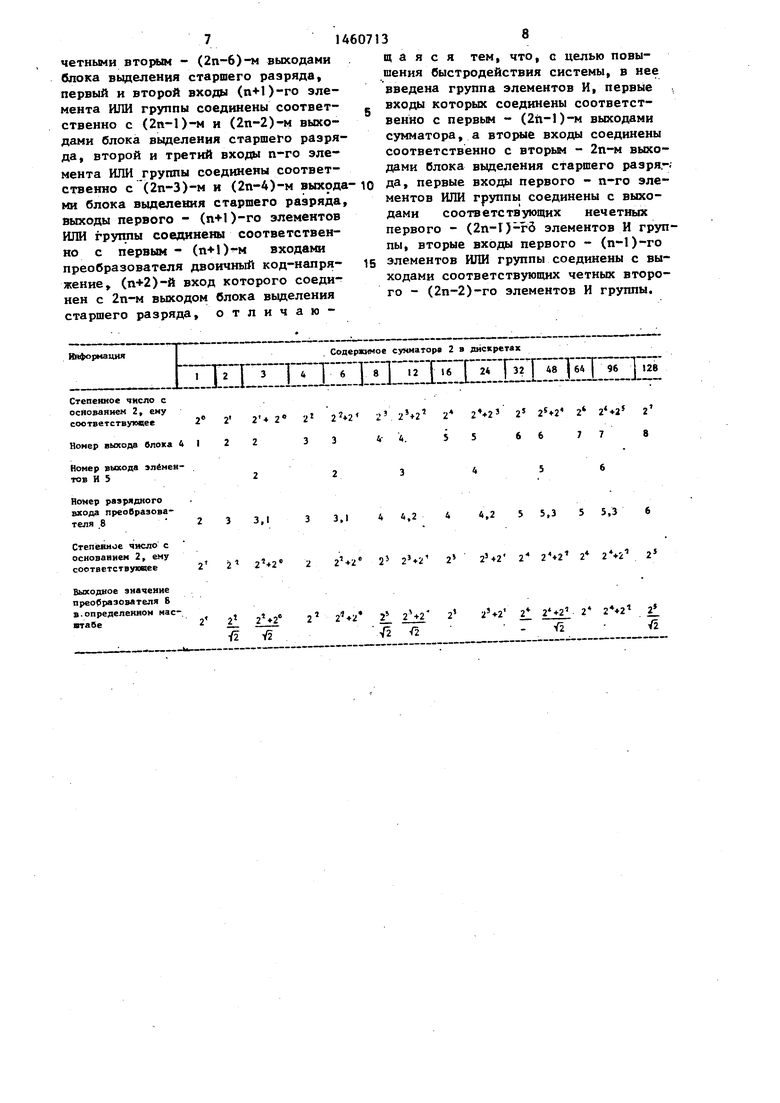

На фиг. 1 представлена функцио-о нальная схема цифровой системы программного управления; на фиг. 2 - зависимость амплитуды аналогового сигнала на вькоде преобразователя двоичный код-напряжение от кода разности заданного и текущего положений объекта.

Система содержит блок 1 задания программы, сумматор.2, элемент ИЛИ 3j блок 4 выделения старшего разряда, группу элементов И 5.1-5,2п-1, блок б определения четности старшего разряда, группу элементов ИЛИ 7.1- , преобразователь 8 двоичный код напряжение, усилитель 9, блок 1Q управления и датчик 11 обратной связи.

Система работает следующим обра- зом.

Блок I задания программы вьщает в сумматор 2 код заданного положения объекта. Сумматор 2 формирует двоичный код разности заданного и текуще- го положений объекта, и 2п-1 младших разрядов двоичного кода разности поступают непосредственно в блок 4 выделения старшего разряда, а 2п-й и (2п+1) - (2п+р)-й старшие разряды поступают на соответствующие входы элемента ИЛИ 3, цифровой сигнал с выхода которого поступает на соответствующий 2п-и вход блока 4.

Блок 4 выделения старшего разряда разрешает прохождение лишь старшего разряда поступающего на его входы кода. Код выделенного четного старшего разряда с выходов блока 4 выделения старшего разряда поступает на входы блока 6 определения четности старшего разряда, который управляет коэффициентом преобразования преобразователя 8 двоичный код-напряжение, вьщавая на его управляющий вход цифровой сигнал, вызывающий уменьшение коэффициента преобразования преобразователя 8 двоичный код- напряжение в /2 раз в том случае, когда номер выделенного старшего разряда двоичного кода четный, и увеличивающий коэффициент преобразо преобразователя 8 двоичный код-напряжение обратно до исходного значения, когда номер выделенного старшего разряда двоичного кода нечетный.

Изменение коэффициента преобразования преобразователя 8 двоичный ко

напряжение может быть вьшолнено различными способами, например с помощью управляемого электронного ключа, переключающего резисторы в цепи обратной связи суммирующего усилителя в преобразователе 8 двоичный код-напряжение.

Нечетные разряды выходного двоичного кода 4 выделения старшего разряда передаются параллельно в порядке возрастания на второй - (п+1)-й разрядные входы преобр)а зова теля 8 двоичный код-напряжение через второй - (п+1)-й элементы ИЛИ 7 группы. Поэтому при поочередном выделении блоком 4 выделения старшего разряда - нечетных разрядов двоичного кода разности на выходе преобразователя 8, двоичный код-напряжение появляются аналоговые сигналы, представляющие в определенном масштабе, соответствую ющем большему из двух возможных значений коэффициентов преобразования преобразователя 8 двоичньй код-напряжение, корни квадратные из весов, поочередно выделяемых блоком 4 выделения старшего разряда нечетных разрядов двоичного кода разности.

Четные разряды выходного кода блока 4 выделения старшего разряда передаются параллельно в порядке возрастания на третий - (п+1)-й разрядные входы преобразователя 8 двоичный код-напряжения через третий -(п+1)-и элементы ИЛИ 7 группы.

Вес каждого четного разряда двоичного кода в 2 раза меньше веса, соответствующего ему большего нечетного разряда, корень квадратный из веса каждого четного разряда двоичного кода в V2 раз меньше корня квадратного из веса соответствующего ему большего нечетного разряда. Так как каждый четный разряд выходного двоичного кода блока 4 выделения старшего разряда передается через элементы ИЛИ 7 группы на тот же разрядный вход преобразователя 8 двоичный код-напряжение, что и соответствующий ему больший нечетный разряд, и при выделении старшего четного разряда коэффициент преобразователя 8 двоичный код-напряжение уменьшается в V2 раз по сигналу от блока 6 определения-четности старшего разряда, то при последовательном выделении блоком 4 четных разрядов на выходе преобразователя 8 двоичный код-напряжение так же.

как и в случае с выделением нечетных разрядов, появляются аналоговые сигналы, представляющие собой корни квадратные из весов выделяемых четных разрядов, причем в том же масштабе , что и для случая выделения всех нечетных разрядов.

Аналогично нечетные разряды сумматора 2, на единицу меньшие старших выявляемые нечетными, т.е. первым и третьим - (2п-1)-м элементами И 5. группы передаются параллельно в порядке возрастания на первый - п-й разрядные входы преобразователя 8 двоичный код-напряжение через первый - п-й злементы ИЛИ 7 группы.

Четные разряды сумматора 2, на единицу меньшие старших, выявляемые четными, т.е. вторым - (2п-2)-м элементами И 5 группы, передаются параллельно в порядке возрастания на первый - (п-1)-й разрядные входы преобразователя 8 двоичный код-напряжение через первый - (п-1)-й элементы ИЛИ 7 группы.

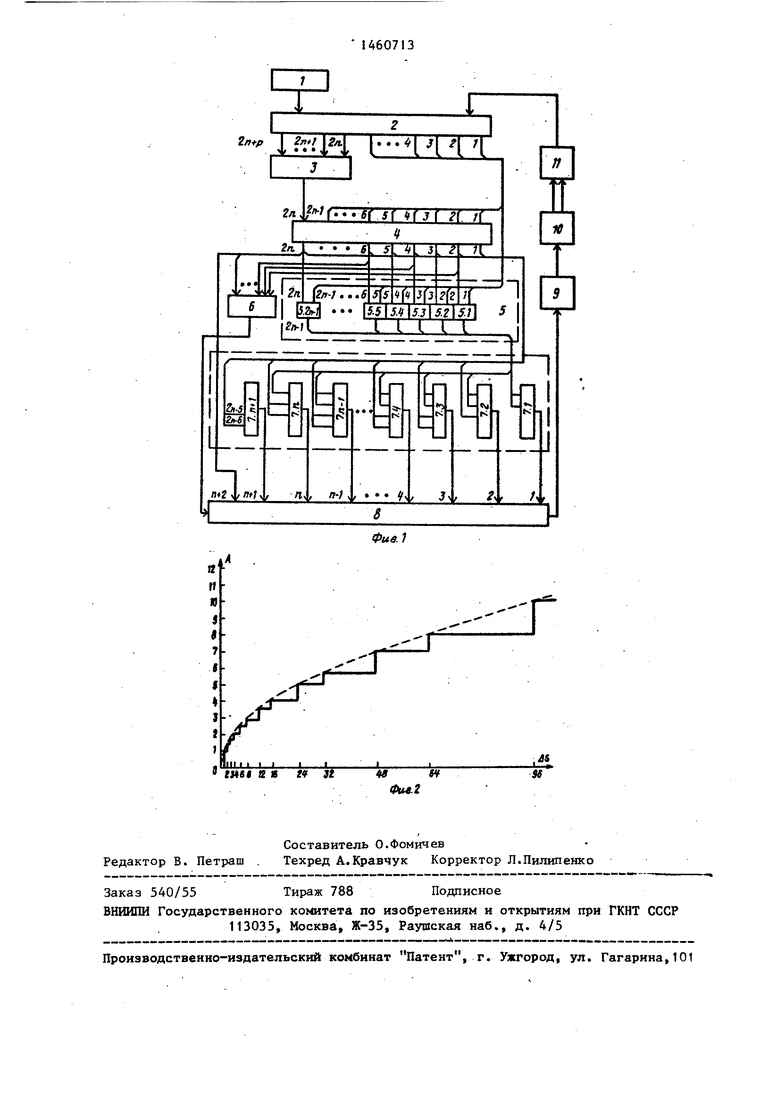

При выделении блоком 4 выделения старшего разряда как нечетных, так и четных разрядов двоичного кода раз «ости и при выявлении элементами И 5 группы разрядов сумматора 2, на единицу меньших старших разрядов, на выходе преобразователя 8 двоичный код- напряжение формируется информация в соответствии с таблицей.

Эта информация соответствует корню квадратному (умноженному на 2) из весов отдельных нечетных и четных разрядов двоичного кода разности |. заданного и текущего положений объекта. Точность соответствия этой информации корню квадратному (умноженному на 2) из суммы весов двух старших разрядов составляет +2%.

Аналоговый сигнал с выхода преобразователя 8 двоичный код-напряжение через усилитель 9 поступает на блок 10 управления, перемещающий объект и датчик 11 обратной связи. Код текущего положения объекта с выхода датчика 11 обратной связи поступает на первый (вычитающий) вход сумматора 1, который формирует новый код разности. Если этот код становится равным нулю, напряжение на вход усилителя 9 не подается и перемещение объекта заканчивается в данной точке.

Для оптимального по быстродействию процесса позиционирования характерно торможение с постоянньм максимально допустимым по. величине ускорением. Связь скорости V и перемещения S при движении с ускорением iai определяется зависимостью V Va2S. Чтобы обеспечить такой закон движения, задание на скорость, т.е. выходное напряжение преобразователя 8 двоичный код-напряжение, должно быть связано с рассогласованием по nepe- i- мещению параболической зависимостью.

В предлагаемой системе обеспечивается формирование параболически (с точностью ± 1%) изменяющейся по амплитуде гистограммы напряжений А (фиг. 2), соответствующих весам последовательно выделяемых двух старших и старших разрядов кода разности AS заданно-го и текущего положений объекта, что приближает быстродействие процесса позиционирования к оптимальному значению.

Формула изобретения

Цифровая система программного управления, содержащая группу элементов ИЛИ, блок вьщеления старшего разряда, блок определения четности старшего разряда и последовательно соединенные преобразователь двоичный

код-напряжение, усилитель, блок управления, датчик обратной связи и сумматор, второй вход которого соединен с выходом блока задания программы, а 2п...(2п+р) выходы старших

разрядов сумматора подключены к входам элемента ИЛИ, выход которого соединен с 2п-входом блока выделения старшего разряда, первый - (2п-1)-й входы которого соединены соответст-. .

венно с первым - (2п-1)-м выходами младших разрядов сумматора, управляющий вход преобразователя двоичный код-напряжение соединен с выходом блока определения четности старшего

разряда, входы которого соединены с соответствующими четными выходами блока выделения старшего разряда, третьи входы второго (n-l)-ro элементов ИЛИ группы соединены с соответствующими нечетными первым - (2п-5)-м выходами блока выделения старшего разряда, четвертые входы третьего - (n-l)-ro элементов ИЛИ группы соединены с соответствующими

7146

четньми вторым - (2п-6)-м выходами блока выделения старшего разряда, первый и второй входы ()-го элемента ИЛИ группы соединены соответ- ственно с (2п-1)-м и (2п-2)-м выходами блока выделения старшего разряда, второй и третий входы п-го элемента ИЛИ группы соединены соответственно с (2п-3)-м и (2п-4)-м выходами блока выделения старшего разряда, выходы первого - (п+1)-го элементов ИЛИ грутты соединены соответственно с п ервым - (п+1)м входами преобразователя двоичный код-напряжение, (п+2)-й вход которого соединен с 2п-м выходом блока выделения старшего разряда, отличаю

38

щ а я с я тем, что, с целью повышения быстродействия системы, в нее введена группа элементов И, первые входы которых соединены соответственно с первым - (2п-1)-м выходами сумматора, а вторые входы соединены соответственно с вторым - 2п-м выходами блока выделения старшего разря,- да, первые входы первого - п-го элементов ИЛИ группы соединены с выходами соответств ующих нечетных первого - (2п-Г)-г5 элементов И группы, вторые входы первого - (n-l)-ro элементов ШШ группы соединены с выходами соответствующих четных второго - (2п-2)-го элементов И группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая система программного управления | 1988 |

|

SU1508192A1 |

| Цифровая система программного управления | 1980 |

|

SU888074A1 |

| Цифровая система для программного управления | 1987 |

|

SU1441352A1 |

| Цифровая система программного управления | 1987 |

|

SU1411710A1 |

| Преобразователь кодов | 1989 |

|

SU1762410A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| Функциональный преобразователь нескольких переменных | 1986 |

|

SU1387022A1 |

| УСТРОЙСТВО КАСКАДНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ, ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА И МАКСИМАЛЬНЫХ ГРУПП | 2019 |

|

RU2701709C1 |

| Устройство для контроля Р-кодов Фибоначчи | 1988 |

|

SU1533007A1 |

Изобретение относится к области автоматики и вычислительной техники и может использоваться в цифровых системах автоматического управления позиционированием перемещающихся объектов .Цель изобретения - повышение быстродействия системы за счет формироваНИН уплотненной параболической гистограммы торможения.Поставленная цель достигается тем, что в известную систему, содержащую блок .задания программы, сумматор, элемент ИЛИ, блок выделения старшего разряда, блок определения четности старшего разряда, группу элементов ИЛИ, преобра-. зователь двоичный код-напряжение, усилитель, блок управления и датчик обратной связи, введена группа элементов И. Введение новых элементов и соответствующих связей позволяет формировать нелинейно изменяющуюся (по зависимости, близкой к параболической) по амплитуде гистограмму выходных сигналов преобразователя двоичный код-напряжение, соответствующих весам последовательно выделяемых двух старших и старших разрядов кода разности &S заданного и текущего по-.- ложений объекта, т.е. остатка пути обработки, что увеличивает скорость процесса позиционирования, так как торможение производится с ускорением, среднее значение которого приближается к максимальному. 2 ил., 1 табл. € сл фь ф о 0

Ипфорнация

Содержимое суяматора 2 в дискретах

Содержимое суяматора 2 в дискретах

ТТТ Т Т 1 П Т Т Т Т «Т Ч

J. „.J,J -«I-J..-l.-.

Степенное число с.

основанием 2, ему..3 z +z 2 2 2 2

соответствующеегг.

«с&ь778

Номер выхода блока 41 2 2

Номер выхода элймен- тов И S

3 3 2

3456

Помер разрядного

входа преобразова- , , , ,ч 3 144244,2 5 5,3 5 5,36

теля .8 2 3 J, 1л J, .

Степ1евмое число с

основаиием 2, ему, . jj э., 2 +2 2 2 2

соответствуювее2 2 i J.

+2 2

Выходное значение

преобразователя В«15

в.определенной мае- , ,, 1 l.,. 2 +2 2 2 f2V 2 2 +2 2 штабе

V2 /2

V2

«с&ь77

3456

+2 2

2 +2 2 2 f2V 2 2 +2 2

V2 /2

V2

г

I /I X

L

i

X ГгЦЧ l L

i

n

J f

Sf

| УСТРОЙСТВО для ПРОГРАММНОГО РЕГУЛИРОВАНИЯ СКОРОСТИ подвижных ОБЪЕКТОВ | 0 |

|

SU351200A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Цифровая система автоматического регулирования | 1973 |

|

SU447684A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Цифровая система программного управления | 1976 |

|

SU624210A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Цифровая система программного управления | 1980 |

|

SU888074A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1989-02-23—Публикация

1987-05-14—Подача