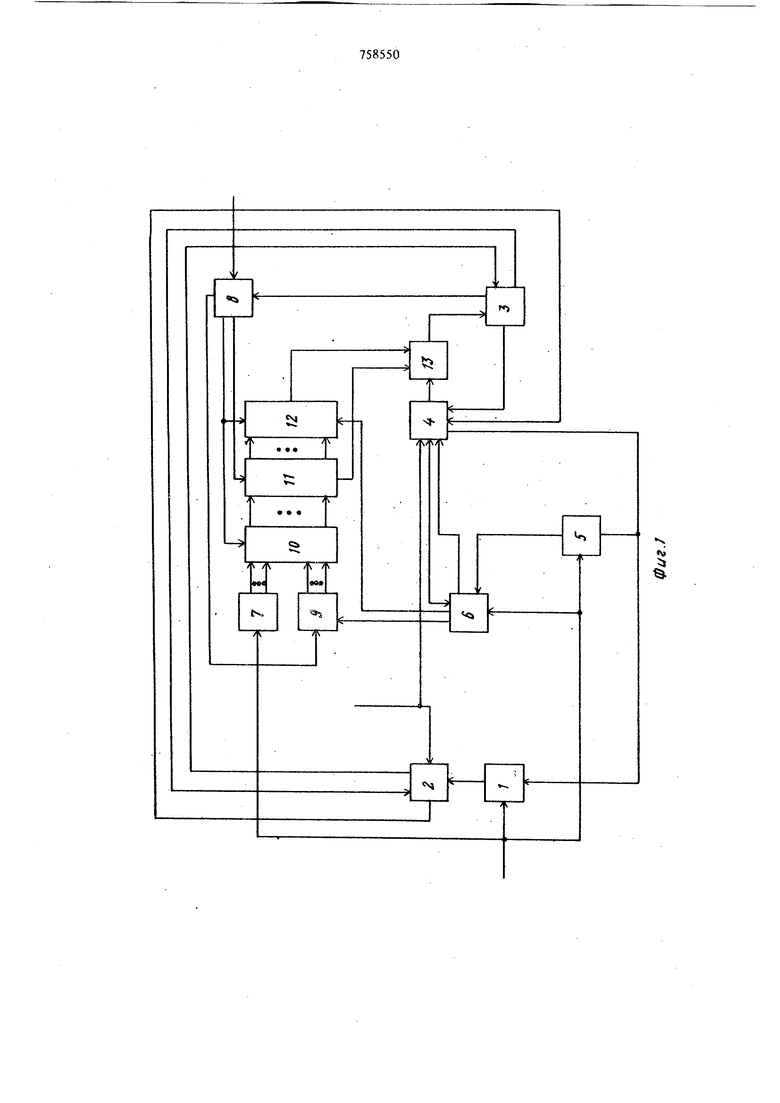

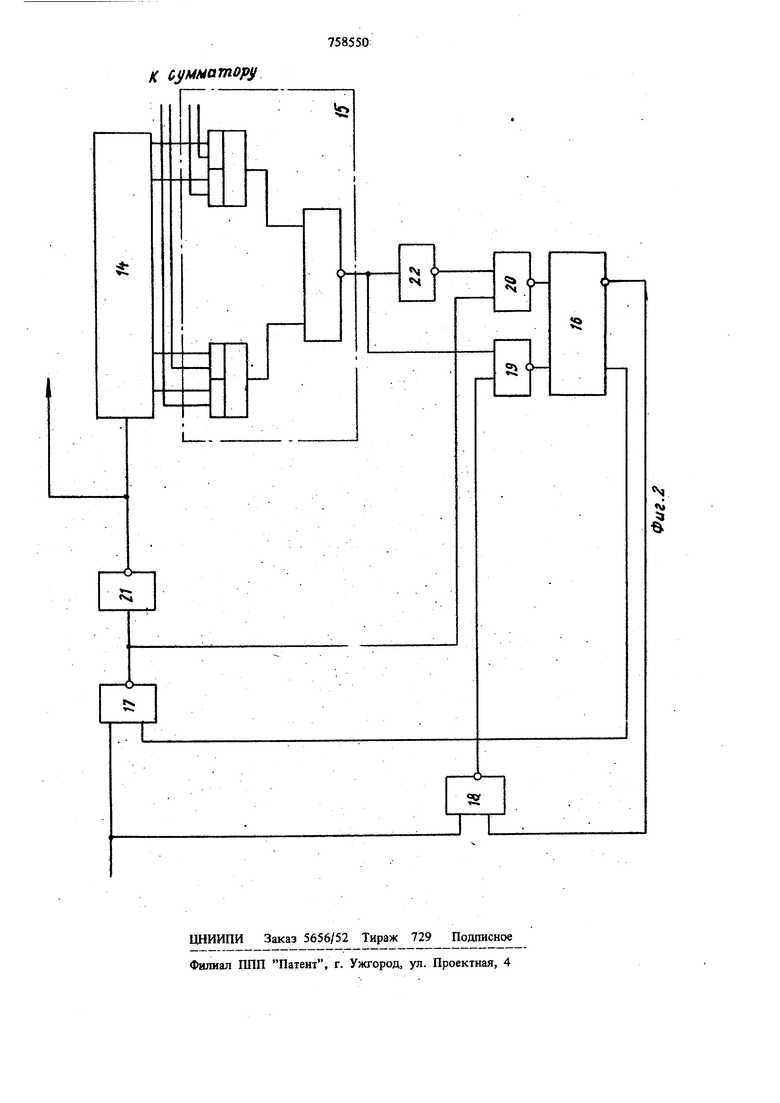

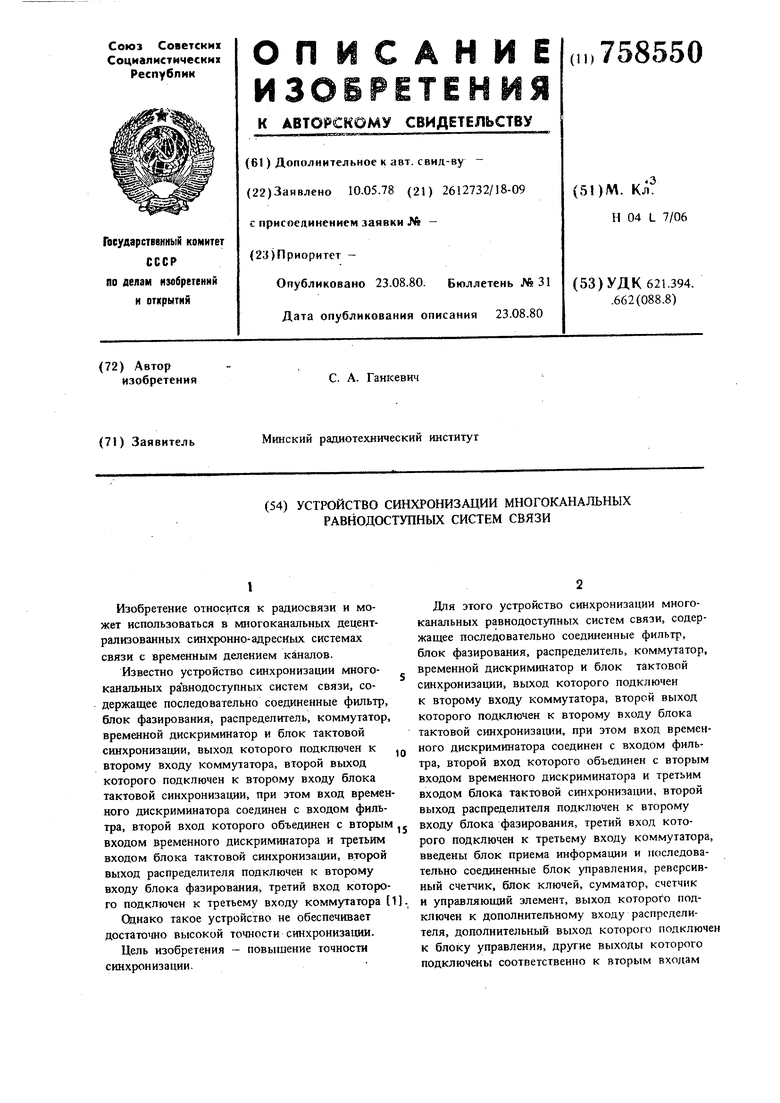

Изобретение относится к радиосвязи и может использоваться в многоканальных децентрализованных синх:ронно-адресных системах связи с временным делением каналов. Известно устройство синхронизации многоканальных равнодоступных систем связи, содержащее последовательно соединенные фильтр блок фазирования, распределитель, коммутатор временной дискриминатор и блок тактовой синхронизации, выход которого подключен к второму входу коммутатора, второй выход которого подключен к второму входу блока тактовой синхронизации, при зтом вход време ного дискриминатора соединен с входом фильтра, второй вход которого объединен с вторым входом временного дискриминатора и третьим входом блока тактовой синхронизации, второй выход распределителя подключен к второму входу блока фазирования, третий вход которо го подключен к третьему входу коммутатора Однако такое устройство не обеспечивает достаточно высокой точности синхронизации. Цель изобретения - повьпиение точности синхронизации. Для этого устройство синхронизации многоканальных равнодоступных систем связи, содержащее последовательно соединенные фильтр, блок фазирования, распределитель, коммутатор, временной дискриминатор и блок тактовой синхронизации, выход которого подключен к второму входу коммутатора, второй выход которого подключен к второму входу блока тактовой синхронизаьщи, при этом вход временного дискриминатора соединен с входом фильтра, второй вход которого объединен с вторым входом временного дискриминатора и третьим входом блока тактовой синхронизации, второй выход распределителя подключен к второму входу блока фазирования, третий вход которого подключен к третьему входу коммутатора, введены блок приема информации и последовательно соединенные блок управления, реверсивный счетчик, блок ключей, сумматор, счетчик и управляющий злемент, выход которого подключен к дополнительному входу распределителя, дополнительный выход которого подключен к блоку управлении, другие выходы которого подключены соответственно к вторым входам . 3 блока ключей:- счетчика и сумматора, второй выход которого подключен к второму входу управляющего элемента, третий вход которого соединен с третьим выходом коммутатора, при чем дополнительные выходы блока тактовой синхронизации подключены соответственно к второму входу реверсивного счетчика, и к третьему входу счетчика, а второй вход фильтра через блок приема информации соединен с третьим входом блока ключей. На фиг. дана структурная электрическая схема предложенного устройства; на фиг. 2 - схема счетчика. Устройство содержит фильтр 1, блок 2 фази рования, распределитель 3, коммутатор 4, временной дискрим шатор 5, блок 6 тактовой син хронизации, блок 7 приема информации, блок управления, реверсивный счетчик 9, блок 10 к чей, сумматор 11, счетчик 12 и управляющий элемент 13. Счетчик 12 содержит счетчик 14, деишфратор 15, RS-триггер 16, элементы И/Н 17-22. Устройство работает следующим образом. Фильтр 1 предназначен для выделения синхр сигнала, принимаемого в начале каждого занятого временного канала. С помощью блока 2 фазирования осуществляется поиск временных каналов и начальное фазирование. Распределитель 3 обеспечивает разметку временных каналов и формирование временных стробов, необходимых для функционирования устройства. Блок 6 тактовой синхронизации обеспечивае сщгхронизапию по информационным посылкам с 1,елью их регистрации и синхронизацию распределителя 3. Коммутатор 4 обеспечивает компенсацию фа зовых сдвигов, возникающих вследствие различ Kbix времен задержки канальных сигналов, к формирование импульсов канальной частоты для определения начала временных каналов через цикл.. . Временной дискриминатор 5 обеспечивает формирование дискриминационной характеристики при приеме синхросигнала. Управляющий элемент 13 обеспечивает коррекцию фазы распределителя 3 при изменении расстояния между станциями. Блок 7 предназначен для выделения из принятых канальных сигналов от дрзтих станций информации о состоянии реверсивных счетчиков 9. Блок 10 обеспечивает запись в сумматор 11 кода реверсивного счетчика 9 и информации о состояниях реверсивных счетчиков 9 других станций. С помощью сумматора 11 осуществляется опера 1ДТЯ суммирования фазового рассогласования всех станций, работающих в сети, накопленного в течение цикла. Счетч1пс 12 обеспечивает подачу на вход управляющего элемента 13 импульсов в соответствии с кодом сумматора 11. Реверсивный счетчшс 9 предназначен для усреднения и накопления информации о разности фаз между принимаемыми канальными сигналами и опорным сигналом в течение длительности цикла. Влияние задержки на частоту следования временных каналЬв приводит к погрещности в восстановлении начала временных каналов через цикл, определяемой величиной прирашения задержки, и срыву синхронизма при превыщении величины 1j,/2 , где т, - длительность элементарной посьижи. Каждая из станции сети использует информацию о разности фаз между. опорным и канальным сигналами за время цикла на всех станциях, работающих в сети.I Информацией о величине приращения задержки в сети является .( свободная частота, i где О) станции;число станций в сети; N % длительность цикла. При нулевой либо скомпенсированной задержке. При наличии приращения задержки эта величина определяется выражением Nk N N. ..,, где„ .Г -iflTUP-l i.W,N+.. ,Z Z: f:; i-л где К - коэффициент усиления; Tjj - величина задержки радиосигнала между i и j станциями. Последнее вьфажение и позволяет составить алгоритм двухсторонней синхронизаШи. Каждая из станций сети в занятом временном канале передает информацию о величине Д j (со i - со) Тц, накопленной в течение предыдущего цикла. Принятая от всех станций информация суммируется на каждой из станций о собственном значении величины A(j, накопленным за цикл, и фаза распределителя временных каналов, а следовательно, и канального сигнала при передаче сдвигается в соответствии с величиной Z Aipj в противоположную по знаку сторону, что позволяет компенсировать влияние задержки на частоту.

На этапе вхождения в связь с помощью блока 2 фазирования производится фаз1грование распределителя 3 по синхросигаалу, принимаемому (С минимальной задержкой относительно тактовых точек временных каналов и фазирование делителей по синхросигналам, принимаемым в соответствующих временных каналах. По отклику фильтра 1 делитель тактовой частоты коммутатора 4 устанавливается в нулевое состояние, а делитель канальной частоты коммутатора 4 - в код, соответствующий базе синхросигнала. Одновременно производится коррекция фазы опорного сигнала тактовой частоты. Для этого в начале временного канала вход делителя коммутатора подключается к управляющему элементу блока 6, а выход - к временному дискриминатору 5.

В момент фазирования распределитель 3 не подстраивается, а по окончании процесса фазирования подключается к выходу ;д1равляющего элемента блока 6 через коммутатор 4 и управляющий элемент 13.

Коммутация делителей осуществляется сигналами с блока 8.

С помощью реверсивного счетчика 9 измеряется фазовое рассогласование между опррны ми и канальными сигналами за время цикла. IВ занятом для передачи временном канале каждая из станций информирует другие станции о состоянии реверсивного счетчика 9. В результате суммирования значений кода, полученных от всех других станций, и кода собственного реверсивного счетчика 9 на выходе сумматора 11 формируется код, пропорциональный величине приращения задержки радиосигнала. В соответствии со значением кода с помощью счетчика 12 и управляющего элемента 13 производитсясдвиг фазы распределителя 3, компенсирующий приращение задержки.

Установка счетчика 12 в нулевое состояние производится сигналом с блока 8 управления. Единичным сигналом с дещифратора 15 открывается элемент И 19, и вне зависимости от предьщущего состояния RS-триггера 16 последний переходит в единичное состояние. При этом на элемент И 17 подается разрешение, а вход элемента И 18 закрывается нулевым сигналом с противоположного плеча RS-триггера 16. При записи в счетчик 14 числа импульсов, соответствующего коду сумматора 11, на элемент И 20 подается разрещение с дешифратора 15,

и по окончании счетного импульса на входе триттер 16 опрокидывается, закрывая посредством подачи на элемент И 17 нулевого сигнала на вход счетчика 14, который открывается вновь только по приходу сигнала начальной установки.

Предложенное устройство позволяет за счет устранения влияния задержки на среднюю частоту в сети обеспечить более высокую точность

синхронизации по временным каналам.

Формула изобретения

Устройство синхронизащ1И многоканальных равнодоступных систем связи, содержащее последовательно соединенные фильтр, блок фазирования, распределитель, коммутатор, временной дискриминатор и блок тактовой синхронизащ И, выход которого подключен к второму входу коммутатора, второй выход которого подключен к второму входу блока тактовой синхронизации, при этом вход временного дискриминатора соединен с входом фильтра, второй

вход которого объединен с вторым входом временного дискриминатора и третьим входом блока тактовой синхронизации, второй выход распределителя подключен к второму входу блока фазирования, третий вход которого подключен к третьему входу, коммутатора, отличающееся тем, что, с целью повыщения точности синхронизации, введены блок приема информации и последовательно соединенные блок зшравления, реверсивнътй счетчик, блок

ключей, сумматор, счетчик и управляющий элемент, выход которого подключен к дополнительному входу распределителя, дополнительный выход которого подключен к блоку зшравления, выходы которого подключены соответственно к вторым входам блока ключей, счекчика и сумматора, второй которого подключен к второму входу управляющего элемента, третий вход которого соединен с третьим выходом коммутатора, причем дополнительные выходы блока тактовой синхронизации подключены соответственно к второму входу реверсивного счетчика и третьему входу счетчика, авторой вход фильтра через блок приема информации соед1шен с третьим входом блока

ключей.

Исто1шики ияформапии, принятые во внимание при экспе 1тизе 1. Заявка № 2372221/18-09, кл. П (И L 7/02, 1976 (прототип).

«м

f( cyMMomOfy

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство для синхронизации многоканальных равнодоступных систем связи | 1978 |

|

SU681569A2 |

| Устройство для синхронизации многоканальных равнодоступных систем связи | 1977 |

|

SU681566A2 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1469562A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для синхронизации равнодоступных многоканальных систем связи | 1975 |

|

SU563736A1 |

| Устройство для синхронизации многоканальных равнодоступных систем связи | 1976 |

|

SU650245A1 |

| Устройство синхронизации многоканальных равнодоступных систем связи | 1978 |

|

SU745012A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1982 |

|

SU1030986A1 |

| Устройство синхронизации многоканальной системы радиосвязи | 1990 |

|

SU1739502A1 |

N «i

Авторы

Даты

1980-08-23—Публикация

1978-05-10—Подача