1

Изобретение относится к радиосвязи и быть использовано в многоканальгных децейтрализованных синхронно-адресных системах связи в временным делением каналов.

Известное устройство синзфонизадии многоканальных равнодоступных систем связи содержит последовательно соеди- ненные блок фазирования, распределитель временных каналов, управляемый коммутатор и блок тактовой синхронизации, выход которого подключен к второму входу управляемого коммутатора, причем другой выход распределителя временнь1х каналов подключен к второму входу блока фазирования, другой выход которого подключен к другому входу управляемого коммутатора, при этом на третий вход блока фазирования подан входной сигнал ClJОднако известное устройство имеет недостаточйую точность синхронизации.

Цель изобретения - повышение точности синхронизации.

Для этого в устройство синхронизации многоканальных равнодоступных систем связи введены последовательно соединенные ключ, блок корреляционной обработки, коммутатор и управляющий элемент, а также блок усреднения, входы которого объединены с входами коммутатора и соединены с дополнительными выходами блока тактовой синхронизации, а выход блока усреднения подключен к

10 второму входу блока, корреляционной обработки, третий вход которого соединен с вторым дополнительным выходом блока тактовой синхронизации и дополнительным входом блока фазирования, причем выход

15 управляющего элемента подключен к допсшнительному входу распределителя ременных каналов, а другой вход управляющего элемента соединен с третьим дополнительным выходом блока тактовой

20 синхронизации, а дополнительный выход управляемого коммутатора подключен к четвертому входу блока корреляционной обработки и входу ключа, другой вход

которого объединен с третьим входом блока фазирования и вторым дополнительным входом блока тактовой син онизации.

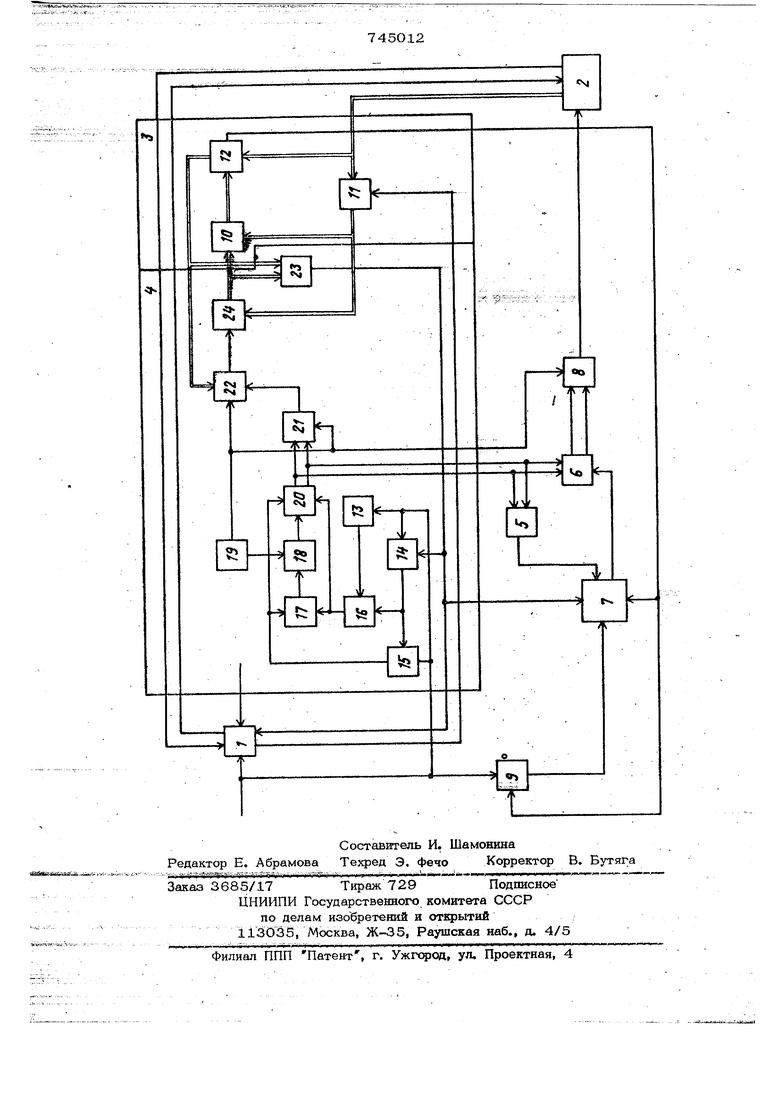

На чертеже изображена структурная

схема устройства синхронизации многоканальных равнодоступных систем свяаи.

Предложенное устройство содержит последовательно соединенные блок 1

фазирования, распределитель 2 временных каналов, управляемый коммутатор 3 и блок 4 тактовой синхроинзании, выход которого подключен к второму входу управляемого коммутатора 3. Другой

выход распределителя 2 временных каналов подключен к второму входу блока 1 другой выход которого подключен к другому входу управляемого коммутатора 3. lia третий вход блока 1 подан входной сигнал. Входы блока 5 усреднения объединены с входами коммутатора 6 и соединены с дополнительными выходами блока 4. Выход блока 5 подключен к второму входу блока 7 корреляционной обработки, третий вход которого соединен с вторым дополнительным выходом блока 4 и дополнительным входом блока 1.

Выход управляющего элемента 8 подключен к дополшггельному входу распределителя 2, а другой вход управляющего элемента 8 соединен с третьим дополнительным выходом блока 4г Дополнительный выход управл:яемого коммутатора 3 подключен к четвертому входу блока 7 и входу ключа 9, другой вход которого объединен с третьим входом блока 1 и вторым дополнительЕсым входом блока 4.

.Управляемый коммутатор 3 состоит вз делителя 10 канальной частоты, коммутатора 11 с элементом 12 управления коммутацией.

Блок 4 тает-овой синхронизации сое-, тоит из элемента 13 задержки, регенератора 14, перемножителей 15, 16, сумматора по модулю 2 17, элемента И 18, генератора 19, реверсивного счет чика 20, утфавляющего элемента 21, ко мутаторов 22, 23, делителя 24 тактовой частоты.

Предложенное устройство работает следующим образом.

На этапе вхождения в связь производится фазирование распределителя 2 по синхросягналу, принимаемому с минимальной задержкой относительно тактовых точек Е менных каналов, полученных в резулмате фазирования распределителя 2 по первому принятому синхросигналу, а также фазирование делителей 24 и 10 по синхросигналам, принятым в соответствующих времегшых каналах с помощью блока 1, Одновременно производится коррекция фазы опорного сигнала тактовой частоты, получаемого на выходе делителя 24. По окончании времен.ного канала делитель 24 подключается к вы- . ходу генератора 19, а для следующего временного канала - к управляющему элементу 21. Через время цикла последовательности импульсов тактовой частоты на выходе делителя 24 будут синфазны с значащими моментами соответствующих канальных сигналов. При последующей коммутации делителей 10, 24 к регенератору фазовое рассогласование между входным и оперным сигналами бедет определяться лишь нестабильностью генерируе- мыхчастот и длительностью цикла. Коммутация выходов делителей 10 и 24 к регенератору гфоизводится в момент смен временных каналов посредством коммутатора 23, а входа к управляющему элементу 21 - посредством коммутатора 22 Коммутаторы 22 и 23 управляются сигналами с элемента 12, который, в свою очередь, управляется сигналами с выходов распределителя 2.

Устранение влияния задержки на частоту осуществляется следующим/образом.

Если приращение расстояний между станциями не равно О, знак усредненной величины фазового рассогласования между опорным и канальным сигналами тактовой частоты, определяемь1й с помощью блока 5, одинаков на всех станциях и соответствует знаку приращения задержки. В занятом для передачи временном канале каждая станция информирует другие станции о знаке фазового рассогласования посредством передачи в начале ременного канала одного из двух щэотивопйложных синхросигналов. Последа ВИЙ используется также при корреляционном приеме в качестве опорного сигнала. В этом случае максимальное значение корреляции йа выходе блока 7 положительна.

Коммутатор 6 подключает перекрестно шшй добавления и бычитания к упрабляЕоmeNsy элементу 8. При этом знак коррекции фазы распределителя 2 противоположен знаку приращения задержки. При этом влияйие задержки на частоту компенсируется, поскольку передача информации осуществляется с фазой распределителя 2

Если прираШенйе расстояний равно или близко к О, знак усредненной величины фазового рассогласования на различных станциях различен и определяется разностью между средней частотой цикла в сети и частотой цикла собственного генератсфа .Цри различии в знаках фазового рассогласования на передающей и приемной станциях максимальное значение ксфреляцйонной функции отрицательно. В результате этого с помощью коммутатора ь осуществляется прямое соединение шин добавления и вычитания управляющих элементов 21 и 8, и коррекция фазы распределителя 2 совпадает по величине и знаку с коррекцией фазы делитедя 24,

Изобретение позволяет обеспечить высокую точность синхронизации по временным каналам, а также снизить погрешность синхронизации, при этом максимальная продолжительность сеанса связи не ограничивается.

.

. Формула, изобретения

Устройство синхронизации многоканальных равнодоступных систем связи, содержащее последовательно соединеншде блок фазирования, распределитель Щ)еменных каналов, управляемый KOMMyraTqp и блок тактовой синхронизации, выход которого подключен к второму входу управляемого коммутатора, причем другой выход распределителя временных каналов подключен к Второму входу блока фазироЬания, другой выход которого подключен к другому входу управляемого коммутатора при этом йа третий вход блока фаа1фования подан входной сигнал, о т л и ч а ю щ е е с я тем, что, с целью : повышения точности синхронизации, введены последовательно соединенные ключ, блок, корреляционной обработки, коммутат ф и управляющий элемент, а тже блок усреднения, входы которого объдинены с вхбдами коммутатора и соединены с дополНЕРгельными выходами блока тактовой синзфонизации, а выход блока усреднения подключен к второму входу блока корреляционной обработки, третий вход KOTqporo соединен с вторым дополнительным выходом блока тактовой синзфонизации и дополнительным входом блока фазирования, причем выход управляющего элемеяга подключен к дополнительному входу распределителя временных каналов, а другой вход управляющег элемента соединен с третьим дополнительным выходом блока тактовой синхронизации, а дополнительный выход управляемого коммутатора подключен к четвертому входу блока корреляционной обработки и входу ключа, другой вход которого объединен с третьим входом блока фазирования и вторым дополнительным входом блока тактовой синхронизации.

Источники информации, принятые Во внимание при экспертизе

1. Авторское свидетельство СССР по заявке № 2372221/18-09, кл. Н 04 t 7/02, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1469562A1 |

| Устройство синхронизации многоканальных равнодоступных систем связи | 1978 |

|

SU758550A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1982 |

|

SU1030986A1 |

| Устройство для синхронизации многоканальных равнодоступных систем связи | 1978 |

|

SU681569A2 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для синхронизации многоканальных равнодоступных систем связи | 1976 |

|

SU650245A1 |

| Устройство для синхронизации многоканальных равнодоступных систем связи | 1977 |

|

SU681566A2 |

| Устройство для синхронизации равнодоступных многоканальных систем связи | 1975 |

|

SU563736A1 |

| Устройство синхронизации многоканальной системы радиосвязи | 1990 |

|

SU1739502A1 |

Авторы

Даты

1980-06-30—Публикация

1978-03-16—Подача