te

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ ОШИБОК И КОРРЕКЦИЕЙ ОДИНОЧНОЙ ОШИБКИ | 1993 |

|

RU2062512C1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| УПРАВЛЯЮЩАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2520350C2 |

| Резервированное оперативное запоминающее устройство | 1987 |

|

SU1471225A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

Изобретение относится к вычислительной технике, в частности к полупроводниковым запоминающим устройствам. Цель изобретения - повышение надежности запоминающего устройства. Резервированное запоминающее устройство с коррекцией информации содержит три основных накопителя, накопитель корректирующих кодов, три схемы управления коррекцией, три блока сравнения, три блока эл.ементов И, два блока мажоритарных элементов, пять элементов ИЛИ, два элемента И, два формирователя временного интервала, элемент НЕ и соответствующие связи между ними. Новым является введение в устройство элементов ИЛИ, формирователей временного интервала, схем управления коррекцией, элемента НЕ, блоков элементов И и соответствующих связей. 2 ил.

Изобретение относится к вычислительной технике, в частности к полупроводниковым запоминающим устройствам (ЗУ).

Известно трехканальное мажоритарное резервированное запоминающее устройство, содержащее три блока памяти с контрольными разрядами, блоки свертки, элементы сравнения, блоки сравнения, мажоритарный блок, коммутатор, информационные выходы, выход коммутатора, управляющие входы и информационные входы коммутатора.

К недостаткам данного устройства относят принципиальную возможность выдачи на выход устройства недостоверной информации в случае одновременного и идентичного искажения информации в двух любых накопителях. Кроме того, в устройстве не парируются совпадающие по адресу одновременные отказы трех накопителей. А общая адресная часть для информационных

и контрольных разрядов каждого из накопителей приводит к тому, что отказы в адресных трактах устройства с помощью схем свертки и элементов сравнения не выявляются, что снижает надежность устройства. Наиболее близким по технической сущности к предлагаемому является резервированное оперативное запоминающее устройство, содержащее первый регистр, адресные входы устройства, блок управления режимом, вторые входы первого регистра, второй регистр, информационные входы устройства, элемент ИЛИ-НЕ, выход элемента ИЛИ-НЕ, блок кодирования, накопители данных, накопители корректирующих кодов, выходы выбора накопителя блока управления режимом, пятый и четвертый регистры, третьи входы четвертого регистра, мажоритарные элементы, третий регистр, блок сравнения, дешифратор, блок коррекции, выходы устройства, первые и вторые

S

i

v|

ел

СО

ho о

элементы и инверторы, элементы задержки, вход выборки устройства.

Недостаток известного устройства - наличие отдельного накопителя контрольных разрядов для каждого из основных накопителей, что приводит к значительной аппаратной избыточности, особенно при использовании мощных корректирующих кодов. Кроме того, метоД коррекции основанный на сравнении считанных из контрольных накопителей и вновь получаемых корректирующих кодов, может привести к несанкционированному искажению достоверной информации с выходов основных накопителей, например в случае одновременного совпадающего по адресу отказа в двух любых накопителях корректирующих кодов.

Общим недостатком, снижающим надежность устройства - прототипа и устройства - аналога является также невозможность восстановления правильной информации в рабочих накопителях в случае мягких (некатастрофических) отказов ячеек памяти, что приводит в условиях длительной непрерывной работы к накоплению отказов и повышает ёероятность появления непарируемого отказа.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в резервированное запоминающее устройство с коррекцией информации, содержащее первый, второй, третий накопители, накопитель корректирующих кодов, первый и второй блоки мажоритарных элементов, первый и второй элементы И, три блока сравнения, причем входы первой группы третьего блока сравнения и входы первой группы второго блока сравнения объединены и являются третьим информационным входом-выходом устройства, входы вто рой группы второго блока сравнения и входы первой группы первого блока сравнения объединены и являются вторым информационным входом-выходом устройства, входы второй группы первого блока сравнения и входы второй группы третьего блока сравнения объединены и являются первым информационным входом-выходом устройства, а адресные входы первого, второго и третьего накопителя являются соответственно первым, вторым и третьим адресным входами устройства, введены первые, второй, третий, четвертый и пятый элементы ИЛИ, первый и второй формирователи временного интервала, первый, второй и третий блоки управления коррекцией, элемент НЕ, первый, второй и третий блоки элементов И, выходы которых соединены соответственно с первыми входами первого, второго, третьего блоков управления коррекцией, первые входы первого, второго и третьего блоков элементов И объединены и подключены к выходу первого блока сравнения, вторые входы первого,

второго и третьего блоков элементов И объединены и подключены к выходу второго блока сравнения, третьи входы первого, второго и третьего блоков элементов И объединены и подключены к выходу третьего блока

0 сравнения, четвертые входы первого, второго и третьего блоков элементов И обьедине- ны и подключены к выходу второго формирователя временного интервала, вход которого, вход первого формирователя

5 временного интервала, вторые входы первого, второго и третьего блоков управления коррекцией объединены и являются входом синхронизации устройства, третьи входы первого, второго и третьего блоков управле0 ния коррекцией объединены и соединены с выходом накопителя корректирующих кодов, информационный вход которого соединен с выходом первого блока мажоритарных элементов, первый, второй и третий входы

5 которого подключены соответственно к первым выходам первого, второго и третьего блоков управления коррекцией, вторые входы которых соединены соответственно с первыми входами третьего, четвертого и пя0 того элементов ИЛИ и с первым, вторым, третьим входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом элемента НЕ, вход ко5 торого, вторые входы третьего, четвертого, пятого элементов ИЛИ и первый вход первого элемента И объединены и являются входом управления записью устройства, выход первого формирователя временного ин0 тервала соединен с объединенными вторым входом первого элемента И и третьим входом второго элемента И, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого и вход управ5 ления накопителя корректирующих кодов объединены и подключены к выходу первого элемента И, выход второго элемента ИЛИ соединен с объединенными входами записи первого, второго и третьего накопителей,

0 входы управления которых подключены соответственно к выходам третьего, четвертого и пятого элементов ИЛИ, адресные входы первого, второго и третьего накопителей соединены соответственно с первым, ворым,

5 третьим входами второго блока мажоритарных элементов, выход которого подключен к адресному входу накопителя корректирующих кодов, причем информационные входы-выходы группы первого, второго и третьего накопителей соединены соответствен но с входами-выходами первой группы первого, второго и третьего блоков управления коррекцией, входы-выходы второй группы которых являются соответственно информационными входами-выходами первой, второй и третьей групп устройства.

Положительный эффект при осуществлении изобретения достигается за счет: парирования совпадающих по адресу идентичных отказов в двух накопителях и совпадающих по адресу отказов в трех накопителях; исключения накопления мягких (некатастрофических) отказов ячеек памяти в накопителях; исключения возможности несанкционированной коррекции правильной информации накопителей при отказах в накопителе корректирующих кодов.

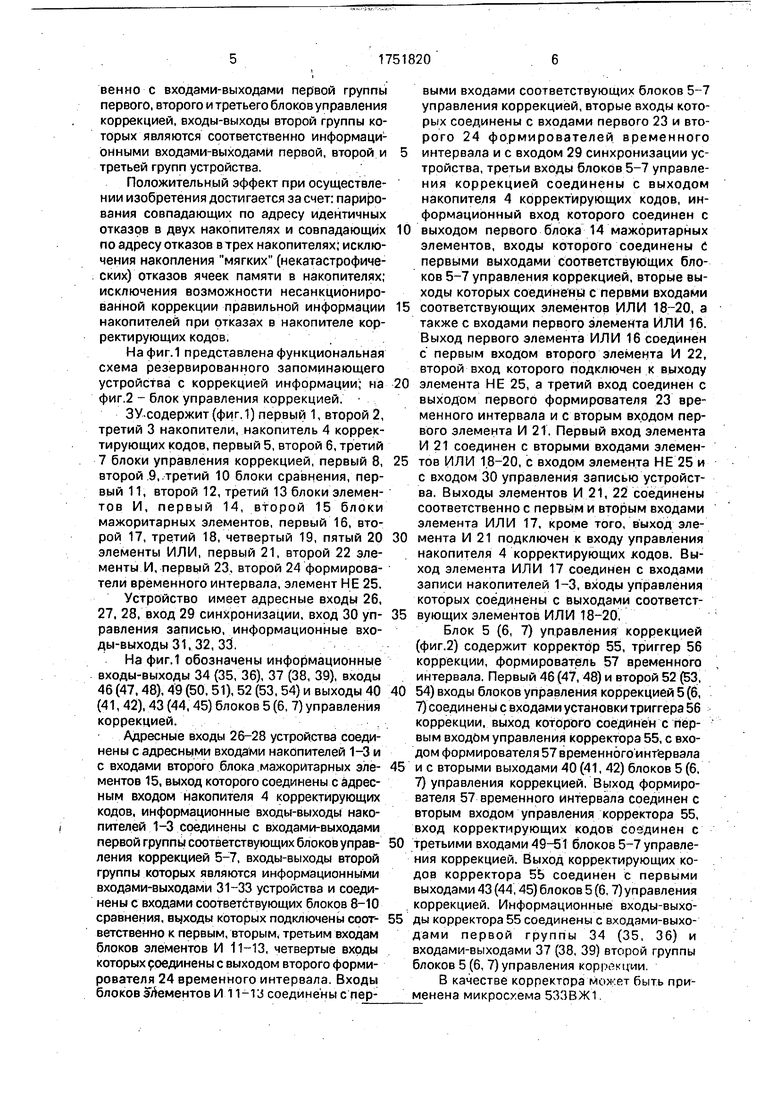

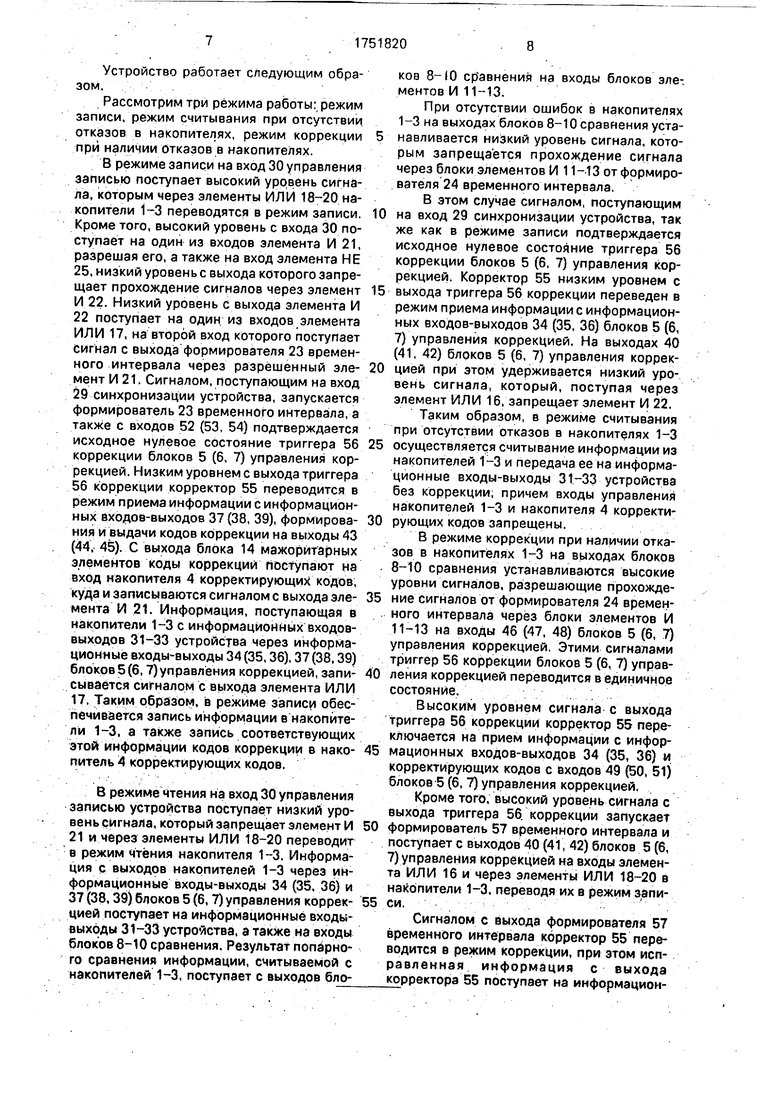

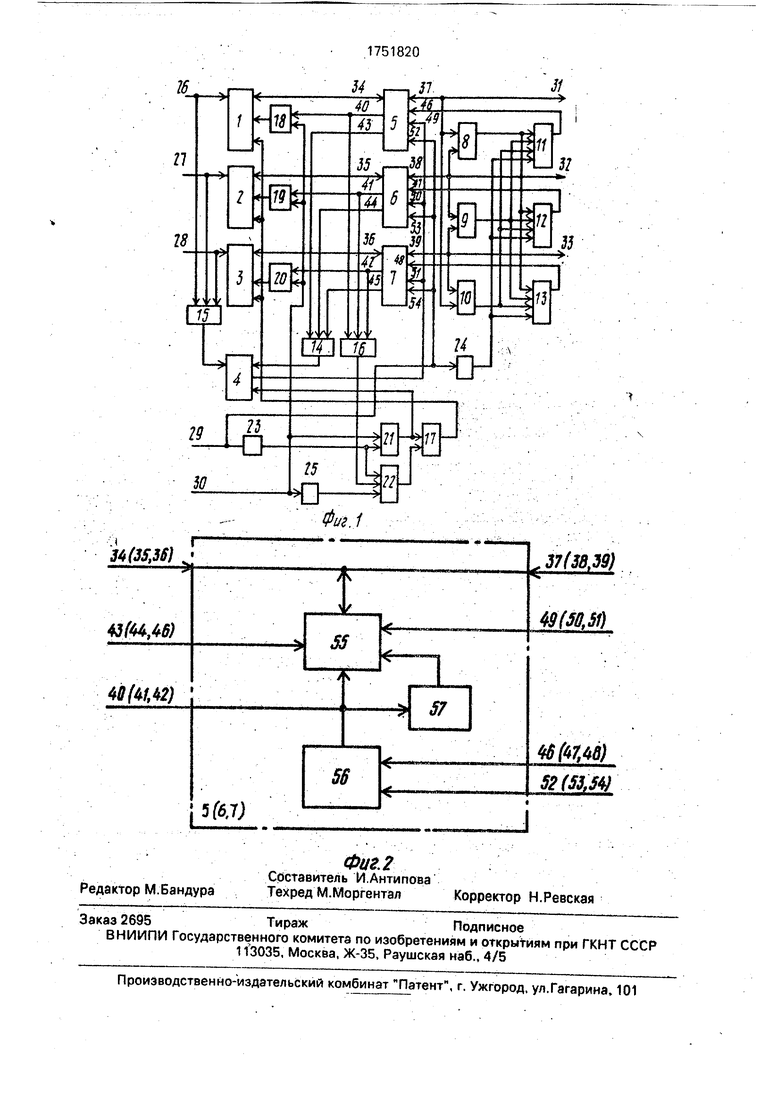

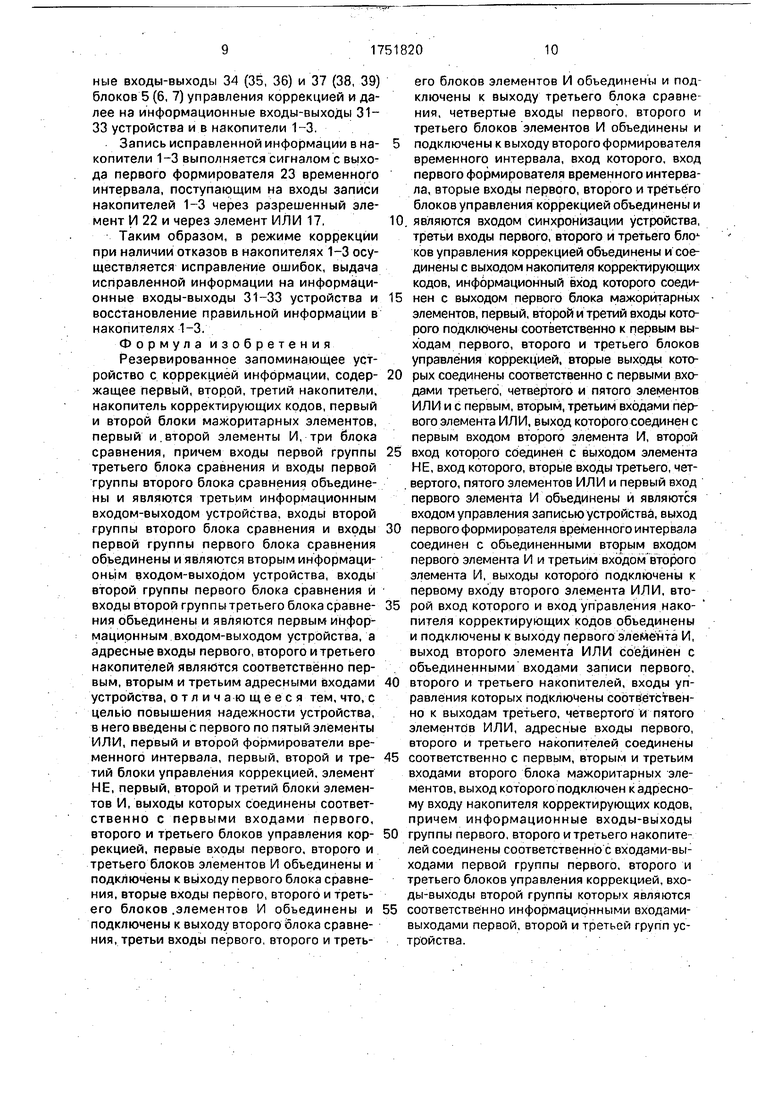

На фиг.1 представлена функциональная схема резервированного запоминающего устройства с коррекцией информации; на фиг.2 - блок управления коррекцией.

ЗУ-содержит (фиг.1) первый 1, второй 2, третий 3 накопители, накопитель 4 корректирующих кодов, первый 5, второй 6, третий 7 блоки управления коррекцией, первый 8, второй 9, третий 10 блоки сравнения, первый 11, второй 12, третий 13 блоки элементов И, первый 14, второй 15 блоки мажоритарных элементов, первый 16, второй 17, третий 18, четвертый 19, пятый 20 элементы ИЛИ, первый 21, второй 22 элементы И, первый 23, второй 24 формирователи временного интервала, элемент НЕ 25.

Устройство имеет адресные входы 26, 27, 28, вход 29 синхронизации, вход 30 уп- равления записью, информационные входы-выходы 31, 32, 33.

На фиг.1 обозначены информационные входы-выходы 34 (35, 36), 37 (38, 39), входы 46 (47,48), 49 (50, 51), 52 (53, 54) и выходы 40 (41, 42), 43 (44, 45) блоков 5 (6, 7) управления коррекцией.

Адресные входы 26-28 устройства соединены с адресными входами накопителей 1-3 и с входами второго блока мажоритарных эле- ментов 15, выход которого соединены с адресным входом накопителя 4 корректирующих кодов, информационные входы-выходы накопителей 1-3 соединены с входами-выходами первой группы соответствующих блоков управ- ления коррекцией 5-7, входы-выходы второй группы которых являются информационными входами-выходами 31-33 устройства и соединены с входами соответствующих блоков 8-10 сравнения, выходы которых подключены соот- ветственно к первым, вторым, третьим входам блоков элементов И 11-13, четвертые входы которых соединены с выходом второго формирователя 24 временного интервала. Входы блоков элементов И 11-и соединены с первыми входами соответствующих блоков 5-7 управления коррекцией, вторые входы которых соединены с входами первого 23 и второго 24 формирователей временного интервала и с входом 29 синхронизации устройства, третьи входы блоков 5-7 управления коррекцией соединены с выходом накопителя 4 корректирующих кодов, информационный вход которого соединен с выходом первого блока 14 мажоритарных элементов, входы которого соединены С первыми выходами соответствующих блоков 5-7 управления коррекцией, вторые выходы которых соединены с первми входами соответствующих элементов ИЛИ 18-20, а также с входами первого элемента ИЛИ 16. Выход первого элемента ИЛИ 16 соединен с первым входом второго элемента И 22, второй вход которого подключен к выходу элемента НЕ 25, а третий вход соединен с выходом первого формирователя 23 временного интервала и с вторым входом первого элемента И 21. Первый вход элемента И 21 соединен с вторыми входами элементов ИЛИ 18-20, с входом элемента НЕ 25 и с входом 30 управления записью устройства. Выходы элементов И 21, 22 соединены соответственно с первым и вторым входами элемента ИЛИ 17, кроме того, выход элемента И 21 подключен к входу управления накопителя 4 корректирующих кодов. Выход элемента ИЛИ 17 соединен с входами записи накопителей 1-3, входы управления которых соединены с выходами соответствующих элементов ИЛИ 18-20.

Блок 5 (6, 7) управления коррекцией (фиг.2) содержит корректор 55, триггер 56 коррекции, формирователь 57 временного интервала. Первый 46 (47, 48) и второй 52 (53, 54) входы блоков управления коррекцией 5 (6, 7) соединены с входами установки триггера 56 коррекции, выход которого соединен с первым входом управления корректора 55, с входом формирователя 57 временногоинтервала и с вторыми выходами 40 (41, 42) блоков 5 (6, 7) управления коррекцией, Выход формирователя 57 временного интервала соединен с вторым входом управления корректора 55, вход корректирующих кодов соединен с третьими входами 49-51 блоков 5-7 управления коррекцией. Выход корректирующих кодов корректора 5Ь соединен с первыми выходами 43 (44,45) блоков 5 (6, 7) управления коррекцией. Информационные входы-выходы корректора 55 соединены с входами-выходами первой группы 34 (35, 36) и входами-выходами 37 (38, 39) второй группы блоков 5 (6, 7) управления коррекции

В качестве корректора может быть применена микросхема 533ВЖ1

Устройство работает следующим образом.

Рассмотрим три режима работы: режим записи, режим считывания при отсутствии отказов в накопителях, режим коррекции при наличии отказов в накопителях.

В режиме записи на вход 30 управления записью поступает высокий уровень сигнала, которым через элементы ИЛИ 18-20 накопители 1-3 переводятся в режим записи. Кроме того, высокий уровень с входа 30 поступает на один из входов элемента И 21, разрешая его, а также на вход элемента НЕ 25, низкий уровень с выхода которого запрещает прохождение сигналов через элемент И 22. Низкий уровень с выхода элемента И 22 поступает на один из входов элемента ИЛИ 17, на второй вход которого поступает сигнал с выхода формирователя 23 временного интервала через разрешенный эле- мент И 21. Сигналом, поступающим на вход 29 синхронизации устройства, запускается формирователь 23 временного интервала, а также с входов 52 (53, 54) подтверждается исходное нулевое состояние триггера 56 коррекции блоков 5 (6, 7) управления коррекцией. Низким уровнем с выхода триггера 56 коррекции корректор 55 переводится в режим приема информации с информационных входов-выходов 37 (38, 39), формирова- ния и выдачи кодов коррекции на выходы 43 (44, 45). С выхода блока 14 мажоритарных элементов коды коррекции поступают на вход накопителя 4 корректирующих кодов, куда и записываются сигналом с выхода эле- мента И 21. Информация, поступающая в накопители 1-3 с информационных входов- выходов 31-33 устройства через информационные входы-выходы 34 (35,36), 37 (38,39) блоков5(6,7)управления коррекцией, запи сывается сигналом с выхода элемента ИЛИ 17. Таким образом, в режиме записи обеспечивается запись информации в накопители 1-3, а также запись соответствующих этой информации кодов коррекции в нако- питель 4 корректирующих кодов.

В режиме чтения на вход 30 управления записью устройства поступает низкий уровень сигнала, который запрещает элемент И 21 и через элементы ИЛИ 18-20 переводит в режим чтения накопителя 1-3. Информация с выходов накопителей 1-3 через информационные входы-выходы 34 (35, 36) и 37 (38,39) блоков 5 (6, 7) управления коррек- цией поступает на информационные входы- выходы 31-33 устройства, а также на входы блоков 8-10 сравнения. Результат попарного сравнения информации, считываемой с накопителей 1-3, поступает с выходов 6локов 8-Ю сравнения на входы блоков элементов И 11-13.

При отсутствии ошибок в накопителях 1-3 на выходах блоков 8-10 сравнения устанавливается низкий уровень сигнала, которым запрещается прохождение сигнала через блоки элементов И 11-13 от формирователя 24 временного интервала.

В этом случае сигналом, поступающим на вход 29 синхронизации устройства, так же как в режиме записи подтверждается исходное нулевое состояние триггера 56 коррекции блоков 5 (6, 7) управления коррекцией. Корректор 55 низким уровнем с выхода триггера 56 коррекции переведен в режим приема информации с информационных входов-выходов 34 (35, 36) блоков 5 (6, 7) управления коррекцией. На выходах 40 (41, 42) блоков 5 (6, 7) управления коррекцией при этом удерживается низкий уровень сигнала, который, поступая через элемент ИЛИ 16, запрещает элемент И 22.

Таким образом, в режиме считывания при отсутствии отказов в накопителях 1-3 осуществляется считывание информации из накопителей 1-3 и передача ее на информационные входы-выходы 31-33 устройства без коррекции, причем входы управления накопителей 1-3 и накопителя 4 корректирующих кодов запрещены.

В режиме коррекции при наличии отказов в накопителях 1-3 на выходах блоков 8-10 сравнения устанавливаются высокие уровни сигналов, разрешающие прохождение сигналов от формирователя 24 временного интервала через блоки элементов И 11-13 на входы 46 (47, 48) блоков 5 (6, 7) управления коррекцией. Этими сигналами триггер 56 коррекции блоков 5 (6, 7) управления коррекцией переводится в единичное состояние.

Высоким уровнем сигнала с выхода триггера 56 коррекции корректор 55 переключается на прием информации с информационных входов-выходов 34 (35, 36) и корректирующих кодов с входов 49 (50, 51) блоков 5 (6, 7) управления коррекцией,

Кроме того, высокий уровень сигнала с выхода триггера 56 коррекции запускает формирователь 57 временного интервала и поступает с выходов 40 (41, 42) блоков 5 (6, 7) управления коррекцией на входы элемента ИЛИ 16 и через элементы ИЛИ 18-20 в накопители 1-3, переводя их в режим записи.

Сигналом с выхода формирователя 57 временного интервала корректор 55 переводится в режим коррекции, при этом исправленная информация с выхода корректора 55 поступает на информациейные входы-выходы 34 (35, 36) и 37 (38, 39) блоков 5 (6, 7) управления коррекцией и далее на информационные входы-выходы 31- 33 устройства и в накопители 1-3

Запись исправленной информации в накопители 1-3 выполняется сигналом с выхода первого формирователя 23 временного интервала, поступающим на входы записи накопителей 1-3 через разрешенный элемент И 22 и через элемент ИЛИ 17,

Таким образом, в режиме коррекции при наличии отказов в накопителях 1-3 осуществляется исправление ошибок, выдача исправленной информации на информационные входы-выходы 31-33 устройства и восстановление правильной информации в накопителях 1-3.

Формула изобретения

Резервированное запоминающее устройство с коррекцией информации, содержащее первый, второй, третий накопители, накопитель корректирующих кодов, первый и второй блоки мажоритарных элементов, первый и второй элементы И, три блока сравнения, причем входы первой группы третьего блока сравнения и входы первой группы второго блока сравнения объединены и являются третьим информационным входом-выходом устройства, входы второй группы второго блока сравнения и входы первой группы первого блока сравнения объединены и являются вторым информаци- оным входом-выходом устройства, входы второй группы первого блока сравнения и входы второй группы третьего блока сравнения объединены и являются первым информационным входом-выходом устройства, а адресные входы первого, второго и третьего накопителей являются соответственно первым, вторым и третьим адресными входами устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены с первого по пятый элементы ИЛИ, первый и второй формирователи временного интервала, первый, второй и третий блоки управления коррекцией, элемент НЕ, первый, второй и третий блоки элементов И, выходы которых соединены соответственно с первыми входами первого, второго и третьего блоков управления коррекцией, первые входы первого, второго и третьего блоков элементов И объединены и подключены к выходу первого блока сравнения, вторые входы первого, второго и третьего блоков .элементов И объединены и подключены к выходу второго блока сравнения, третьи входы первого второго и третьего блоков элементов И объединены и под ключены к выходу третьего блока сравне ния, четвертые входы первого, второго и третьего блоков элементов И объединены и 5 подключены к выходу второго формирователя временного интервала, вход которого, вход первого формирователя временного интервала, вторые входы первого, второго и третьего блоков управления коррекцией объединены и 10 являются входом синхронизации устройства, третьи входы первого, второго и третьего бло1 ков управления коррекцией объединены и соединены с выходом накопителя корректирующих кодов, информационный вход которого соеди- 5 нен с выходом первого блока мажоритарных элементов, первый, второй и третий входы которого подключены соответственно к первым выходам первого, второго и третьего блоков управления коррекцией, вторые выходы кото0 рых соединены соответственно с первыми входами третьего, четвертого и пятого элементов ИЛИ и с первым, вторым, третьим входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй

5 вход которого соединен с выходом элемента НЕ, вход которого, вторые входы третьего, четвертого, пятого элементов ИЛИ и первый вход первого элемента И объединены и являются входом управления записью устройства, выход

0 первого формирователя временного интервала соединен с объединенными вторым входом первого элемента И и третьим входом второго элемента И, выходы которого подключены к первому входу второго элемента ИЛИ, вто5 рой вход которого и вход управления накопителя корректирующих кодов объединены и подключены к выходу первого элемента И, выход второго элемента ИЛИ соединен с объединенными входами записи первого,

0 второго и третьего накопителей, входы управления которых подключены соответственно к выходам третьего, четвертого и пятого элементов ИЛИ, адресные входы первого, второго и третьего накопителей соединены

5 соответственно с первым, вторым и третьим входами второго блока мажоритарных элементов, выход которого подключен к адресному входу накопителя корректирующих кодов, причем информационные входы-выходы

0 группы первого, второго и третье го накопителей соединены соответственно с входами-выходами первой группы первого, второго и третьего блоков управления коррекцией, входы-выходы второй группы которых являются

5 соответственно информационными входами- выходами первой, второй и третьей групп устройства.

| Трехканальное мажоритарное резервированное запоминающее устройство | 1986 |

|

SU1451780A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Резервированное оперативное запоминающее устройство | 1987 |

|

SU1471225A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-07-30—Публикация

1990-07-10—Подача