функции допустимости, запирающее эле- 45 ЧТ и ЗП, что приводит к потере информации и отказу в целом МПС. При такой некорректной ситуации на выходе бломент И 14. Оценка состояния временного распределения управляющих сигналов производится в момент действия етробирующих сигналов Прием или Выка 10 устанавливается код 1000. Так. как всегда Fg 0, то в следующем машинном цикле нулевой сигнал на выбранном входе мультиплексора 12 - (табл. 4) приводит к установке в активное состояние триггера 5 и формированию сигнала на выходе 6 устройства. Выход 6 ошибки устройства может соединяться с входом запроса прерывания МПС или использоваться каким-либо другим образом по усмотрению разработчика. В первом случае при возникноведача микропроцессора. При нормальной

работе МПС в момент появления этих сигналов на выходе элемента ИЛИ 15 элемент И 14 закрыт, что предотвращает появление сигнала ошибки на его выходе. Например, при появлении в двух предыдущих машинных циклах сигнала Запись в память на выходе блока 10 устанавливается код Q011 (табл.4).По этому коду выбирается информационный

ка 10 устанавливается код 1000. Так. как всегда Fg 0, то в следующем машинном цикле нулевой сигнал на выбранном входе мультиплексора 12 - (табл. 4) приводит к установке в активное состояние триггера 5 и формированию сигнала на выходе 6 устройства. Выход 6 ошибки устройства может соединяться с входом запроса прерывания МПС или использоваться каким-либо другим образом по усмотрению разработчика. В первом случае при возникновеII

15

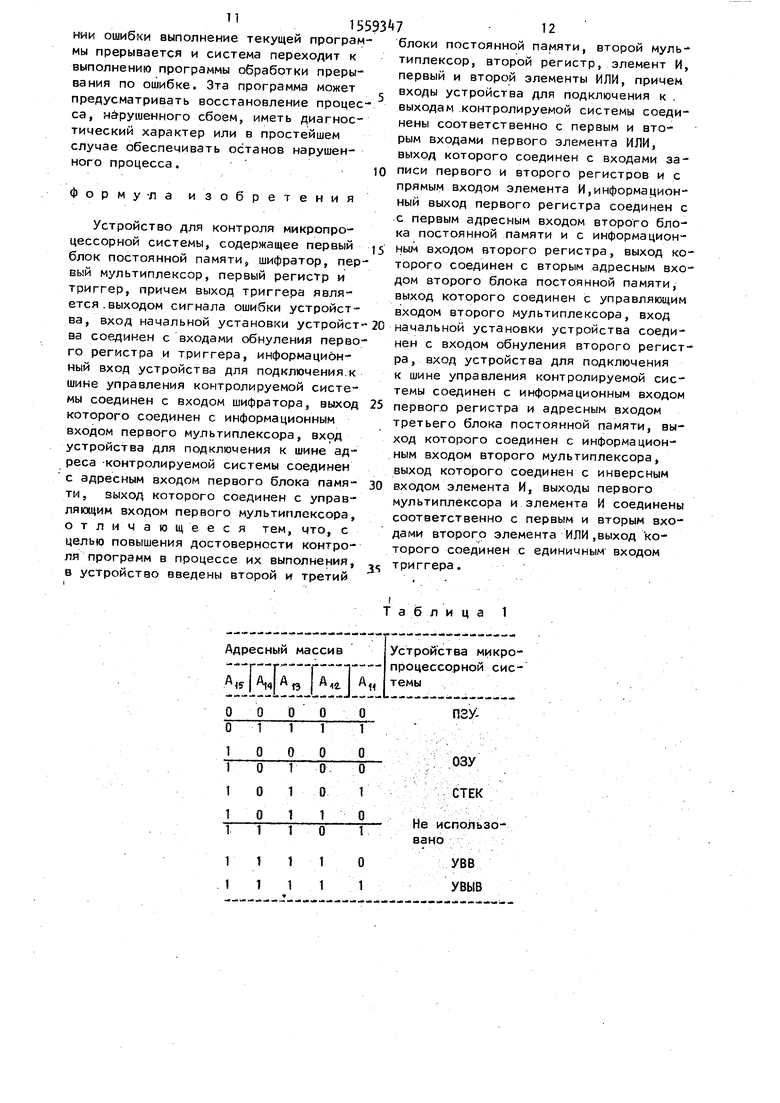

нии ошибки выполнение текущей программы прерывается и система переходит к выполнению программы обработки прерывания по ошибке. Эта программа может предусматривать восстановление процесса, нарушенного сбоем, иметь диагностический характер или в простейшем случае обеспечивать останов нарушенного процесса.

Форму-л а изобретения

Устройство для контроля микропроцессорной системы, содержащее первый блок постоянной памяти, шифратор, первый мультиплексор, первый регистр и триггер, причем выход триггера является выходом сигнала ошибки устройства, вход начальной установки устройст ва соединен с входами обнуления первого регистра и триггера, информационный вход устройства для подключения к шине управления контролируемой системы соединен с входом шифратора, выход которого соединен с информационным входом первого мультиплексора, вход устройства для подключения к шине адреса контролируемой системы соединен с адресным входом первого блока памя

ти, выход которого соединен с управляющим входом первого мультиплексора, отличающееся тем, что, с целью повышения достоверности контроля программ в процессе их выполнения, в устройство введены второй и третий

12

0

5

0 5

0

S

блоки постоянной памяти, второй мультиплексор, второй регистр, элемент И, первый и второй элементы ИЛИ, причем входы устройства для подключения к выходам контролируемой системы соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с входами записи первого и второго регистров и с прямым входом элемента И,информационный выход первого регистра соединен с с первым адресным входом второго блока постоянной памяти и с информационным входом второго регистра, выход которого соединен с вторым адресным входом второго блока постоянной памяти, выход которого соединен с управляющим входом второго мультиплексора, вход начальной установки устройства соединен с входом обнуления второго регистра, вход устройства для подключения к шине управления контролируемой системы соединен с информационным входом первого регистра и адресным входом третьего блока постоянной памяти, выход которого соединен с информационным входом второго мультиплексора, выход которого соединен с инверсным входом элемента И, выходы первого мультиплексора и элемента И соединены соответственно с первым и вторым входами второго элемента ИЛИ,выход которого соединен с единичным входом триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

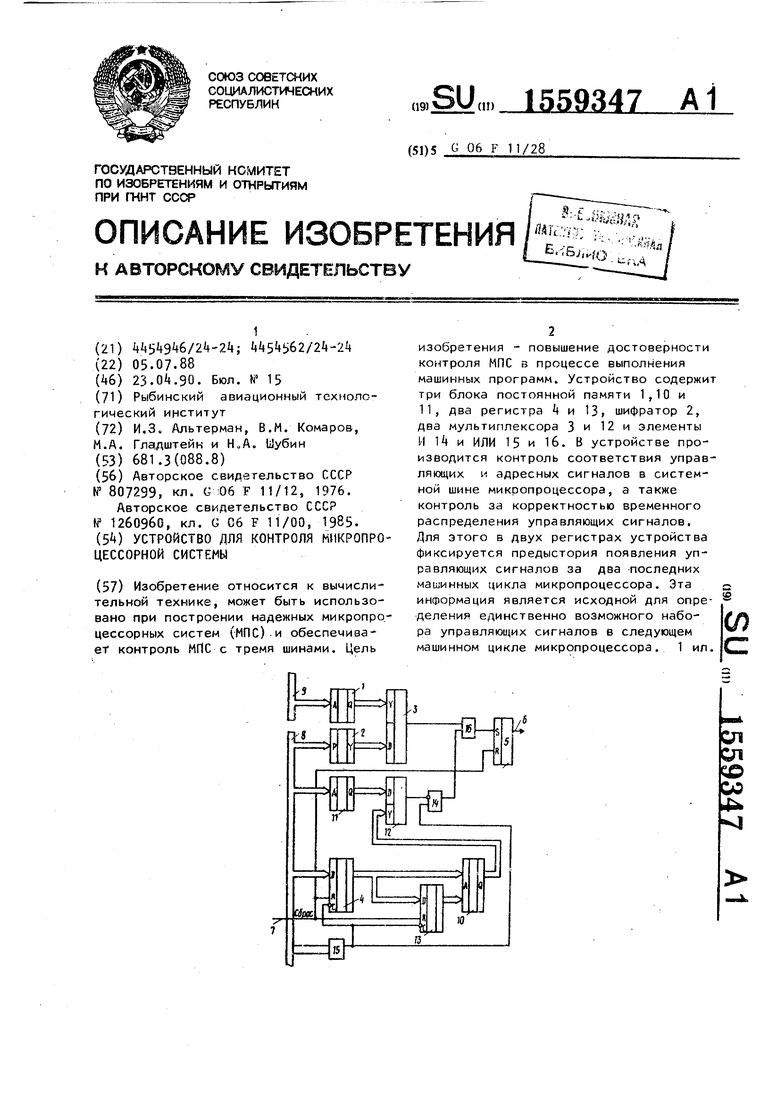

Изобретение относится к вычислительной технике, может быть использовано при построении надежных микропроцессорных систем (МПС) и обеспечивает контроль МПС с тремя шинами. Цель изобретения - повышение достоверности контроля МПС в процессе выполнения машинных программ. Устройство содержит три блока постоянной памяти 1,10 и 11, два регистра 4 и 13, шифратор 2, два мультиплексора 3 и 12 и элементы И 14 и ИЛИ 15 и 16. В устройстве производится контроль соответствия управляющих и адресных сигналов в системной шине микропроцессора, а также контроль за корректностью временного распределения управляющих сигналов. Для этого в двух регистрах устройства фиксируется предыстория появления управляющих сигналов за два последних машинных цикла микропроцессора. Эта информация является исходной для определения единственно возможного набора управляющих сигналов в следующем машинном цикле микропроцессора. 1 ил.

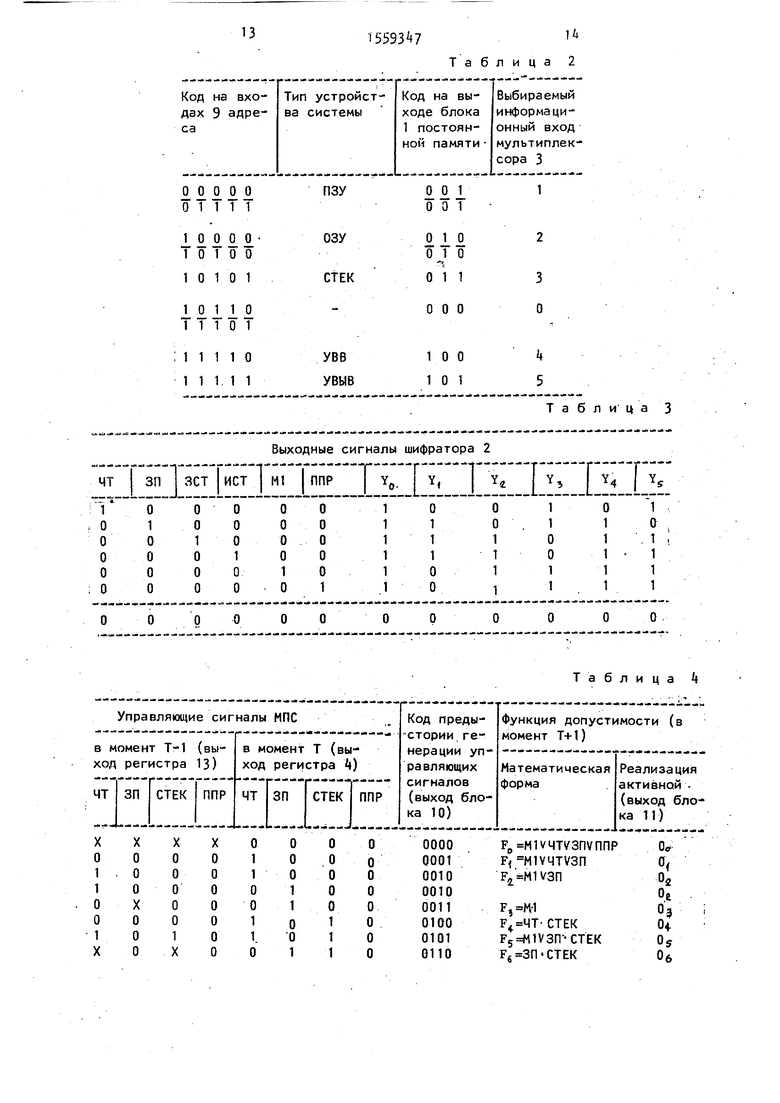

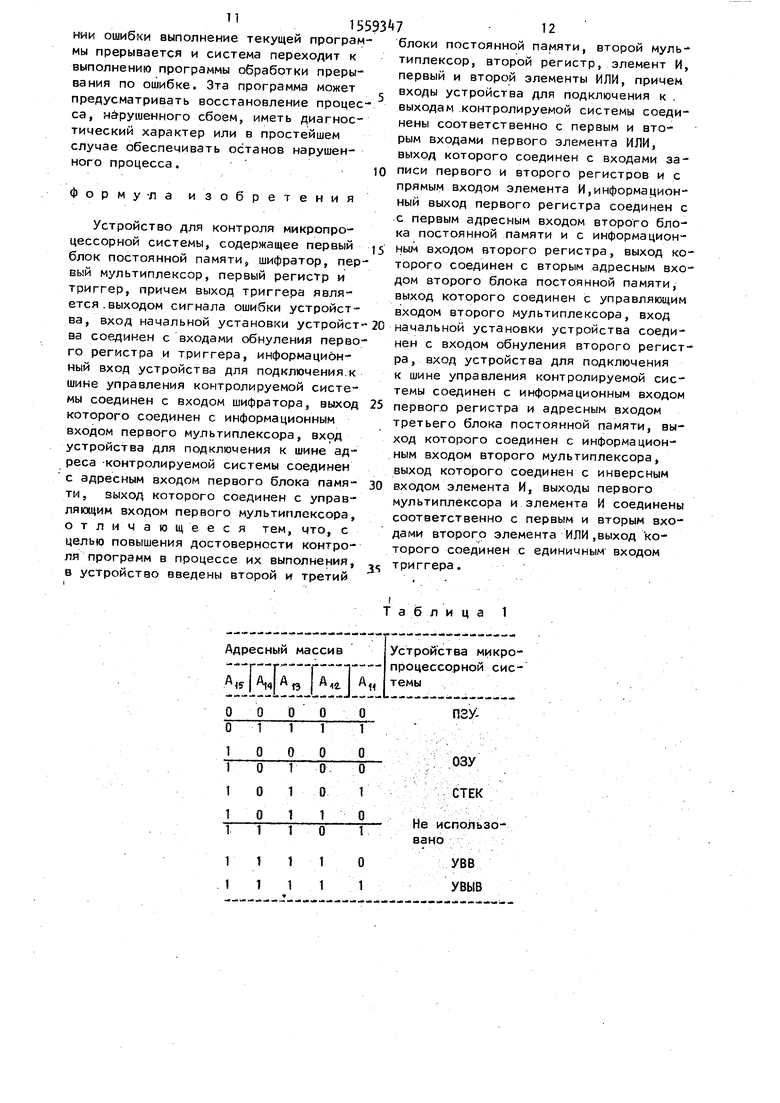

Адресный массив

Ч А

1 О

1

О

1 о

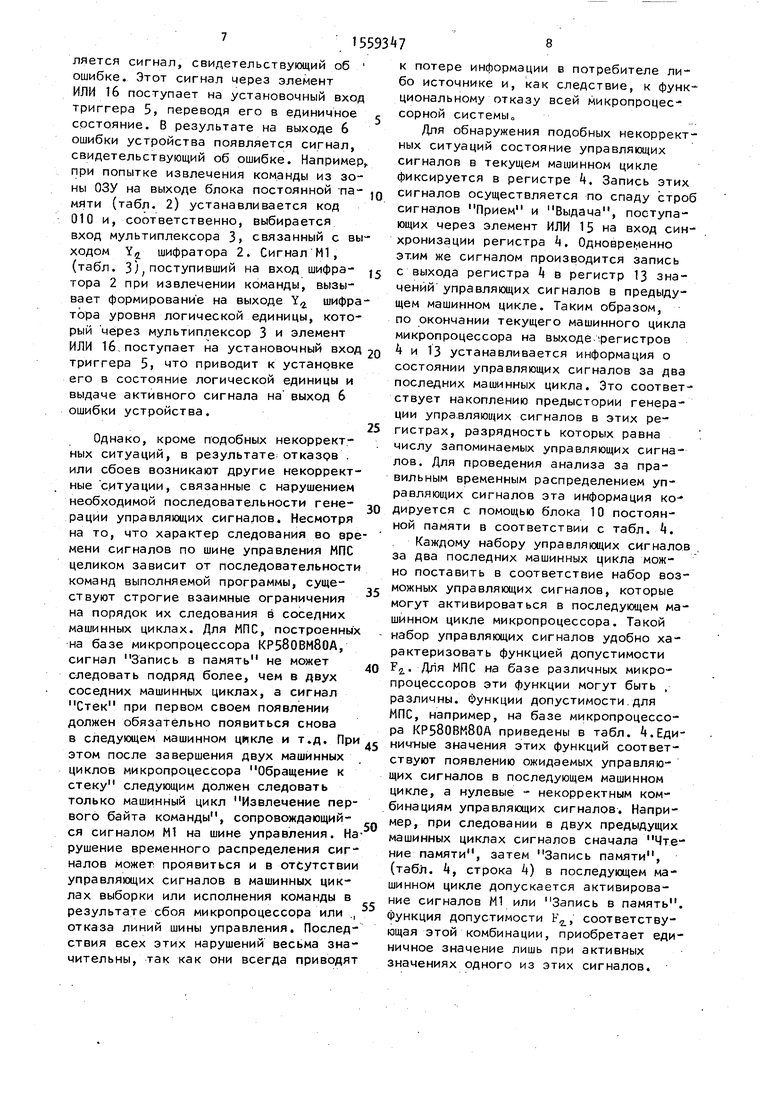

Таблица 1

Устройства микропроцессорной системы

пг

ОЗУ СТЕК

Не использовано

УВВ УБЫВ

13

Выходные сигналы шифратора 2

15593 7 k

Таблица 2

Таблица 3

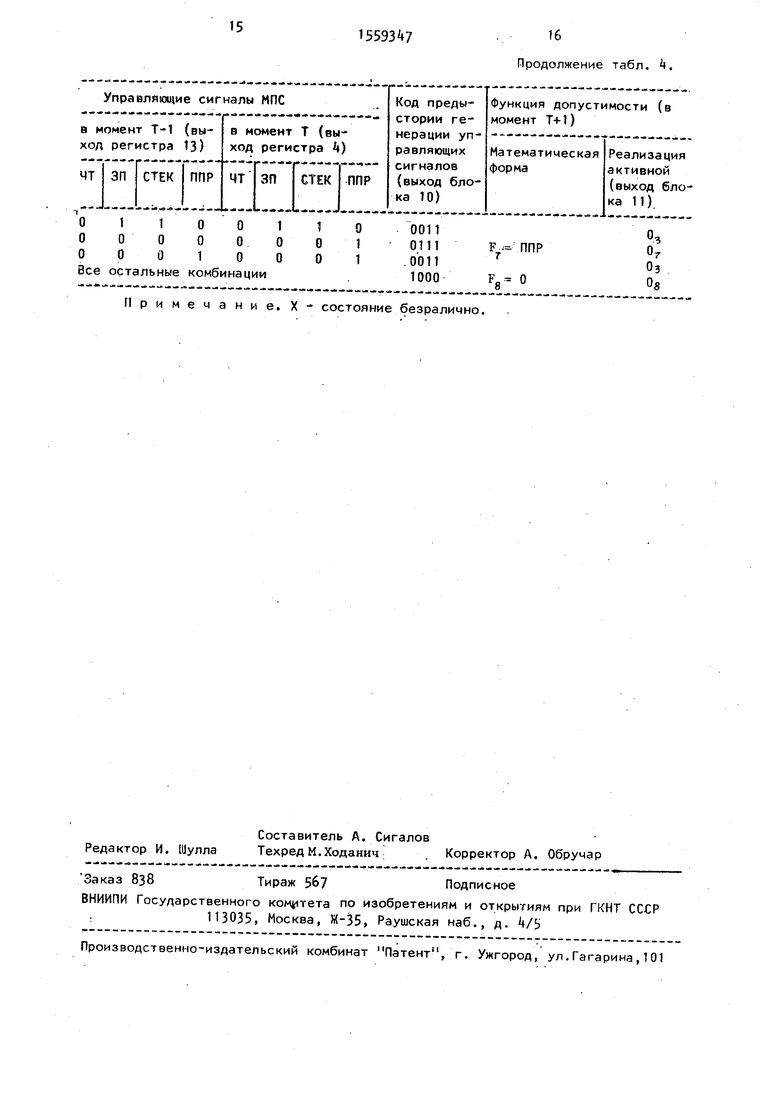

Таблица k

15

Примечание. Х- состояние безралично.

15593 7

16 Продолжение табл. Ь,

| Устройство для синтаксическогоКОНТРОля пРОгРАММ | 1978 |

|

SU807299A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ( УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ | |||

Авторы

Даты

1990-04-23—Публикация

1988-07-05—Подача