Изобретение относится к вычислительной технике и может быть использовано для контроля выполнения операций в устройствах управления и сопряжения.

Целью изобретения является сокращение оборудования.

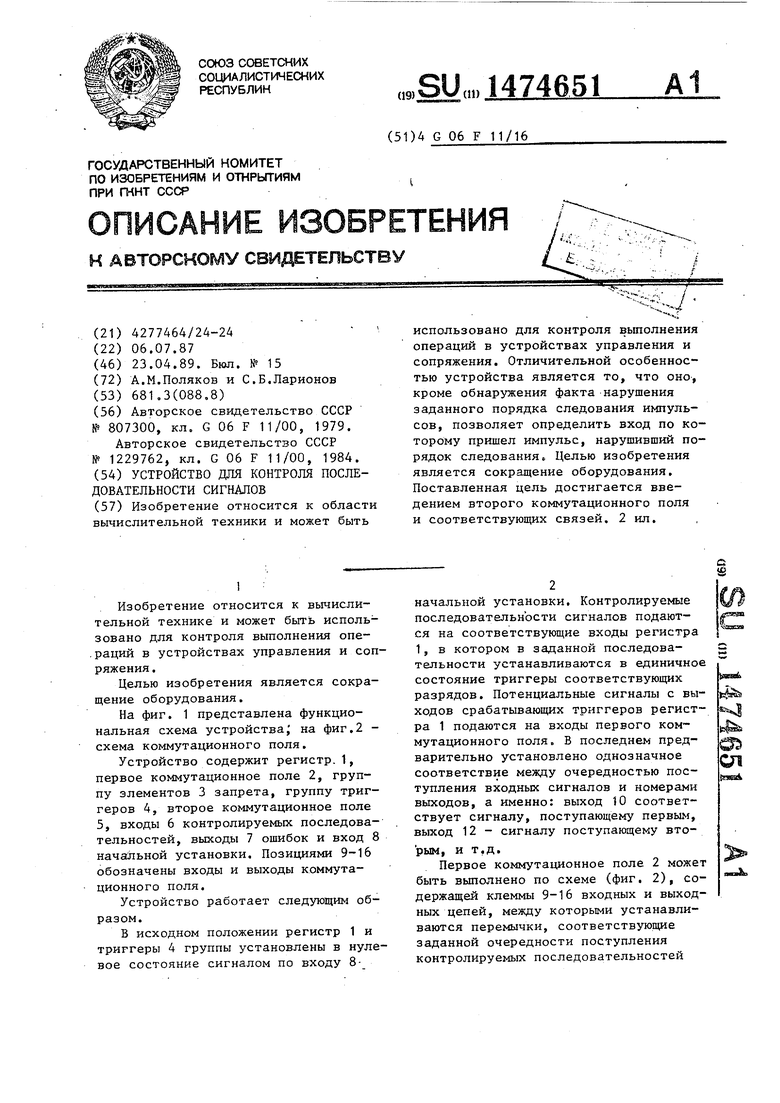

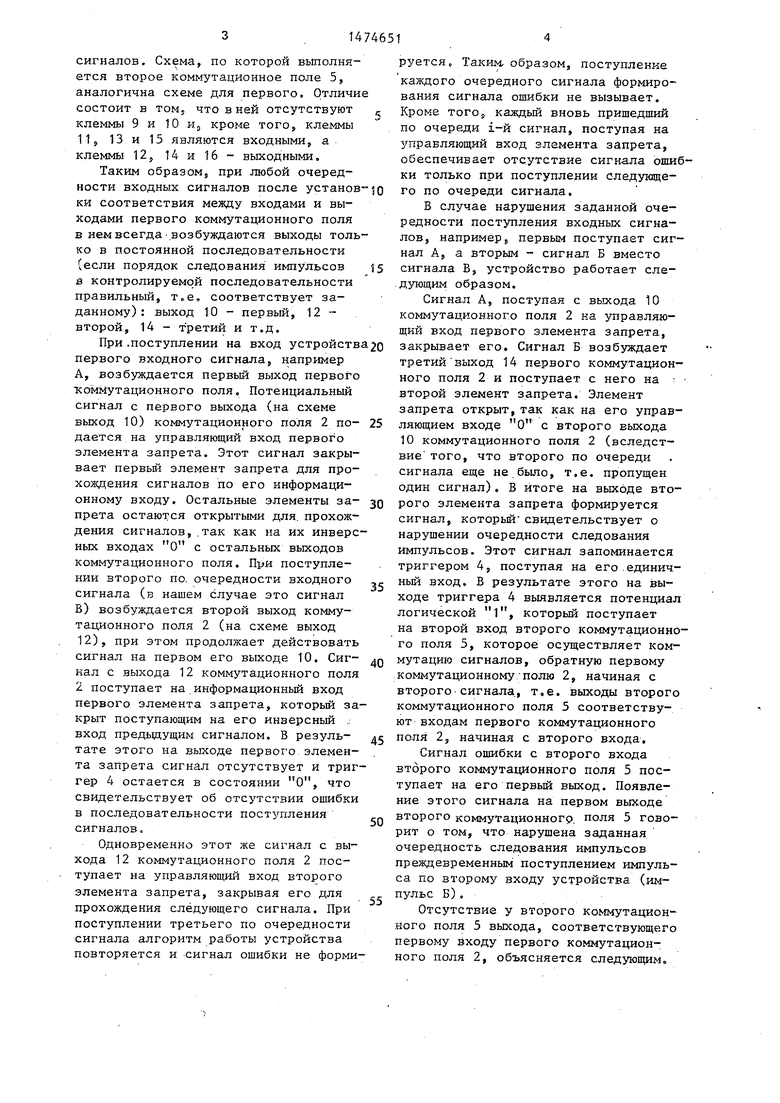

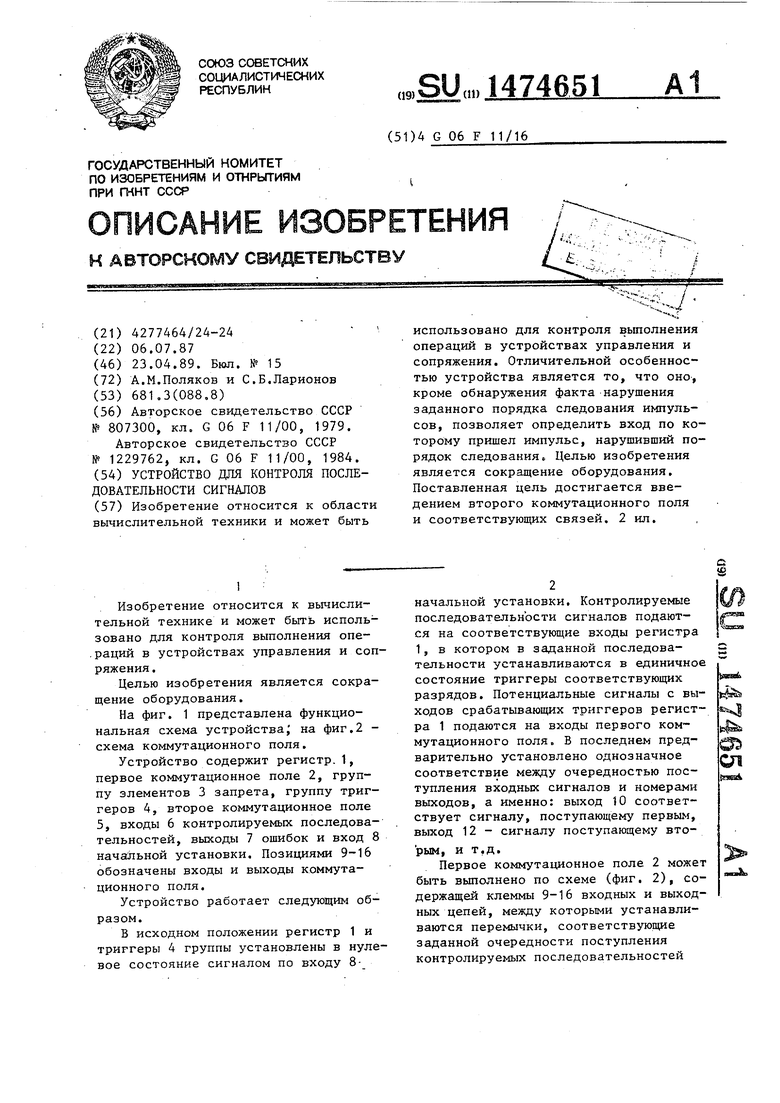

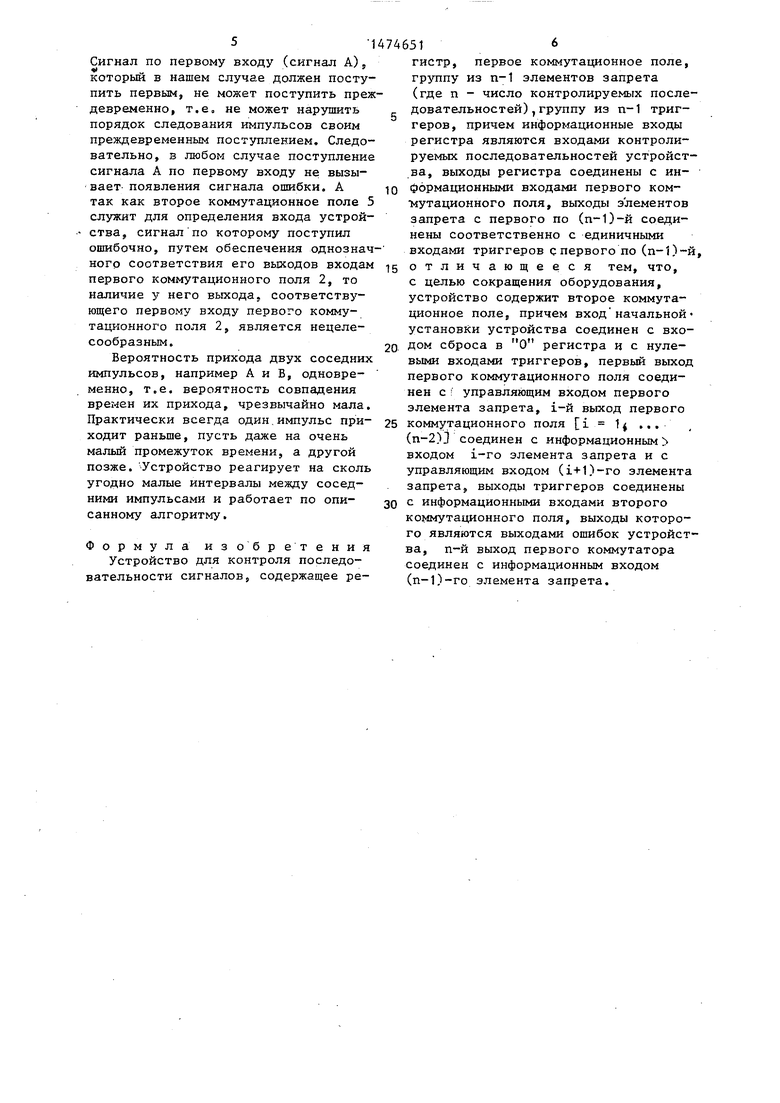

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - схема коммутационного поля.

Устройство содержит регистр 1, первое коммутационное поле 2, группу элементов 3 запрета, группу триггеров 4, второе коммутационное поле 5, входы 6 контролируемых последовательностей, выходы 7 ошибок и вход 8 начальной установки. Позициями 9-16 обозначены входы и выходы коммутационного поля.

Устройство работает следующим образом.

В исходном положении регистр 1 и триггеры 4 группы установлены в нулевое состояние сигналом по входу 8

начальной установки. Контролируемые последовательности сигналов подаются на соответствующие входы регистра 1, в котором в заданной последовательности устанавливаются в единичное состояние триггеры соответствующих разрядов. Потенциальные сигналы с выходов срабатывающих триггеров регистра 1 подаются на входы первого коммутационного поля. В последнем предварительно установлено однозначное соответствие между очередностью поступления входных сигналов и номерами выходов, а именно: выход 10 соответствует сигналу, поступающему первым, выход 12 - сигналу поступающему вторым, и т.д.

Первое коммутационное поле 2 может быть выполнено по схеме (фиг. 2), содержащей клеммы 9-16 входных и выходных цепей, между которыми устанавливаются перемычки, соответствующие заданной очередности поступления контролируемых последовательностей

6я&

сд

,

сигналов. Схема, по которой выполняется второе коммутационное поле 5, аналогична схеме для первого. Отличи состоит в том, что в ней отсутствуют клеммы 9 и 10 иа кроме того, клеммы 119 13 и 15 являются входными, а клеммы 12 5 14 и 16 - выходными.

Таким образом, при любой очередности входных сигналов после установ ки соответствия между входами и выходами первого коммутационного поля в нем всегда возбуждаются выходы только в постоянной последовательности (если порядок следования импульсов в контролируемой последовательности правильный, т.е. соответствует заданному): выход 10 - первый, 12 - второй, 14 - третий и т.д.

При .поступлении на вход устройств первого входного сигнала, например А, возбуждается первый выход первого тсоммутационного поля. Потенциальный сигнал с первого выхода (на схеме выход 10) коммутационного поля 2 по- дается на управляющий вход первого элемента запрета. Этот сигнал закрывает первьй элемент запрета для прохождения сигналов по его информационному входу. Остальные элементы за- прета остаются открытыми для прохождения сигналов, так как на их инверсных входах О с остальных выходов коммутационного поля. При поступлении второго по очередности входного сигнала (в нашем случае это сигнал В) возбуждается второй выход коммутационного поля 2 (на схеме выход 12), при этом продолжает действовать сигнал на первом его выходе 10. Сиг- кал с выхода 12 коммутационного поля 2 поступает на информационный вход первого элемента запрета, который закрыт поступающим на его инверсный вход предыдущим сигналом. В резуль- тате этого на выходе первого элемента запрета сигнал отсутствует и триггер 4 остается в состоянии О, что свидетельствует об отсутствии ошибки в последовательности поступления сигналов.

Одновременно этот же сигнал с выхода 12 коммутационного поля 2 поступает на управляющий вход второго элемента запрета, закрывая его для прохождения следующего сигнала. При поступлении третьего по очередности сигнала алгоритм работы устройства повторяется и сигнал ошибки не форми

,о 5

0

руется. Таким- образом, поступление каждого очередного сигнала формирования сигнала ошибки не вызывает. Кроме того9 каждый вновь пришедший по очереди i-й сигнал, поступая на управляющий вход элемента запрета, обеспечивает отсутствие сигнала ошибки только при поступлении следующего по очереди сигнала.

В случае нарушения заданной очередности поступления входных сигналов, например, первым поступает сигнал А, а вторым - сигнал Б вместо сигнала В, устройство работает следующим образом.

Сигнал А, поступая с выхода 10 коммутационного поля 2 на управляющий вход первого элемента запрета, закрывает его. Сигнал Б возбуждает третий выход 14 первого коммутационного поля 2 и поступает с него на второй элемент запрета. Элемент запрета открыт, так как на его управ- ляющием входе О с второго выхода 10 коммутационного поля 2 (вследствие того, что второго по очереди сигнала еще не было, т.е. пропущен один сигнал). В итоге на выходе второго элемента запрета формируется сигнал, который свидетельствует о нарушении очередности следования импульсов. Этот сигнал запоминается триггером 4, поступая на его единичный вход. В результате этого на выходе триггера 4 выявляется потенциал логической 1, который поступает на второй вход второго коммутационного поля 5, которое осуществляет коммутацию сигналов, обратную первому коммутационному полю 2, начиная с второго сигнала, т.е. выходы второго коммутационного поля 5 соответствуют входам первого коммутационного поля 2, начиная с второго входа.

Сигнал ошибки с второго входа второго коммутационного поля 5 поступает на его первый выход. Появление этого сигнала на первом выходе второго коммутационногр поля 5 говорит о том, что нарушена заданная очередность следования импульсов преждевременным поступлением импульса по второму входу устройства (импульс Б).

Отсутствие у второго коммутационного поля 5 выхода, соответствующего первому входу первого коммутационного поля 2, объясняется следующим.

Сигнал по первому входу (сигнал А), который в нашем случае должен поступить первым, не может поступить преждевременно, т.е„ не может нарушить порядок следования импульсов своим преждевременным поступлением. Следовательно, в любом случае поступление сигнала А по первому входу не вызывает появления сигнала ошибки. А так как второе коммутационное поле 5 служат для определения входа устройства, сигнал по которому поступил ошибочно, путем обеспечения однозначного соответствия его выходов входам первого коммутационного поля 2, то наличие у него выхода, соответствующего первому входу первого коммутационного поля 2, является нецелесообразным.

Вероятность прихода двух соседних импульсов, например А и В, одновременно, т.е. вероятность совпадения времен их прихода, чрезвычайно мала. Практически всегда один импульс приходит раньше, пусть даже на очень малый промежуток времени, а другой позже. Устройство реагирует на сколь угодно малые интервалы между соседними импульсами и работает по описанному алгоритму.

Формула изобретения

Устройство для контроля последовательности сигналов, содержащее ре4746516

гистр, первое коммутационное поле, группу из п-1 элементов запрета (где п - число контролируемых последовательностей) , группу из п-1 триггеров, причем информационные входы регистра являются входами контролируемых последовательностей устройства, выходы регистра соединены с ин10 Формационными входами первого коммутационного поля, выходы элементов запрета с первого по (п-1)-и соединены соответственно с единичными входами триггеров с первого по (п-1)-и,

15 отличающееся тем, что, с целью сокращения оборудования, устройство содержит второе коммутационное поле, причем вход начальной установки устройства соединен с вхо2о дом сброса в О регистра и с нулевыми входами триггеров, первый выход первого коммутационного поля соединен с управляющим входом первого элемента запрета, i-й выход первого

25 коммутационного поля i 1 $ ... (п-2)3 соединен с информационным входом 1-го элемента запрета и с управляющим входом (i+1)-ro элемента запрета, выходы триггеров соединены

30 с информационными входами второго коммутационного поля, выходы которого являются выходами ошибок устройства, n-й выход первого коммутатора соединен с информационным входом (п-1)-го элемента запрета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования систем человек-машина | 1986 |

|

SU1348848A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1647573A1 |

| Устройство для ввода информации | 1984 |

|

SU1259240A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1723661A1 |

| Устройство для обнаружения ошибок при передаче кодов | 1989 |

|

SU1615723A2 |

| Устройство для контроля микропроцессора | 1988 |

|

SU1599862A1 |

| Устройство для ввода информации | 1987 |

|

SU1474630A1 |

| Устройство для контроля последовательности прохождения сигналов | 1990 |

|

SU1734095A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

Изобретение относится к области вычислительной техники и может быть использовано для контроля выполнения операций в устройствах управления и сопряжения. Отличительной особенностью устройства является то, что оно, кроме обнаружения факта нарушения заданного порядка следования импульсов, позволяет определить вход, по которому пришел импульс, нарушивший порядок следования. Целью изобретения является сокращение оборудования. Поставленная цель достигается введением второго коммутационного поля и соответствующих связей. 2 ил.

| Устройство для контроля выполненияпОСлЕдОВАТЕльНОСТи дЕйСТВий ОпЕРАТОРА | 1978 |

|

SU807300A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля последовательности сигналов | 1984 |

|

SU1229762A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-23—Публикация

1987-07-06—Подача