.и

па

4

4

00

СО 00

Изобретение относится к автоматике и вычислительной технике и может быть использовано для управления различными устройствами, в том чис- ле и внешними устройствами вычислительных комплексов

Цель изобретения - расширение области применения за счет моделирования последовательности управляющих сигналов в любом сочетании

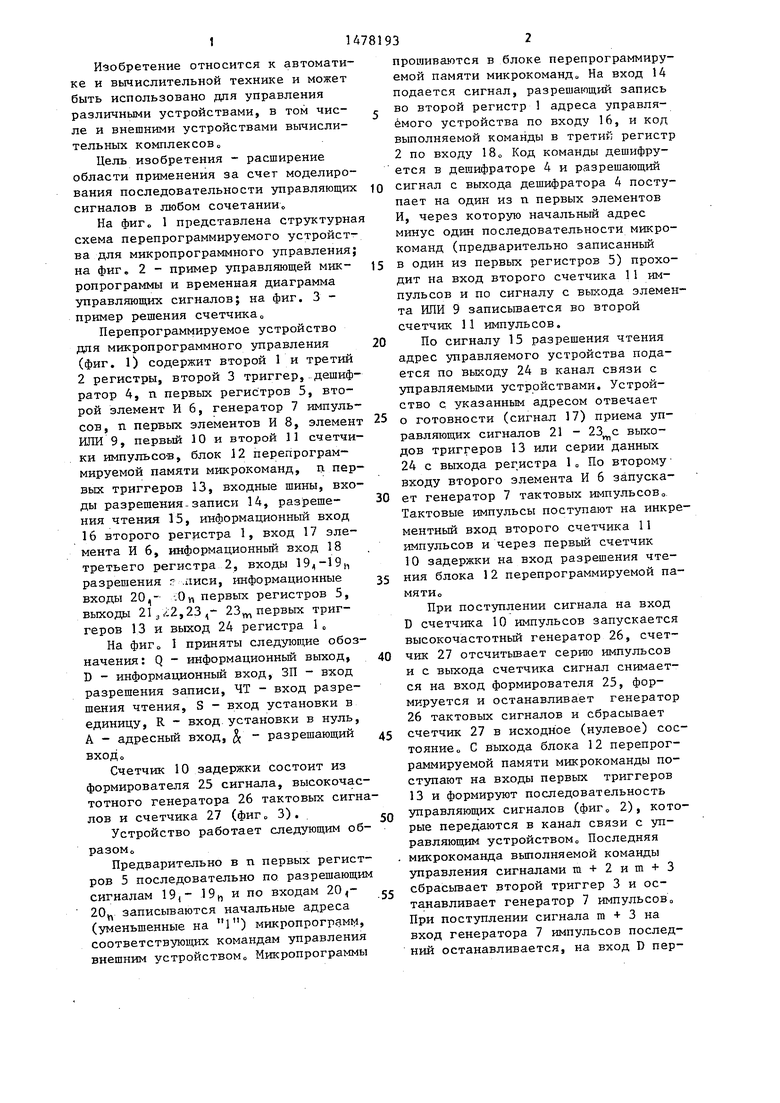

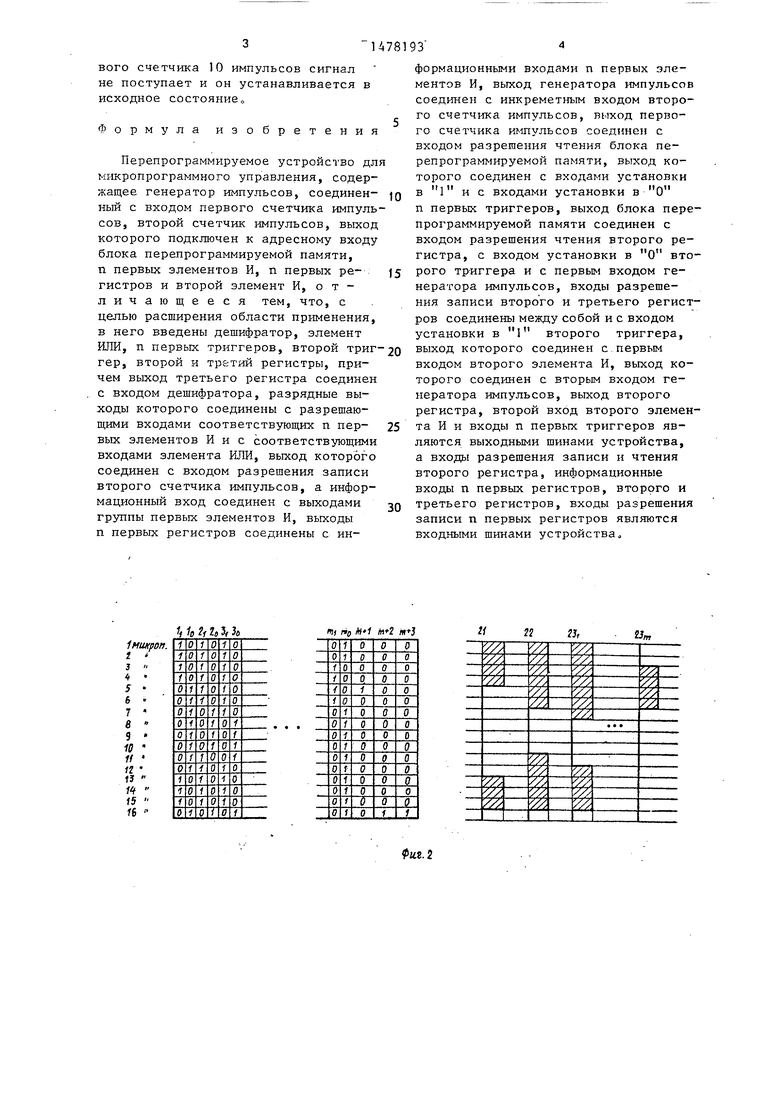

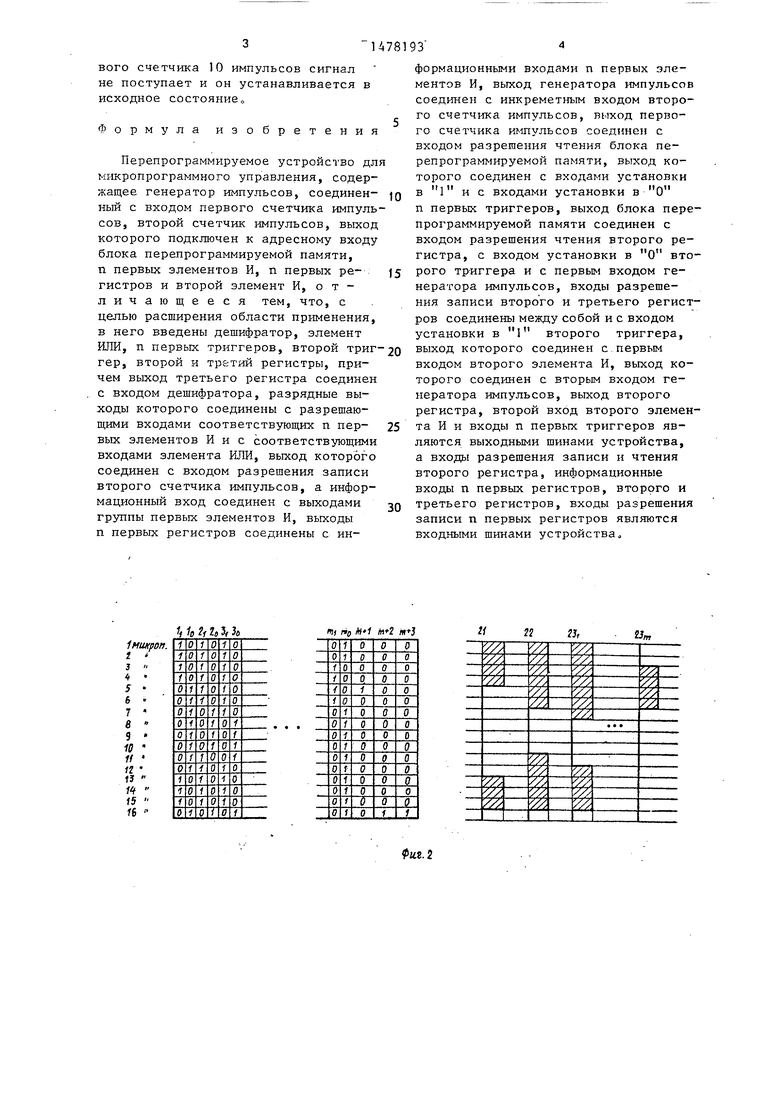

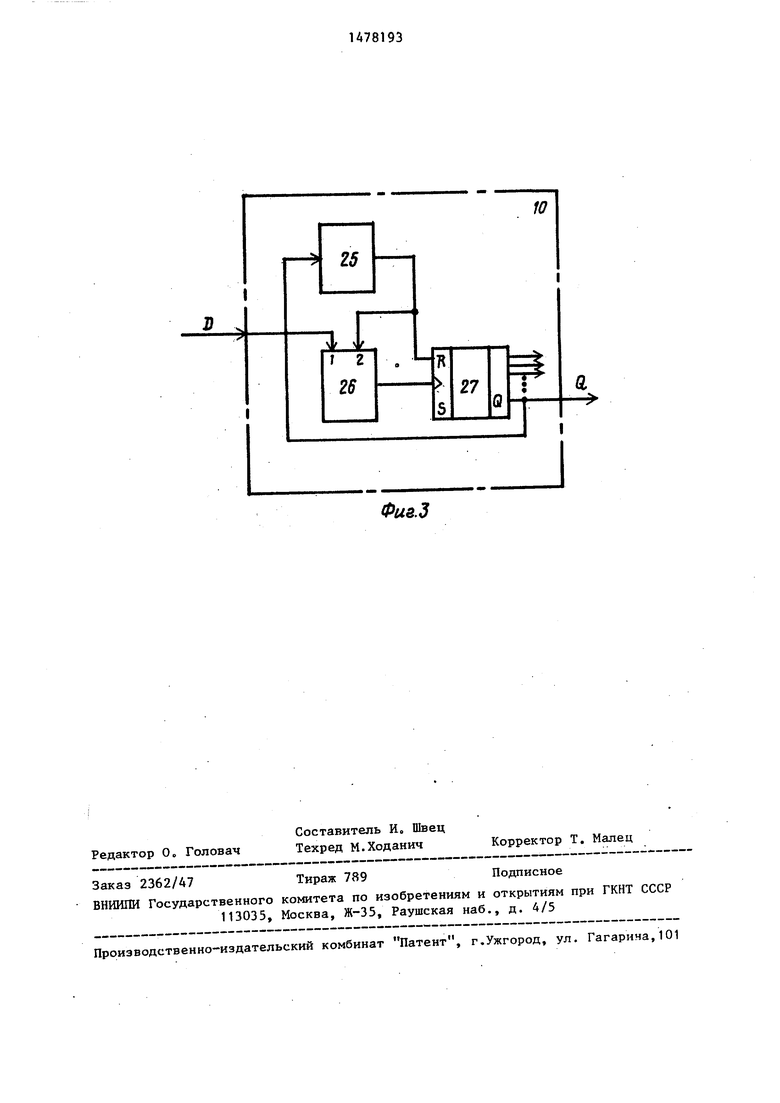

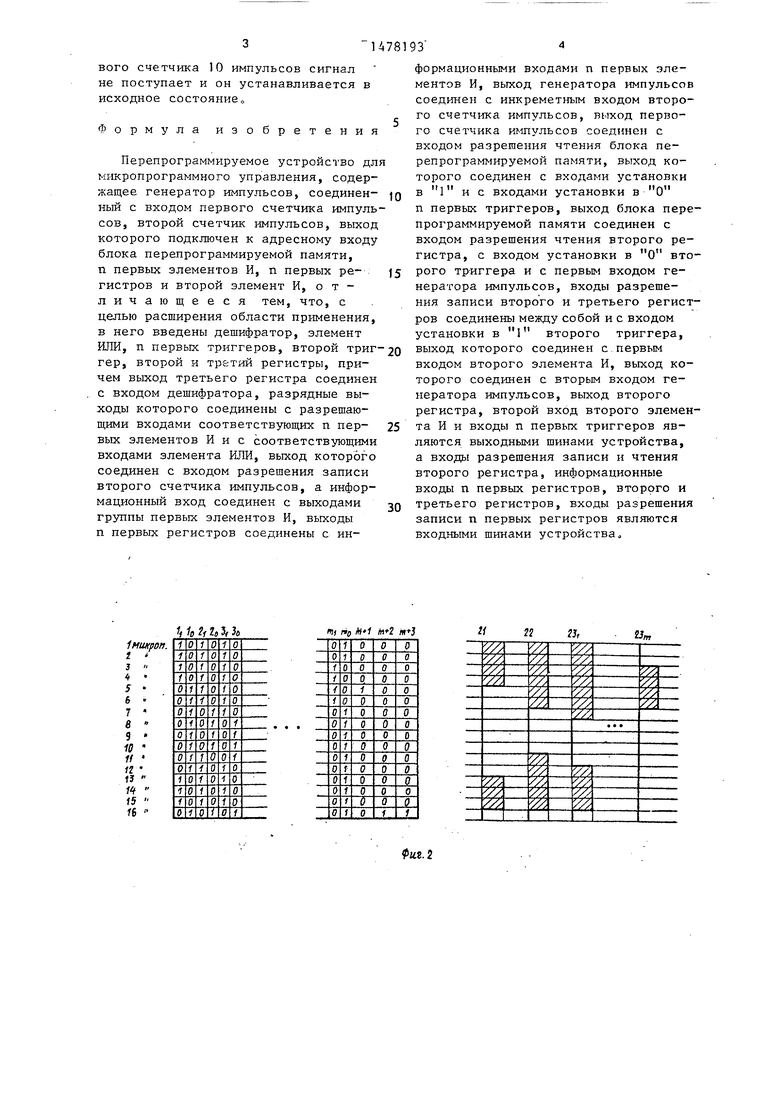

На фиг„ 1 представлена структурна схема перепрограммируемого устройства для микропрограммного управления; на фиг. 2 - пример управляющей мик- ропрограммы и временная диаграмма управляющих сигналов; на фиг. 3 - пример решения счетчика

Перепрограммируемое устройство для микропрограммного управления (фиг. 1) содержит второй 1 и третий 2 регистры, второй 3 триггер, дешифратор 4, п первых регистров 5, второй элемент И 6, генератор 7 импульсов, п первых элементов И 8, элемент ИЛИ 9, первый 10 и второй 11 счетчики импульсо-в, блок 12 перепрограммируемой памяти микрокоманд, п первых триггеров 13, входные шины, входы разрешения-записи 14, разреше- ния чтения 15, информационный вход 16 второго регистра 1, вход 17 элемента И 6, информационный вход 18 третьего регистра 2, входы 19 ,,-19,4 разрешения г лиси, информационные входы 20,- -Ом первых регистров 5, выходы 21.2,23,- 23т первых триггеров 13 и выход 24 регистра 1„

На фиг о 1 приняты следующие обозначения: Q - информационный выход, D - информационный вход, ЗП - вход разрешения записи, ЧТ - вход разрешения чтения, S - вход установки в единицу, R - вход установки в нуль, А - адресный вход, $ - разрешающий вход

Счетчик 10 задержки состоит из формирователя 25 сигнала, высокочастотного генератора 26 тактовых сигналов и счетчика 27 (фиг„ 3).

Устройство работает следующим об- разомо

Предварительно в п первых регистров 5 последовательно по разрешающим сигналам 19,- 19П и по входам 20,- 20П записываются начальные адреса (уменьшенные на 1) микропрограмм, соответствующих командам управления внешним устройствомо Микропрограммы

прошиваются в блоке перепрограммируемой памяти микрокоманд На вход 14 подается сигнал, разрешающий запись во второй регистр 1 адреса управляемого устройства по входу 16, и код выполняемой команды в третий регист 2 по входу 180 Код команды дешифруется в дешифраторе 4 и разрешающий сигнал с выхода дешифратора 4 поступает на один из п первых элементов И, через которую начальный адрес минус один последовательности микрокоманд (предварительно записанный в один из первых регистров 5) проходит на вход второго счетчика 11 импульсов и по сигналу с выхода элемета ИЛИ 9 записывается во второй счетчик 11 импульсов.

По сигналу 15 разрешения чтения адрес управляемого устройства подается по выходу 24 в канал связи с управляемыми устройствами. Устройство с указанным адресом отвечает о готовности (сигнал 17) приема управляющих сигналов 21 - 23гпс выходов триггеров 13 или серии данных 24 с выхода регистра 1„ По второму входу второго элемента И 6 запускает генератор 7 тактовых импульсов„ Тактовые импульсы поступают на инкр ментный вход второго счетчика 11 импульсов и через первый счетчик 10 задержки на вход разрешения чтения блока 12 перепрограммируемой памяти о

При поступлении сигнала на вход D счетчика 10 импульсов запускается высокочастотный генератор 26, счетчик 27 отсчитьюает серию импульсов и с выхода счетчика сигнал снимается на вход формирователя 25, формируется и останавливает генератор 26 тактовых сигналов и сбрасывает счетчик 27 в исходное (нулевое) состояние С выхода блока 12 перепрограммируемой памяти микрокоманды поступают на входы первых триггеров 13 и формируют последовательность управляющих сигналов (фиг 2), которые передаются в канал связи с управляющим устройством Последняя микрокоманда выполняемой команды управления сигналами га + 2 и m + 3 сбрасывает второй триггер 3 и останавливает генератор 7 импульсов При поступлении сигнала m + 3 на вход генератора 7 импульсов последний останавливается, на вход D первого счетчика 10 импульсов сигнал не поступает и он устанавливается в исходное состояние„

Формула изобретения

Перепрограммируемое устройство дл микропрограммного управления, содержащее генератор импульсов, соединен- ньш с входом первого счетчика импульсов, второй счетчик импульсов, выход которого подключен к адресному входу блока перепрограммируемой памяти, п первых элементов И, п первых ре- гистров и второй элемент { отличающееся тем, что, с целью расширения области применения, в него введены дешифратор, элемент ИЛИ, п первых триггеров, второй триг гер, второй и третий регистры, причем выход третьего регистра соединен с входом дешифратора, разрядные выходы которого соединены с разрешающими входами соответствующих п пер- вых элементов И и с соответствующими входами элемента ИЛИ, выход которого соединен с входом разрешения записи второго счетчика импульсов, а информационный вход соединен с выходами группы первых элементов И, выходы п первых регистров соединены с информационными входами п первых элементов И, выход генератора импульсов соединен с инкреметным входом второго счетчика импульсов, выход первого счетчика импульсов соединен с входом разрешения чтения блока перепрограммируемой памяти, выход которого соединен с входами установки в 1 и с входами установки в О п первых триггеров, выход блока перепрограммируемой памяти соединен с входом разрешения чтения второго регистра, с входом установки в О второго триггера и с первым входом генератора импульсов, входы разрешения записи второго и третьего регистров соединены между собой и с входом

установки в 1 второго триггера, выход которого соединен с первым входом второго элемента И, выход которого соединен с вторым входом генератора импульсов, выход второго регистра, второй вход второго элемента И и входы п первых триггеров являются выходными шинами устройства, а входы разрешения записи и чтения второго регистра, информационные входы п первых регистров, второго и третьего регистров, входы разрешения записи п первых регистров являются входными шинами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Вычислительное устройство для диагностики состояния больных | 1990 |

|

SU1725229A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1987 |

|

SU1442996A1 |

| Устройство для перевода выражений в польскую инверсную запись | 1982 |

|

SU1130879A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для управления различными устройствами, в том числе и внешними устройствами вычислительных комплексов. Цель изобретения - расширение области применения за счет моделирования последовательности управляющих сигналов в любом сочетании. Перепрограммируемое устройство для микропрограммного управления содержит регистры 1,2, дешифратор 4, N первых регистров 5, второй элемент И 6, генератор импульсов 7, N первых элементов И 8, элемент ИЛИ 9, блок 12 перепрограммируемой памяти микрокоманд, N первых триггеров 13, первый 10 и второй 11 счетчики импульсов, триггер 3. Данное устройство позволяет моделировать последовательность управляющих сигналов в любом сочетании. 3 ил.

mi п0 т+3

1микро

3 4 5

ь

7

В

9

10

1f

12

13

It

15

16

Фиг.З

| Программируемый контроллер | 1984 |

|

SU1208536A1 |

Авторы

Даты

1989-05-07—Публикация

1987-03-04—Подача