Изобретение относится к вычислительной технике, а именно к буферным запоминающим устройствам, и может быть использовано для промежуточного хранения информации при передаче информации по каналу связи.

Цель изобретения - расширение области применения устройства за счет асинхронного приема и выдачи данных по каналам.

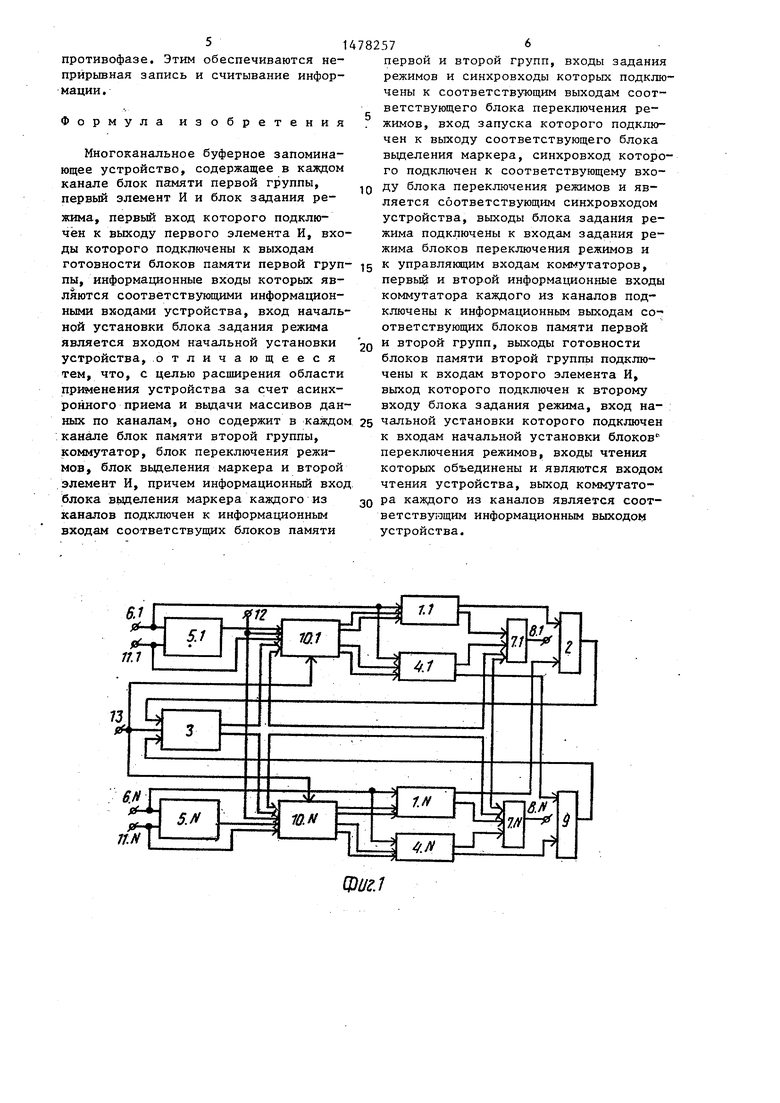

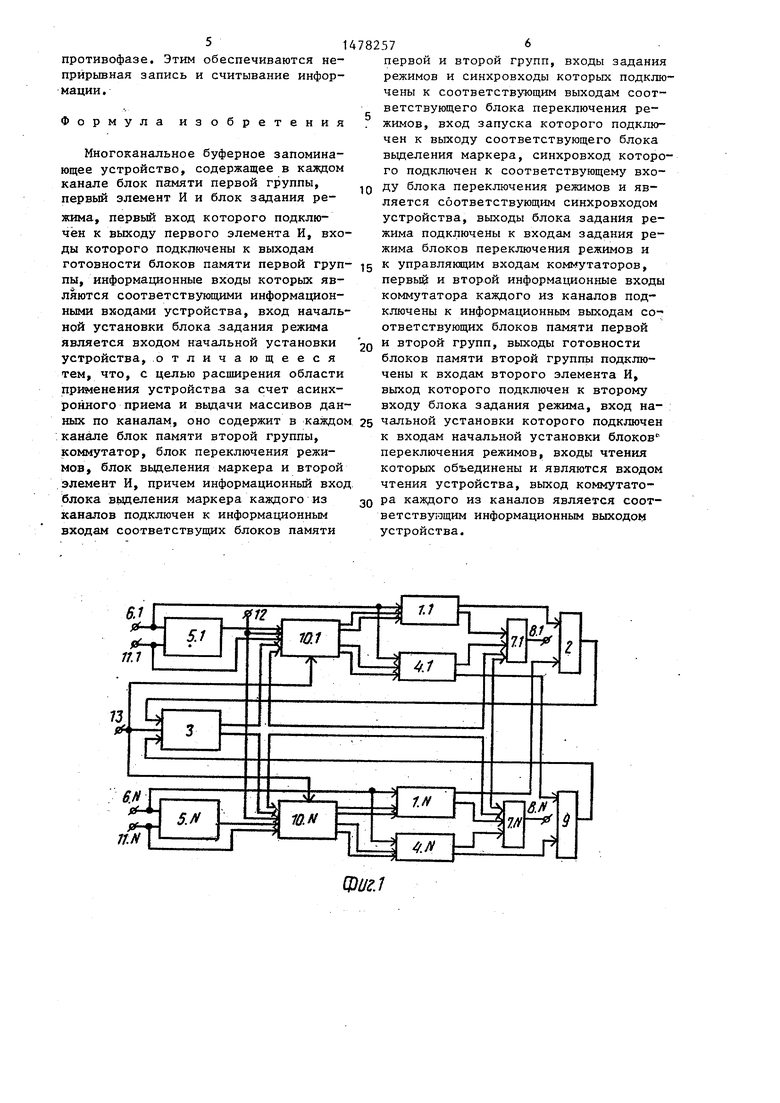

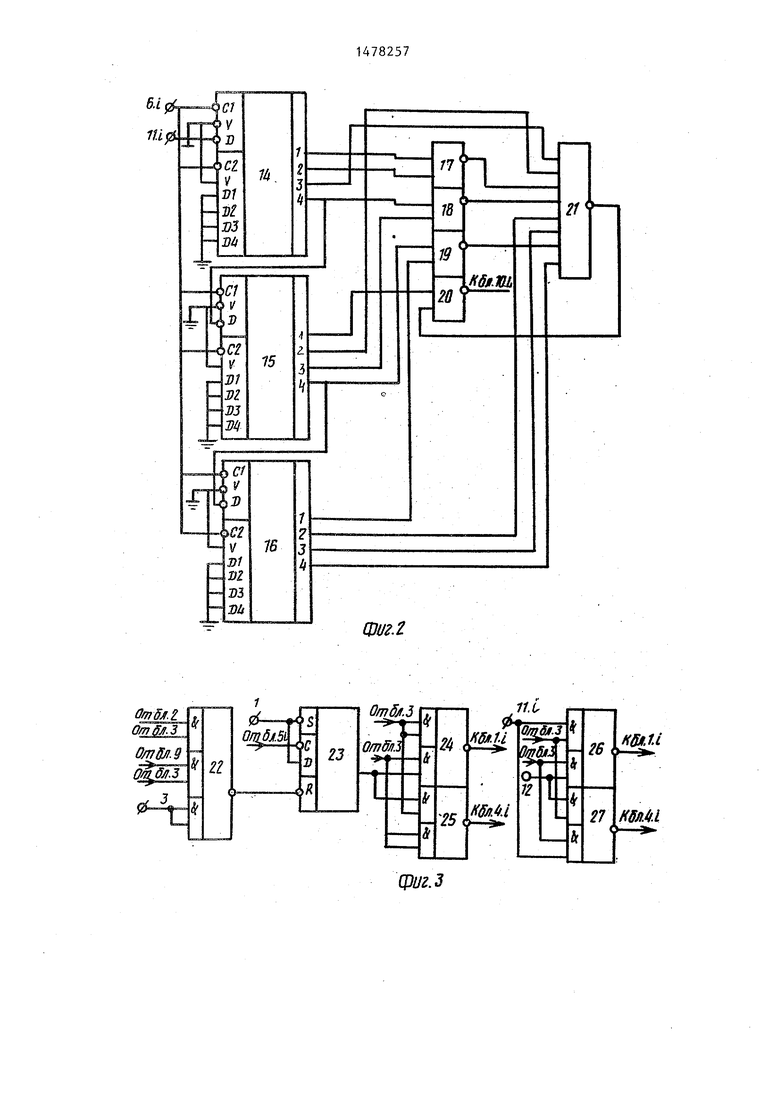

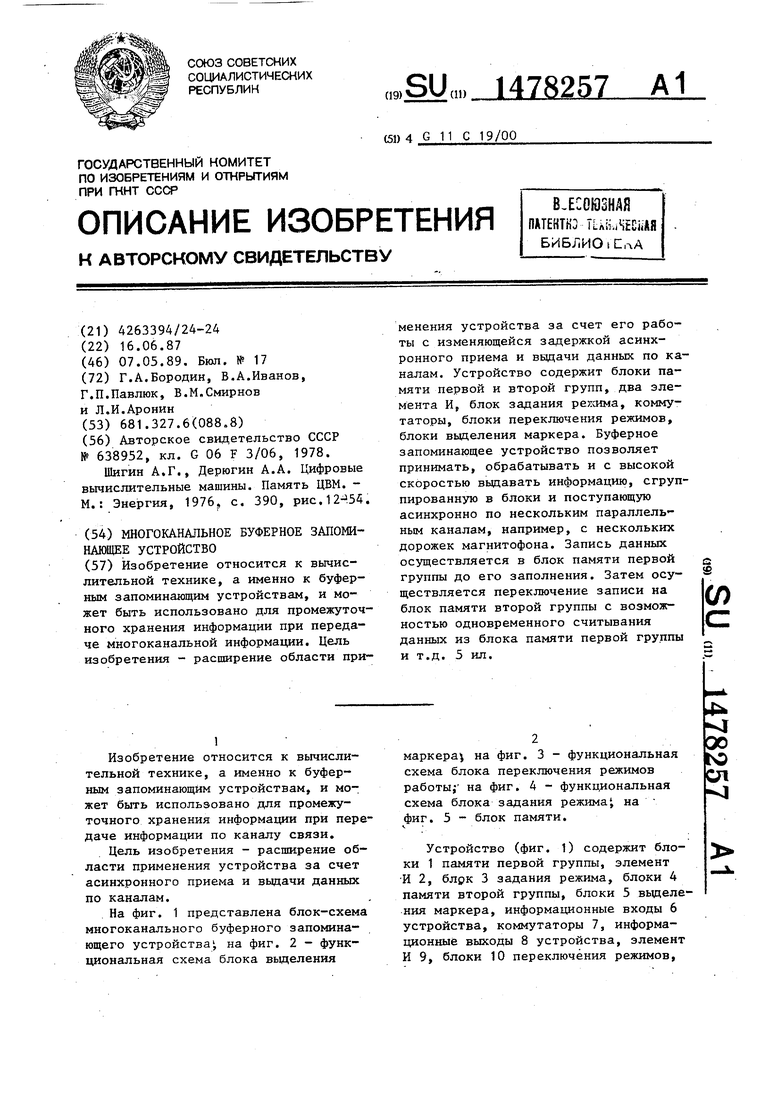

На фиг. 1 представлена блок-схема многоканального буферного запоминающего устройства1, на фиг. 2 - функциональная схема блока выделения

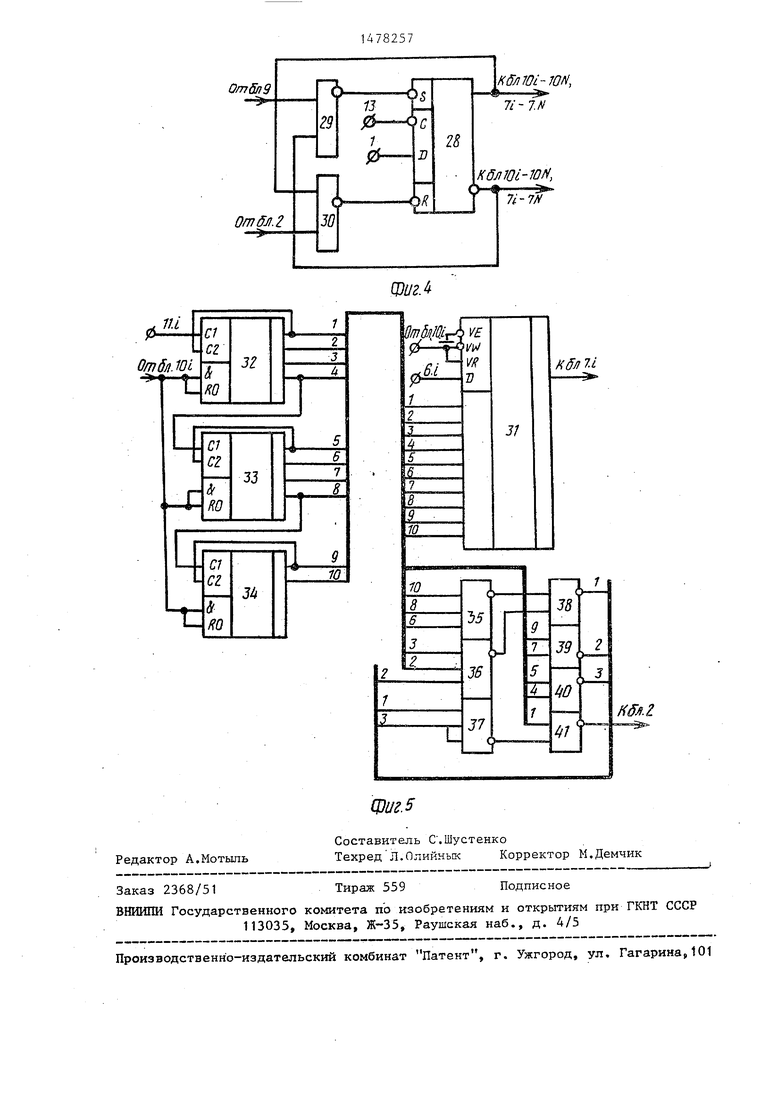

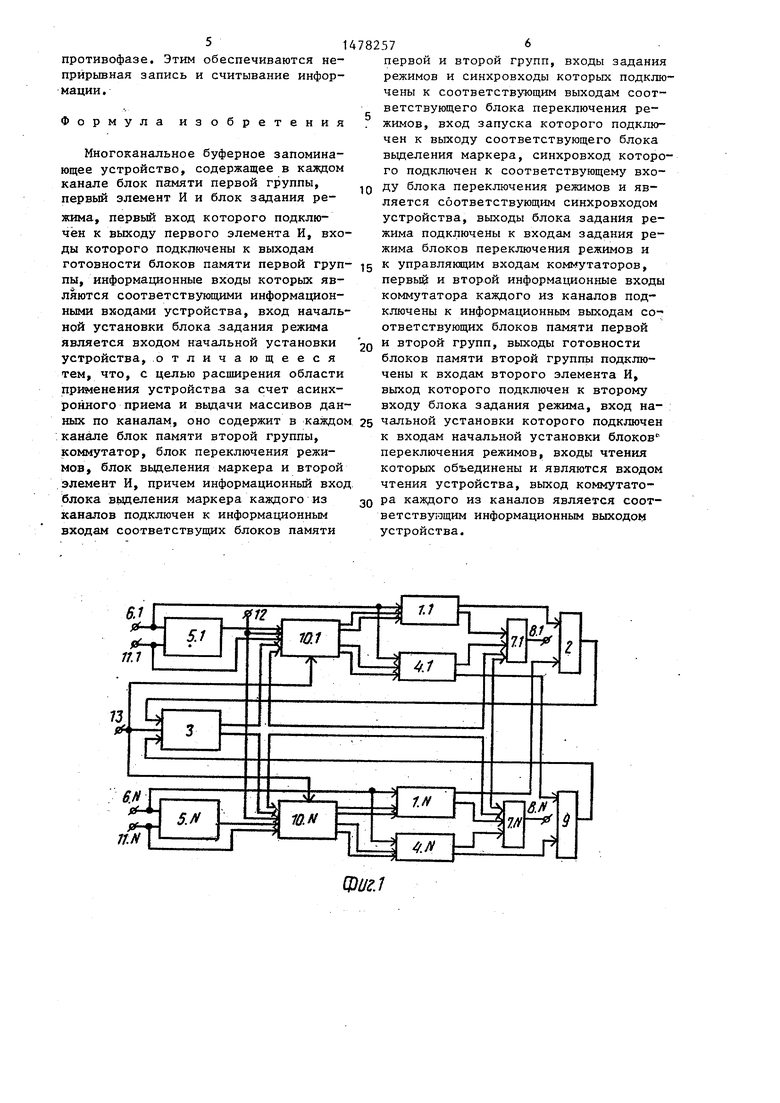

маркера на фиг. 3 - функциональная схема блока переключения режимов работы, на фиг. 4 - функциональная схема блока задания режима , на фиг. 5 - блок памяти.

v

Устройство (фиг. 1) содержит блоки 1 памяти первой группы, элемент И 2, блрк 3 задания режима, блоки 4 памяти второй группы, блоки 5 выделения маркера, информационные входы 6 устройства, коммутаторы 7, информационные выходы 8 устройства, элемент И 9, блоки 10 переключения режимов,

синхровходы 11 устройства, вход 12 чтения и вход 13 начальной установки

Каждый блок 5 выделения маркера (фиг, 2) содержит сдвиговые регистры 14-16, элементы ИЛИ-НЕ 17-20 и элемент И-НЕ 21.

Каждый блок 10 переключения режимов (фиг. 3) содержит элемент 2И- ЗИЛИ-НЕ 22, триггер 23 и элементы 2И-2ИЛИ-НЕ 24-27.

Блок 3 задания режима (фиг. 4) содержит триггер 28 и элементы 2И- НЕ 29 и 30.

Каждый из блоков 1 и 4 памяти (фиг. 5) содержит накопители 31-34, элементы ЗИ-НЕ 35-37 и элементы 2ИЛИ-НЕ 38-41.

Многоканальное буферное запоминающее устройство работает следующим образом,,

Записываемая информация представляет собой 662 двадцатипятиразрядных слова - блок информации, двадцать пятый разряд контрольный. Начало считываемой информации по каждому, каналу определяется маркером - двенадцать разрядов (111000100100). Запись информации- по каждому из каналов происходит независимо друг от друга. Первый блок информации записывается в блок 1 памяти первой группы второй блок информации записывается в блок 4 памяти второй группы, третий блок информации - в блок 1 памяти, четвертый блок информации - в блок 4 памяти и т.д.

Режим начальной установки. В начальный момент времени буферное запоминающее устройство устанавливается в режим записи в блок 1 памяти первой группы. Сигнал на входе начальной установки устройства 13 устанавливает триггер 28 (фиг, 4) в единичное состояние (прямой выход триггера 28 - сигнал ЗГИ, инверсный выход - сигнал ЗП2),, триггер 23 (фиг. 3) - в нулевое состояние, а счетчики 32-34 адреса блока 4 памяти (фиг. 5) - в нерабочее состояние.

Режим записи. Считываемые с магнитной ленты данные по входу 6 поступают на сдвиговые регистры 14-16 блока 5 выделения маркера (фиг. 2). Информация с регистра поступает на элементы 17-21. Если маркер принят на выходе элемента 20э формируется единичный сигнал, который устанавливает триггер 23 в 1 (фиг. 3). По

0

5

0

5

0

5

0

5

0

5

этому сигналу и сигналу ЗП1 - прямой выход элемента 27 (фиг. 4), счетчики 32-34 адреса 1 памяти переводятся в рабочее состояние. На выходе счетчиков 32-34 к моменту записи в блок 1 памяти находится нулевой адрес . Наличие синхросигнала 11, информационного сигнала 6 и сигнала записи (выход элемента 26) разрешает работу накопителя 31 (фиг. 5). По окончании записи блока информации в блоке 1 формируется сигнал готовности (выход элемента 41). При формировании сигнала готовности по всем каналам элемент И 2 выдает сигнал ГОТ 1, который устанавливает триггер 23 в нулевое состояние. Запись в блок 1 памяти окончена. Одновременно сигнал ГОТ 1 подается на блок

3задания режима (фиг, 4). По этому сигналу формируется сигнал ЗП 2 (инверсный выход триггера 28). Начинается запись следующего блока информации, но в блок 4 памяти второй группы.

Режим считывания определяется сигналам СЧ 1 (инверсный выход триггера 28) для блока 1 памяти, СЧ 2 (прямой выход триггера 28) для блока

4памяти. В начальный момент по сигналу, поступающему с выхода элемента 24, счетчики 32-34 адреса, устанавливаются в рабочее состояние. По сигналу на входе 12 осуществляется перебор адресов в счетчиках 32-34. Блок 10 переключения режимов по сигналу СЧ 1 формирует сигнал чтения (выход элемента 26), поступающий

на накопитель 31 блока 1 памяти. Данные одновременно считываются во внешнее устройство с информационных выходов коммутаторов 7 при наличии сигнала СЧ 1. Сигналы с входа 12 и чтения (выход элемента 26) поступают на все блоки 1 памяти первой группы одновременно. По окончании считывания всей информации формируется сигнал ГОТ 1 (выход -элемента И 2), по которому на выходе блока 3 формируется сигнал СЧ 1 (прямой выход триггера 28). Считывание из бло- .ка 4 памяти второй группы происходит аналогично. Сигнал ГОТ 2 формируется на выходе элемента И 9.

После первого цикла записи считывание и запись происходят одновременно, но в разных блоках памяти в

1478257

противофазе. Этим обеспечиваются не- прирывная запись и считывание информации.

Формула изобретения

Многоканальное буферное запоминающее устройство, содержащее в каждом канале блок памяти первой группы, первый элемент И и блок задания режима, первый вход которого подключен к выходу первого элемента И, входы которого подключены к выходам

10

первой и второй групп, входы задания режимов и синхровходы которых подключены к соответствующим выходам соответствующего блока переключения режимов, вход запуска которого подключен к выходу соответствующего блока выделения маркера, синхровход которого подключен к соответствующему входу блока переключения режимов и является соответствующим синхровходом устройства, выходы блока задания режима подключены к входам задания режима блоков переключения режимов и

готовности блоков памяти первой труп- 15 к управляющим входам коммутаторов, пы, информационные входы которых яв- первый и второй информационные входы

коммутатора каждого из каналов подключены к информационным выходам соляются соответствующими информационными входами устройства, вход начальной установки блока задания режима является входом начальной установки устройства, отличающееся тем. что, с целью расширения области

20

ответствующих блоков памяти первой и второй групп, выходы готовности блоков памяти второй группы подключены к входам второго элемента И, выход которого подключен к второму входу блока задания режима, вход наприменения устройства за счет асинхронного приема и выдачи массивов данных по каналам, оно содержит в каждом 25 чальной установки которого подключен канале блок памяти второй группы, к входам начальной установки блоков

переключения режимов, входы чтения которых объединены и являются входом чтения устройства, выход коммутато- 3Q ра каждого из каналов является соответствующим информационным выходом устройства.

коммутатор, блок переключения режимов, блок выделения маркера и второй элемент И, причем информационный вход блока выделения маркера каждого из каналов подключен к информационным входам соответствущих блоков памяти

первой и второй групп, входы задания режимов и синхровходы которых подключены к соответствующим выходам соответствующего блока переключения режимов, вход запуска которого подключен к выходу соответствующего блока выделения маркера, синхровход которого подключен к соответствующему входу блока переключения режимов и является соответствующим синхровходом устройства, выходы блока задания режима подключены к входам задания режима блоков переключения режимов и

ответствующих блоков памяти первой и второй групп, выходы готовности блоков памяти второй группы подключены к входам второго элемента И, выход которого подключен к второму входу блока задания режима, вход начальной установки которого подключен к входам начальной установки блоков

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТ ПОВРЕЖДЕНИЯ НАПОРНОГО ТРУБОПРОВОДА | 1992 |

|

RU2046251C1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля аналогового сигнала | 1990 |

|

SU1797097A1 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| Адаптивное устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532938A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| УСТРОЙСТВО БУФЕРИЗАЦИИ И СИНХРОНИЗАЦИИ ДЛЯ ОБРАБОТКИ НЕПРЕРЫВНОГО СИГНАЛА | 1990 |

|

SU1812885A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

Изобретение относится к области вычислительной техники, а именно к буферным запоминающим устройствам, и может быть использовано для промежуточного хранения информации при передаче многоканальной информации. Цель изобретения - расширение области применения устройства за счет его работы с изменяющейся задержкой асинхронного приема и выдачи данных по каналам. Устройство содержит блоки памяти первой и второй групп, два элемента И, блок задания режима, коммутаторы, блоки переключения режимов, блоки выделения маркера. Буферное запоминающее устройство позволяет принимать, обрабатывать и с высокой скоростью выдавать информацию, сгруппированную в блоки и поступающую асинхронно по нескольким параллельным каналам, например, с нескольких дорожек магнитофона. Запись данных осуществляется в блок памяти первой группы до его заполнения. Затем осуществляется переключение записи на блок памяти второй группы с возможностью одновременного считывания данных из блока памяти первой группы и т.д. 5 ил.

Фиг.1

сриг.3

Редактор А,Мотыль

Составитель С.Шустенко

Техред Л.Олийнык Корректор М.Демчик

Ц)игЛ

Фиг. 5

| Устройство для ввода информации в цифровую вычислительную машину с внешнего носителя | 1977 |

|

SU638952A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шигин А.Г., Дерюгин А.А | |||

| Цифровые вычислительные машины | |||

| Память ЦВМ | |||

| - М.: Энергия, 1976 с | |||

| Поливное приспособление для паровозов | 1922 |

|

SU390A1 |

Авторы

Даты

1989-05-07—Публикация

1987-06-16—Подача