1

Изобретение относится к вычислительной технике и может быть использовано для контроля биполярных больших интегральных микросхем постоянных запоминающих устройств, программируемых избирательным разрушением плавких перемычек (БИС ППЗУ).

Цель изобретения - повышение достоверности контроля.

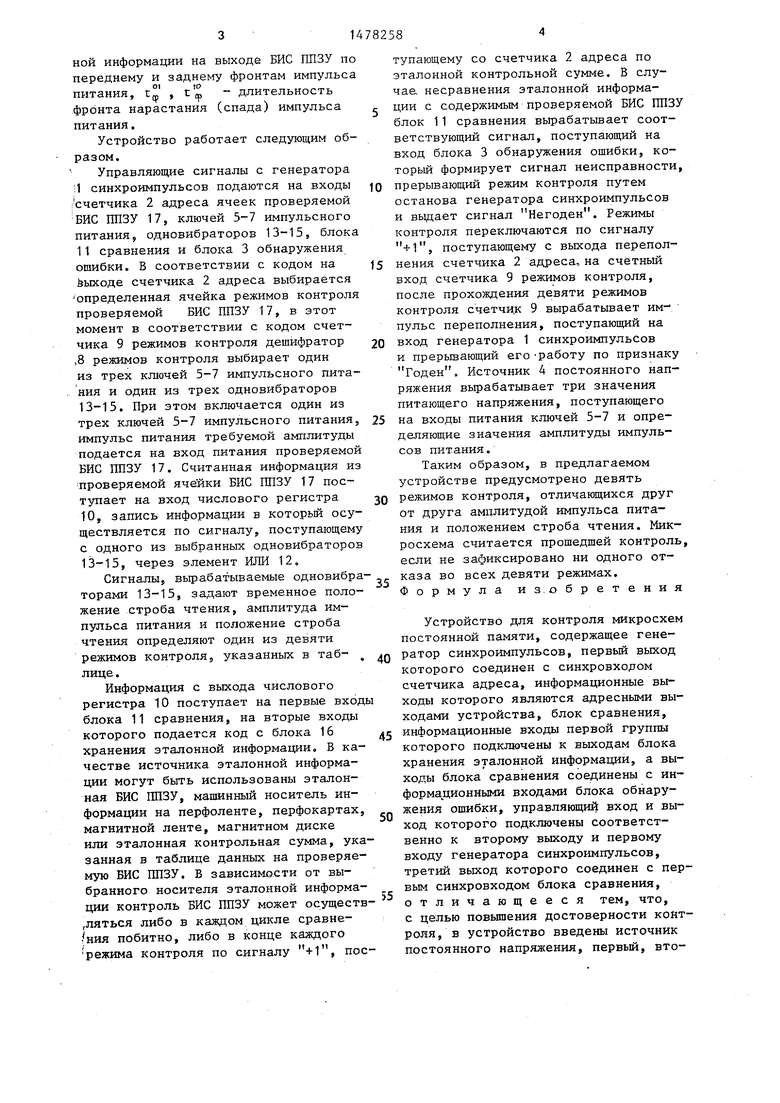

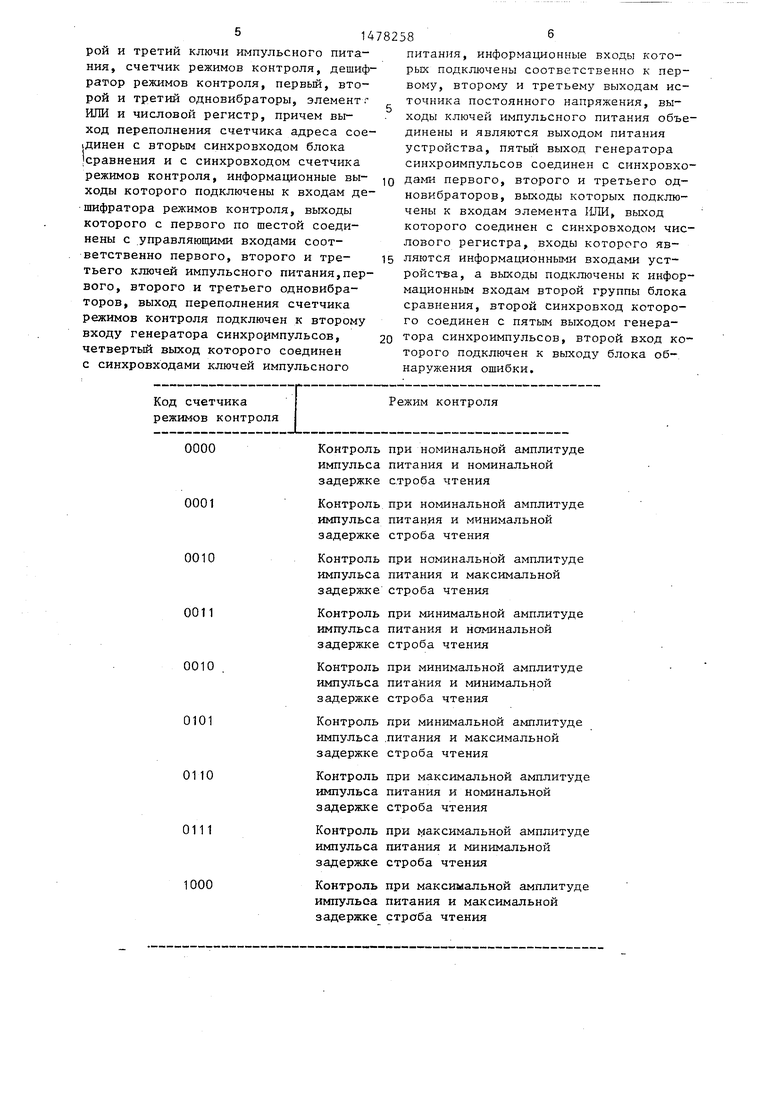

На фиг. 1 представлена схема устройства для контроля микросхем постоянной памяти, на фиг. 2 - временная диаграмма контролируемой микросхемы памяти.

Устройство (фиг. 1) содержит генератор 1 синхроимпульсов, счетчик 2 адреса, блок 3 обнаружения ошибки, источник 4 постоянного напряжения,

ключи 5-7 импульсного питания,дешифратор 8 режимов контроля, счетчик 9 режимов контроля, числовой регистр 10, блок 11 сравнения, элемент ИЛИ 12, одновибраторы 13-15, блок 16 хранения эталонной информации. На .фиг. 1 также показана контролируемая микросхема памяти (БИС ППЗУ) 17.

На фиг. 2 приняты следуюшие обозначения: Ucc- напряжение питания, подаваемое на БИС ППЗУ, UW(,H, UHOM, U/иакс - значения амплитуды импульса питания, U0 - напряжение на выходе

БИС ППЗУ в режиме считывания, U. - импульс строба чтения, t, tHOM , сл«акс временные положения строба чтения при контроле БИС ППЗУ, сии s t ни - время сохранения неопределенЈ

ю

сд оо

ной информации на выходе БИС ППЗУ по переднему и заднему фронтам импульса питания, t° , t m - длительность

. Ч

фронта нарастания (спада) импульса питания.

Устройство работает следующим образом.

Управляющие сигналы с генератора

Iсинхроимпульсов подаются на входы счетчика 2 адреса ячеек проверяемой БИС ППЗУ 17, ключей 5-7 импульсного питания, одновибраторов 13-15, блока

I1сравнения и блока 3 обнаружения ошибки. В соответствии с кодом на йыходе счетчика 2 адреса выбирается

определенная ячейка режимов контроля проверяемой БИС ППЗУ 17, в этот момент в соответствии с кодом счетчика 9 режимов контроля дешифратор ,8 режимов контроля выбирает один из трех ключей 5-7 импульсного питания и один из трех одновибраторов 13-15, При этом включается один из трех ключей 5-7 импульсного питания, импульс питания требуемой амплитуды подается на вход питания проверяемой БИС ППЗУ 17. Считанная информация из проверяемой ячейки БИС ППЗУ 17 поступает на вход числового регистра 10, запись информации в который осуществляется по сигналу, поступающему с одного из выбранных одновибраторов 13-15, через элемент ИЛИ 12.

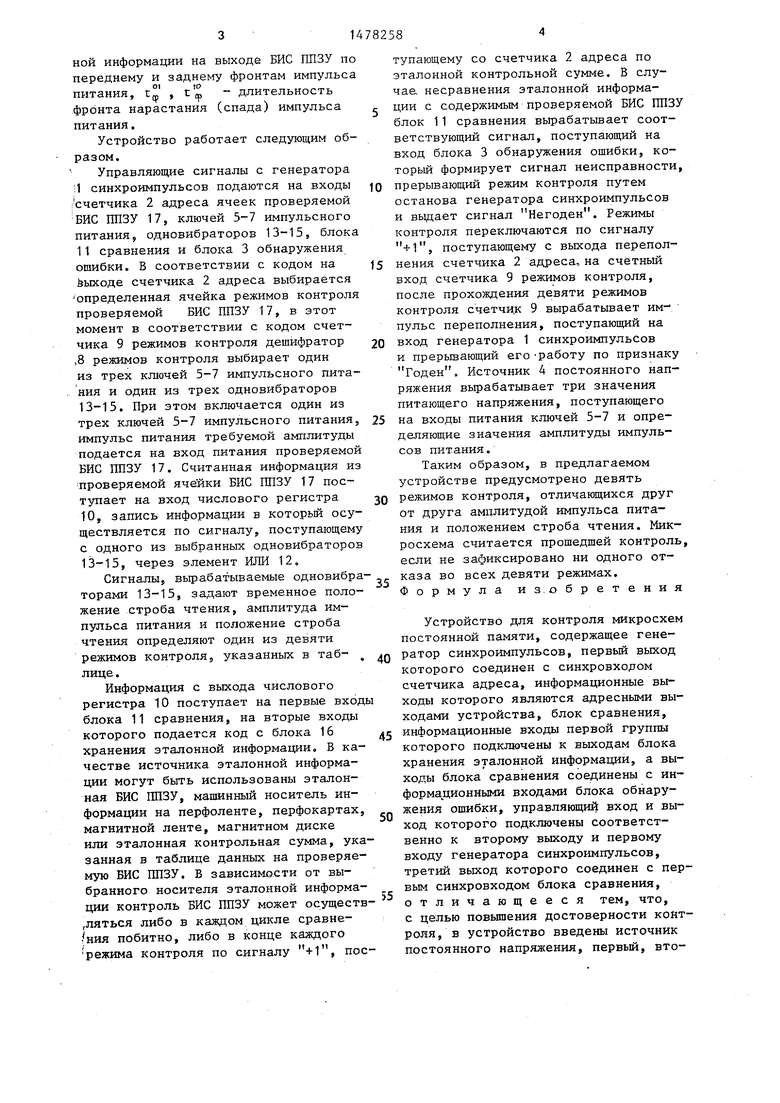

Сигналы вырабатываемые одновибра торами 13-15, задают временное положение строба чтения, амплитуда импульса питания и положение строба чтения определяют один из девяти режимов контроля9 указанных в таблице.

Информация с выхода числового регистра 10 поступает на первые вход блока 11 сравнения, на вторые входы которого подается код с блока 16 хранения эталонной информации. В качестве источника эталонной информации могут быть использованы эталонная ВИС ППЗУ, машинный носитель информации на перфоленте, перфокартах, магнитной ленте, магнитном диске или эталонная контрольная сумма, указанная в таблице данных на проверяемую БИС ППЗУ. В зависимости от выбранного носителя эталонной информации контроль БИС ППЗУ может осуществ ,ляться либо в каждом цикле сравне- ния побитно, либо в конце каждого режима контроля по сигналу +1, пос0

5

0

5

0

5

0

5

0

5

тупающему со счетчика 2 адреса по эталонной контрольной сумме. В слу- чаа несравнения эталонной информации с содержимым проверяемой БИС ППЗУ блок 11 сравнения вырабатывает соответствующий сигнал, поступающий на вход блока 3 обнаружения ошибки, который формирует сигнал неисправности, прерывающий режим контроля путем останова генератора синхроимпульсов и выдает сигнал Негоден. Режимы контроля переключаются по сигналу -Н, поступающему с выхода переполнения счетчика 2 адреса, на счетный вход счетчика 9 режимов контроля, после прохождения девяти режимов контроля счетчик 9 вырабатывает импульс переполнения, поступающий на вход генератора 1 синхроимпульсов и прерывающий его -работу по признаку Годен. Источник 4 постоянного напряжения вырабатывает три значения питающего напряжения, поступающего на входы питания ключей 5-7 и определяющие значения амплитуды импульсов питания,

Таким образом, в предлагаемом устройстве предусмотрено девять режимов контроля, отличающихся друг от друга амплитудой импульса питания и положением строба чтения. Микросхема считается прошедшей контроль, если не зафиксировано ни одного отказа во всех девяти режимах. Формула изобретения

Устройство для контроля микросхем постоянной памяти, содержащее генератор синхроимпульсов, первый выход которого соединен с синхровходом счетчика адреса, информационные выходы которого являются адресными выходами устройства, блок сравнения, информационные входы первой группы которого подключены к выходам блока хранения эталонной информации, а выходы блока сравнения соединены с информационными входами блока обнаружения ошибки, управляющий вход и выход которого подключены соответственно к второму выходу и первому входу генератора синхроимпульсов, третий выход которого соединен с первым синхровходом блока сравнения, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены источник постоянного напряжения, первый, второй и третий ключи импульсного питания, счетчик режимов контроля, дешифратор режимов контроля, первый, второй и третий одновибраторы, элемент г ИЛИ и числовой регистр, причем выход переполнения счетчика адреса соединен с вторым синхровходом блока сравнения и с синхровходом счетчика режимов контроля, информационные выходы которого подключены к входам дешифратора режимов контроля, выходы которого с первого по шестой соединены с управляющими входами соответственно первого, второго и третьего ключей импульсного питания,первого, второго и третьего одновибра- торов, выход переполнения счетчика режимов контроля подключен к второму входу генератора синхроимпульсов, четвертый выход которого соединен с синхровходами ключей импульсного

питания, информационные входы которых подключены соответственно к первому, второму и третьему выходам источника постоянного напряжения, выходы ключей импульсного питания объединены и являются выходом питания устройства, пятый выход генератора синхроимпульсов соединен с синхровходами первого, второго и третьего од- новибраторов, выходы которых подключены к входам элемента ИЛИ, выход которого соединен с синхровходом числового регистра, входы которого яв5 ляются информационными входами устройства, а выходы подключены к информационным входам второй группы блока сравнения, второй синхровход которого соединен с пятым выходом генера0 тора синхроимпульсов, второй вход которого подключен к выходу блока обнаружения ошибки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи информации в полупроводниковые блоки постоянной памяти | 1987 |

|

SU1444882A2 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1564693A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1325571A1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1986 |

|

SU1376121A2 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для контроля блоков постоянной памяти | 1991 |

|

SU1830548A1 |

| Устройство для контроля оперативной памяти тестом Марш с двоично-нарастающим адресным шагом | 1986 |

|

SU1532978A1 |

| Устройство для управления памятью | 1984 |

|

SU1243030A1 |

| СИСТЕМА АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ | 1991 |

|

RU2006896C1 |

| Устройство для контроля цифровых интегральных микросхем | 1985 |

|

SU1265663A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля биполярных больших интегральных микросхем постоянных запоминающих устройств, программируемых избирательным разрушением плавких перемычек. Целью изобретения является повышение достоверности контроля. Устройство содержит генератор синхроимпульсов, счетчик адреса, блок сравнения, блок обнаружения ошибки, числовой регистр, источник постоянного напряжения, ключи импульсного питания, одновибраторы, элемент ИЛИ, блок хранения эталонной информации. Цель изобретения достигается проверкой микросхем постоянной памяти в режиме импульсного питания с номинальным и предельно допустимыми максимальным и минимальным значениями амплитуды питания при положениях строба считывания на границах и в зоне устойчивой работы для каждого значения напряжения питания. 2 ил.

Контроль при номинальной амплитуде импульса питания и номинальной задержке строба чтения

Контроль при номинальной амплитуде импульса питания и минимальной задержке строба чтения

Контроль при номинальной амплитуде импульса питания и максимальной задержке строба чтения

Контроль при минимальной амплитуде импульса питания и номинальной задержке строба чтения

Контроль при минимальной амплитуде импульса питания и минимальной задержке строба чтения

Контроль при минимальной амплитуде импульса питания и максимальной задержке строба чтения

Контроль при максимальной амплитуде импульса питания и номинальной задержке строба чтения

Контроль при максимальной амплитуде импульса питания и минимальной задержке строба чтения

Контроль при максимальной амплитуде импульса питания и максимальной задержке строба чтения

FJrs;;6 S 1 w

J-fKl,В

ijs

I s

ii ,,ч яf

; iffife

:4&#рл &л

A«f

г-т 4i

(7 0,1 t,f

UЈ

I s .4 ii r «

,

| Скрипка | 1923 |

|

SU556A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля постоянной памяти | 1979 |

|

SU769640A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-05-07—Публикация

1987-09-21—Подача