1

Изобретение относится к области запоминающих устройств.

Известны устройства для контроля постоянной памяти 1, 2.

Одно из известных устройств содержит 5 считывающий блок, блок управления, регистр адреса, сумматор, счетчик и блок сравнения 1.

Иедостатком этого устройства является отсутствие индикации слов и разрядов про- ю веряемой постоянной памяти, что увеличивает время и снижает точность и достоверность контроля.

Из известных устройств наиболее близким техническим решением к изобретению i5 является устройство для контроля постоянной памяти, содержащее блок управления, схему сравнения, причем первые вход и выход блока управления подключены соответственно к первым выходу и входу схемы 20 сравнения 2.

Недостатками этого устройства является отсутствие индикации слов и разрядов проверяемой постоянной памяти, что вызывает 25 необходимость ручной проверки ошибок, и применение в проверяемой постоянной памяти дополнительных элементов для получения контрольной суммы и запрещения прохождения сигнала при ошибке, что 30

уменьшает быстродействие устройства, снижает точность и достоверность контроля.

Целью изобретения является повышение быстродействия устройства и достоверности контроля.

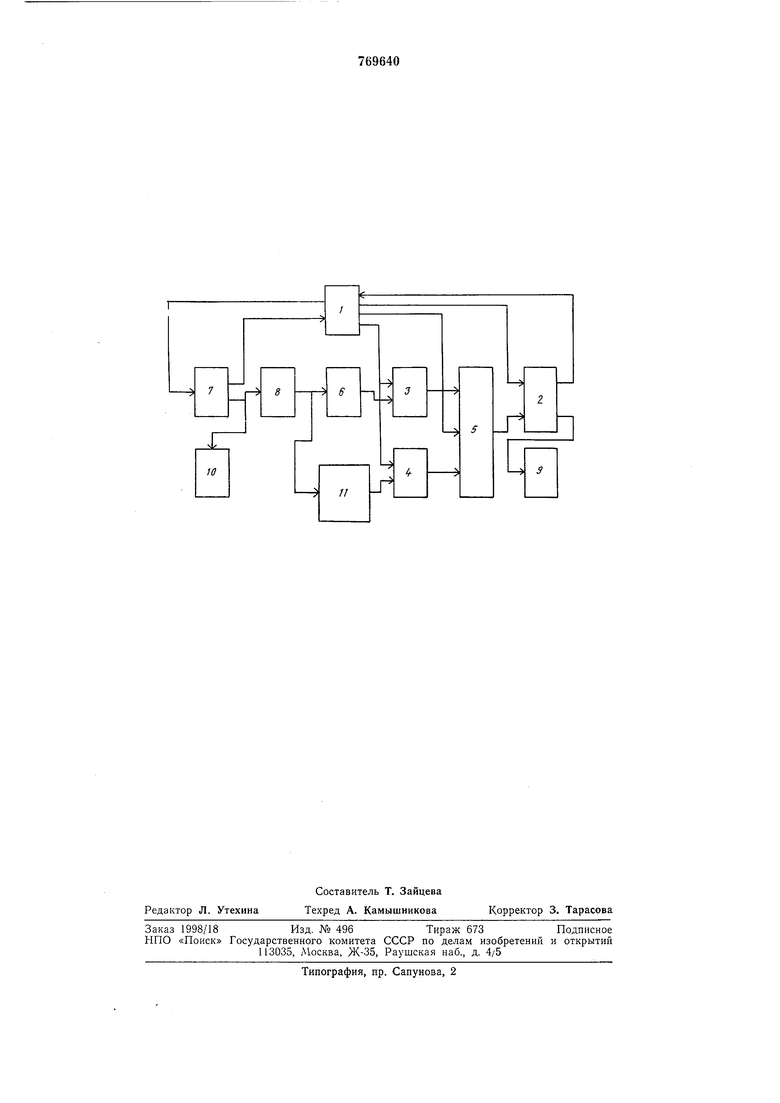

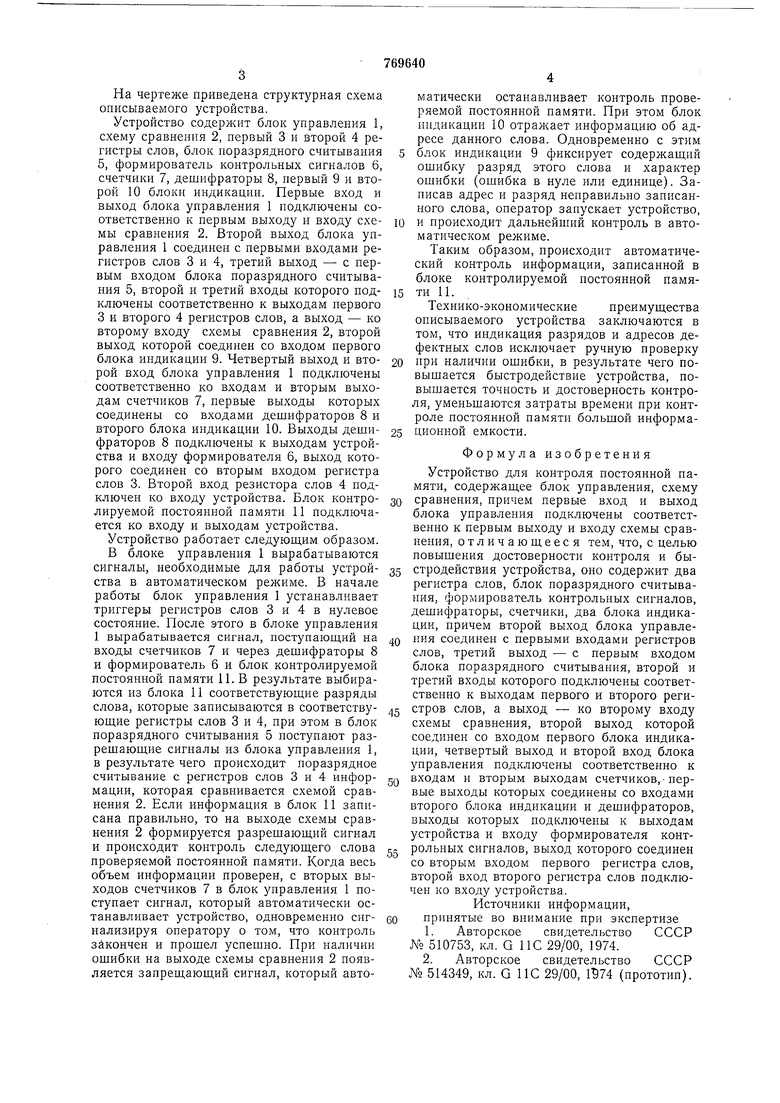

Поставленная цель достигается тем, что устройство содержит два регистра слов, блок поразрядного считывания, формирователь контрольных сигналов, дешифраторы, счетчики, два блока индикации, причем второй выход блока управления соединен с первыми входами регистров слов, третий выход - с первым входом блока поразрядного считывания, второй и третий входы которого подключены соответственно к выходам первого и второго регистров слов, а выход - ко второму входу схемы сравнения, второй выход которой соединен со входом первого блока индикации, четвертый выход и второй вход блока управления подключены соответственно к входам и вторым выходам счетчиков, первые выходы которых соединены со входами второго блока индикации и дешифраторов, выходы которых подключены к выходам устройства и входу формирователя контрольных сигналов, выход которого соединен со вторым входом первого регистра слов, второй вход второго регистра слов подключен ко входу устройства. На чертеже приведена структурная схема описываемого устройства. Устройство содержит блок управления 1, схему сравнения 2, первый 3 и второй 4 регистры слов, блок поразрядного считывания 5, формирователь контрольных сигналов 6, счетчики 7, дешифраторы 8, первый 9 и второй 10 блоки индикации. Первые вход и выход блока управления 1 подключены соответственно к первым выходу и входу схемы сравнения 2. Второй выход блока управления 1 соединен с первыми входами регистров слов 3 и 4, третий выход - с первым входом блока поразрядного считывания 5, второй и третий входы которого подключены соответственно к выходам нервого 3 и второго 4 регистров слов, а выход - ко второму входу схемы сравнения 2, второй выход которой соединен со входом первого блока индикации 9. Четвертый выход и второй вход блока управления 1 подключены соответственно ко входам и вторым выходам счетчиков 7, первые выходы которых соединены со входами дешифраторов 8 и второго блока индикации 10. Выходы дешифраторов 8 подключены к выходам устройства и входу формирователя 6, выход которого соединен со вторым входом регистра слов 3. Второй вход резистора слов 4 подключен ко входу устройства. Блок контролируемой ностоянной памяти 11 подключается ко входу и выходам устройства. Устройство работает следующим образом. В блоке управления 1 вырабатываются сигналы, необходимые для работы устройства в автоматическом режиме. В начале работы блок управления 1 устанавливает триггеры регистров слов 3 и 4 в нулевое состояние. После этого в блоке управления 1 вырабатывается сигнал, поступающий на входы счетчиков 7 и через дешифраторы 8 и формирователь 6 и блок контролируемой постоянной памяти 11. В результате выбираются из блока 11 соответствующие разряды слова, которые записываются в соответствующие регистры слов 3 и 4, при этом в блок поразрядного считывания 5 поступают разрешающие сигналы нз блока управления 1, в результате чего происходит поразрядиое считывание с регистров слов 3 и 4 информации, которая сравнивается схемой сравнения 2. Если информация в блок 11 записана правильно, то на выходе схемы сравнения 2 формируется разрешающий сигнал и происходит контроль следующего слова проверяемой постоянной памяти. Когда весь объем информации нроверен, с вторых выходов счетчиков 7 в блок управления 1 поступает сигнал, который автоматически останавливает устройство, одновременно сигнализируя оператору о том, что контроль закончен и прошел успешно. При наличии ошибки на выходе схемы сравнения 2 появляется запрещающий сигиал, который автоматически останавливает контроль проверяемой постоянной памяти. При этом блок индикации 10 отражает информацию об адресе данного слова. Одновременно с этим блок индикации 9 фиксирует содержащий ошибку разряд этого слова и характер ошибки (ошибка в нуле или единице). Записав адрес и разряд неправильно записанного слова, оператор запускает устройство, и происходит дальнейший контроль в автоматическом режиме. Таким образом, происходит автоматический контроль информации, записанной в блоке контролируемой постоянной иамятн 11. Техиико-экономические преимущества описываемого устройства заключаются в том, что индикация разрядов и адресов дефектных слов исключает ручную проверку при наличии ошибки, в результате чего повышается быстродействие устройства, повышается точность и достоверность контроля, уменьшаются затраты времени при контроле постоянной памяти большой информационной емкости. Формула изобретения Устройство для контроля постоянной памяти, содержащее блок управления, схему сравнения, причем первые вход и выход блока управления подключены соответственно к первым выходу и входу схемы сравнения, отличающееся тем, что, с целью повышения достоверности контроля и быстродействия устройства, оно содержит два регистра слов, блок поразрядного считывания, формирователь контрольных сигналов, дешифраторы, счетчики, два блока индикации, причем второй выход блока управления соединен с первыми входами регистров слов, третий выход - с первым входом блока поразрядного считывания, второй и третий входы которого подключены соответственно к выходам первого и второго регистров слов, а выход - ко второму входу схемы сравнения, второй выход которой соединен со входом первого блока индикации, четвертый выход и второй вход блока управления подключены соответственно к входам и вторым выходам счетчиков, первые выходы которых соединены со входами второго блока индикации и дешифраторов, выходы которых подключены к выходам устройства и входу формирователя контрольных сигналов, выход которого соединен со вторым входом первого регистра слов, второй вход второго регистра слов подключен ко входу устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 510753, кл. G НС 29/00, 1974. 2.Авторское свидетельство СССР № 514349, кл. G ПС 29/00, (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для записи информации в запоминающее устройство | 1980 |

|

SU951399A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Запоминающее устройство с обнаружением отказавших блоков | 1980 |

|

SU903974A1 |

Авторы

Даты

1980-10-07—Публикация

1979-01-10—Подача