ел

со

ND

СО

sj

00

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано для функционального контроля как отдельных больших интегральных микросхем оперативных запоминающих устройств (БИС ОЗУ), так и массивов ОЗУ, построенных на их основе.

Цель изобретения - упрощение устройства.

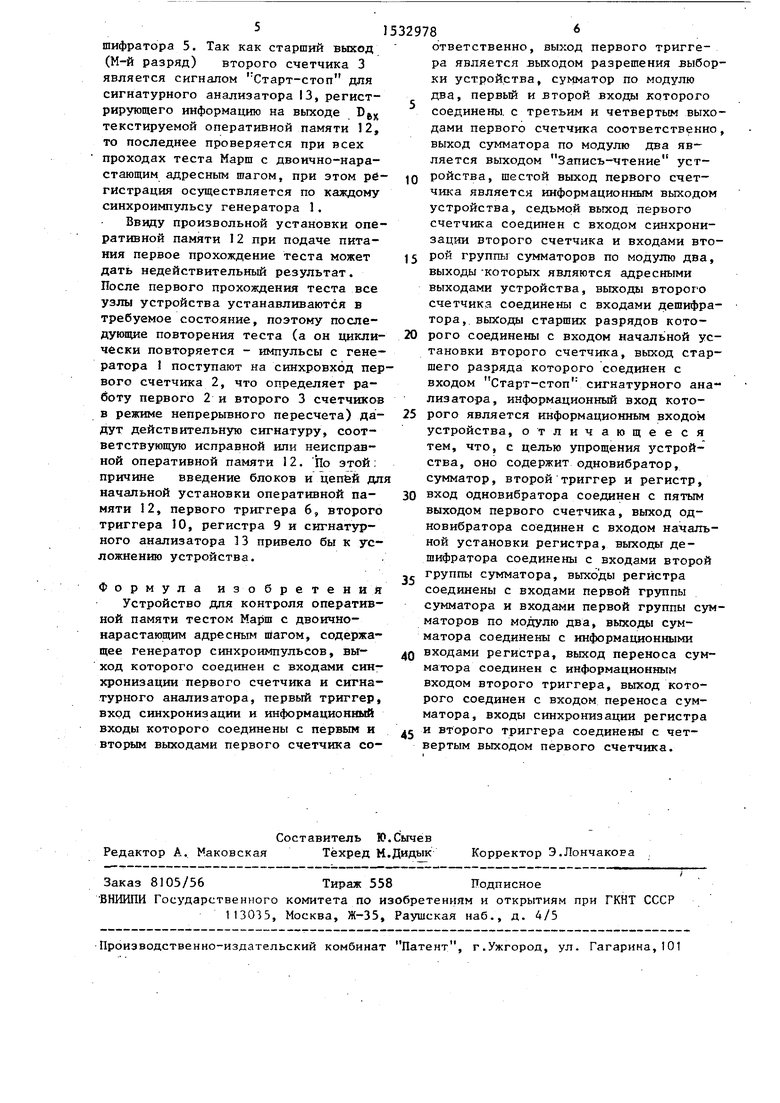

На чертеже представлена схема предлагаемого устройства.

Устройство содержит генетатор 1 синхроимпульсов, первый счетчик 2, в/горой счетчик 3, одновибратор 4, Дешифратор 5, первый триггер 6, сумматор 7, сумматор 8 по модулю два, регисор 9, второй триггер 10, группу сумматоров 11 по модулю два, оперативную память 12, сигнатурный ана- .изатор 13.

Устройство работает следующим образом.

Импульсы с генератора 1 -синхро- .мпульсов обеспечивают работу первого Счетчика 2 в режиме непрерывного пересчета. Смена информации на адресных входах оперативной памяти происходит io заднему фронту сигналов с четвер- toro выхода (3-й разряд) первого счетtmKa 2 (определяется сменой инфор- мации на выходах Qu... Оп регистра J3) . Таким образом, обращение к каждому адресу составляет 16 тактов синхросигнала генератора 1 синхроимпульсов . В течение первых четырех тактов по каждому адресу осуществляется операция Чтение фоновой информации, в течение следующих восьми тактов последовательно осуществляются две операции записи, инверсной по отношению к фоновой информации по данному адресу, в последних четырех тактах осуществляется повторная операция Чтение по данному адресу . Требуемая последовательность выполнения операций Чтение и Запись обеспечивается сумматрором 8 по модулю два.Внутрь каждой четырехтактной операции Чтение или Запись вложен двухтактный сигнал Разрешение выборки (обеспечивается первым гером 6), который принимает активный уровень при неизменных других сигналах, поданных на блок оперативной памяти 12. В начале каждого прохода адресов по заднему фронту сиг

5

0

5

0

5

0

45

50

5

нала с пятого ((п+3)-й разряд) выхода первого счетчика 2 одновибрато- ром 4 формируется короткий импульс длительностью менее одного периода синхросигнала, сбрасывающий регистр 9. После выполнения основной процедуры теста, состоящей из четырех проходов адресов, второй счетчик 3 ин- крементируется. Дешифратор 5, управляемый выходами второго счетчика 3, формирует текущее двоично-нарастающее приращение адресного шага основной процедуры. Сумматор 7 на основании текущего адреса ячейки памяти, хранящегося в регистре 9, заданного приращения адресного шага, определяемого дешифратором 5, и значения переноса, записываемого на второй триггер 10 по переднему фронту сигнала с четвертого выхода (3-й разряд) первого счетчика 2, формирует следующий адрес оперативной памяти 12.

Фиксация вторым триггером 10 возникающего на выходесумматора 7 переноса по переднему фронту сигнала с четвертого выхода (3-й разряд) первого счетчика 2, т.е. еще в процессе формирования следующего адреса, обеспечивает его учет при данном формировании. Запись нового адреса в регистр 9 происходит по заднему фронту сигнала с четвертого выхода (3-й разряд) первого счетчика 2, На выходах регистр 9 формируется последователь- ; ность, соответствующая двоично-нарастающему адресному шагу.

После прохода всех адресов одновиб- ратором 6, управляемым пятым выходом ((п+3)-й разряд) первого счетчика 2 формируется короткий импульс, осуществляющий сброс регистра 9 в начальное состояние, необходимое для начала формирования следующей последовательности. Группа сумматоров JJ по модулю два, управляемая шестым выходом ((п+5)-й разряд) первого счетчика 2, обеспечивает обратный проход адресов. Прохождение теста с взаимно инверсной информацией обеспечивается подачей на вход данных Eg оперативной памяти 12 сигнала с шестого выхода ((п+4)-й разряд) первого счетчика 2.

После прохождения основной тестовой процедуры с максимально возможным шагом, прохождение теста начинается вновь, что обеспечивается сбросом счетчика 3 сигналом с выхода дешифратора 5. Так как старший выход (М-й разряд) второго счетчика 3 является сигналом |:Старт-стоп для сигнатурного анализатора 13, регистрирующего информацию на выходе D6X текстируемой оперативной памяти 12, то последнее проверяется при всех проходах теста Марш с двоично-нарастающим адресным шагом, при этом регистрация осуществляется по каждому синхроимпульсу генератора 1.

Ввиду произвольной установки оперативной памяти 12 при подаче питания первое прохождение теста может дать недействительный результат. После первого прохождения теста все узлы устройства устанавливаются в требуемое состояние, поэтому последующие повторения теста (а он циклически повторяется - импульсы с генератора 1 поступают на синхровход первого счетчика 2, что определяет работу первого 2 и второго 3 счетчиков в режиме непрерывного пересчета) дадут действительную сигнатуру, соответствующую исправной или неисправной оперативной памяти 12. По этой причине введение блоков и цепей для начальной установки оперативной памяти 12, первого триггера 6, второго триггера 10, регистра 9 и сигнатурного анализатора 13 привело бы к усложнению устройства.

Формула изобретения Устройство для контроля оперативной памяти тестом Марш с двоично- нарастающим адресным шагом, содержащее генератор синхроимпульсов, выход которого соединен с входами синхронизации первого счетчика и сигнатурного анализатора, первый триггер, вход синхронизации и информационный входы которого соединены с первым и вторым выходами первого счетчика со-

5329786

ответственно, выход первого триггера является выходом разрешения выборки устройства, сумматор по модулю два, первый и второй входы которого соединены с третьим и четвертым выходами первого счетчика соответственно, выход сумматора по модулю два является выходом Запись-чтение устJQ ройства, шестой выход первого счетчика является информационным выходом устройства, седьмой выход первого счетчика соединен с входом синхронизации второго счетчика и входами втоJ5 РОЙ группы сумматоров по модулю два, выходы -которых являются адресными выходами устройства, выходы второго счетчика соединены с входами дешифратора, выходы старших разрядов кото20 рого соединены с входом начальной установки второго счетчика, выход стар

шего разряда которого соединен с входом Старт-стоп|: сигнатурного анализатора, информационный вход которого является информационным входом устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит одновибратор, сумматор, второй триггер и регистр, вход одновибратора соединен с пятым выходом первого счетчика, выход одновибратора соединен с входом начальной установки регистра, выходы дешифратора соединены с входами второй группы сумматора, выходы регистра соединены с входами первой группы сумматора и входами первой группы сумматоров по модулю два, выходы сумматора соединены с информационными входами регистра, выход переноса сумматора соединен с информационным входом второго триггера, выход которого соединен с входом переноса сумматора, входы синхронизации регистра

и второго триггера соединены с четвертым выходом первого счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705874A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Устройство для контроля оперативной памяти | 1983 |

|

SU1140179A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Параллельный сигнатурный анализатор | 1984 |

|

SU1182523A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1564693A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478220A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1413676A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

Изобретение относится к вычислительной технике и может быть использовано для функционального контроля БИС ОЗУ, а также блоков ОЗУ. Цель изобретения - упрощение устройства. Устройство содержит генератор 1 синхроимпульсов, первый 2 и второй 3 счетчики, одновибратор 4, дешифратор 5, первый триггер 6, сумматор 7, сумматор 8 по модулю два, регистр 9, второй триггер 10, группу 11 сумматоров по модулю два, блок 12 оперативной памяти, сигнатурный анализатор 13. 1 ил.

| Электронная промышленность, 1977, № 2, с | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Микроэлектроника, 1985, т | |||

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Способ обработки грубых шерстей на различных аппаратах для мериносовой шерсти | 1920 |

|

SU113A1 |

Авторы

Даты

1989-12-30—Публикация

1986-12-30—Подача