Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных системах обработки информации.

Целью изобретения является повышение достоверности контроля устройства.

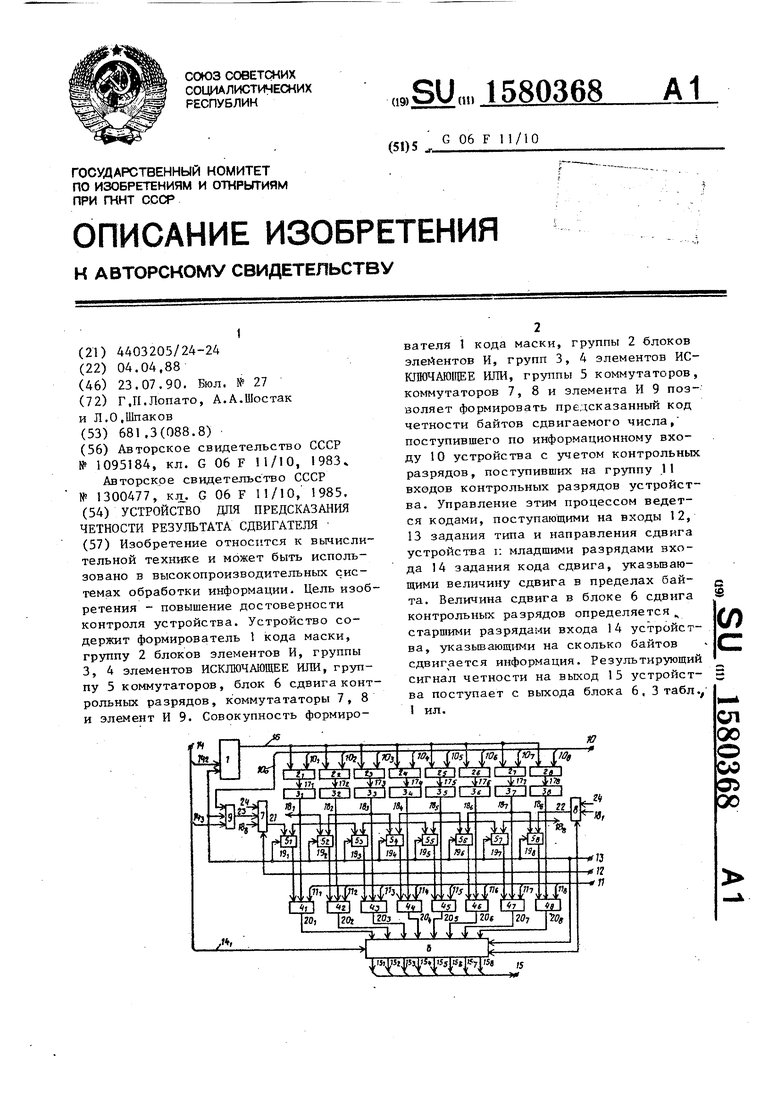

На чертеже приведена функциональная схема устройства,

Устройство содержит формирователь 1 кода маски, группу 2 блоков элементов И, первую 3 и вторую 4 группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу 5 коммутаторов, блок 6 сдвига контроль ных разрядов, коммутаторы 7 и 8, элемент И 9, информационный вход 10 устройства, группу 11 входов контрольных разрядов устройства, входы 12-14 задания типа, направдения и кода сдви- га устройства соответственно, выход 15 контрольных разрядов устройства, выход 16 формирователя кода маски, выходы 17 блоков элементов И группы 2, выходы 18 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы 3, выходы 19 коммутаторов группы 5, выходы 20 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы 4, выходы 21 и 22 первого 7 и второго 8 коммутаторов, выходы 23 элемента И 9, шину 24 нулевого потенциала устройства.

Работа устройства рассматривается для случая 64-разрядного кода (8 байтов) .

Совокупность формирователя 1 кода маски, группы 2 блоков элементов И, первьй 3 и второй 4 групп элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группы 5 коммутаторов, первого 7 и второго 8 коммутато- ров и элементов И 9 предназначена для формирования предсказанных четностей байтов результата сдвигателя при выполнении сдвигов под управлением младших трех разрядов кода сдвига,

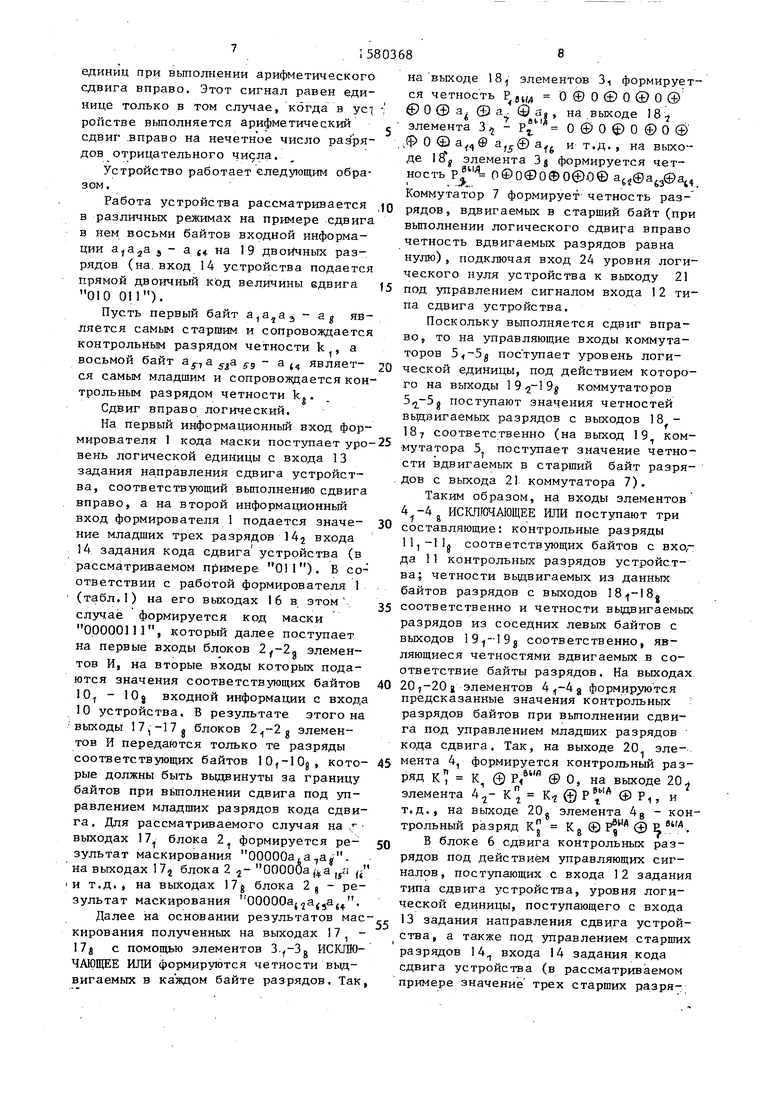

Формирователь 1 кода маски пред- назначен для формирования восьмиразрядного двоичного кода маски, позволяющей выделить в каждом байте входной информации устройства те раз- ряды, которые при выполнении сдвига под управлением младших трех разрядов кода сдвига, поступающего на вход 14 устройства, пересекают границу байта т.е. переходят в соседний байт. В табл.1 детально описано функционирование формирователя, 1 кода маски, на управляющий вход которого поступает управляющий сигнал с входа 13

.

5 0 5 о

5

о 5

Q

5

направле ия сдвига устройства, а на информационные входы - младшие три разряда 142 входа 14 сдвига устройства. Для определенности принято следующее: при выполнении сдвига вправо на входе 13 направления сдвига устанавливается уровень логической единицы, а при выполнении сдвига влево - уровень логического нуля, независимо от направления сдвига, код сдвига на вход 14 устройства поступает в прямом коде.

Формигователь 1 кода маски можно выполнить различными способами: на ПИЗУ 500РЕ 149 (управляющий и информационные входы формирователя 1 в этом случае являются адресными входами ППЗУ) ; на элементах И, ИЛИ, НЕ ,выполнив синтез по таблице истинности работы формирователя 1; на восьмивходо- вых мультиплексорах 500 ИД 164 (в -; этом случае удобнее воспользоваться табл.2, в которой представлено функционирование формирователя 1, учитывающее реализацию его на восьмивходо- вых мультиплексорах).

Группа 2 блоков элементов И предназначена для выделения по коду маски тех разрядов в каждом байте входной информации, которые должны быть выдвинуты за границу байта при выполнении сдвига под управлением младших разрядов кода сдвига.

Каждый блок элементов И можно выполнить на восьми двухвходовых элементах И, на первый вход которых поступает соответствующий разряд кода маски с выхода 16 формирователя 1, а на второй вход - соответствующий разряд соответствующего байта с информационного входа 10 устройства.

Группа 3 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ предназначена для формирования разрядов четности выдвигаемых разрядов, которые поступают на входы группы 3 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с выходов группы 2 блоков элементов И.

Группа 4 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ предназначена для формирования контрольных разрядов байтов при выполнен нии сдвигов под управлением младших разрядов кода сдвига. При этом следует отметить, что если на группу 11 входов контрольных разрядов устройства поступают контрольные разряды байтов, сформированные по четности, то на выходах 20,-20д группы 4 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ формируются предсказанные контрольные разряды по четности, а если на вход 11 поступают контрольные разряды байтов, сформированные по нечетности, то и на выходах 20.-20в формируются предсказанные у

С

контрольные разряды по нечетности.

Группы 3 и 4 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ могут быть реализованы на микро- g схемах ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ/ИЛИ 500ЛП107 или на двенадцатнвходовых схемах контроля четности 500ИЕ160.

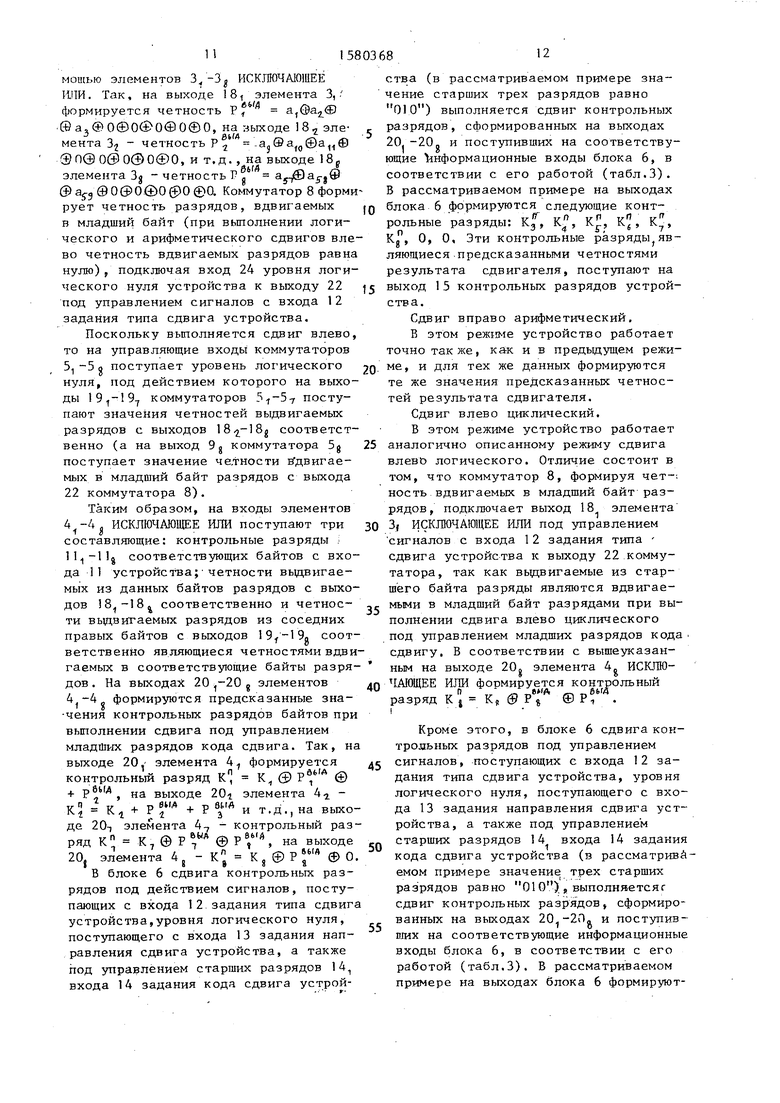

Группа 5 коммутаторов предназначены для формирования четности вдвигае- 55 -IS байтов с первого по восьмой мых в байты разрядов при выполнении соответственно являются предсказанныкода сдвига, в блоке 6 выполняется сдвиг контрольных разрядов в соответствии с табл.3, в которой детально поясняется функционирование блока 6 сдвига контрольных разрядов.

Отмечается, что при выполнении логических и арифметических сдвигов освобождающиеся разряды заполняются нулем () при организации контроля по четности или единицами () при организации контроля по нечетности.

Сформированные таким образом на выходах блока 6 контрольные разряды

-IS байтов с первого по восьмой соответственно являются предсказанныкода сдвига, в блоке 6 выполняется сдвиг контрольных разрядов в соответствии с табл.3, в которой детально поясняется функционирование блока 6 сдвига контрольных разрядов.

Отмечается, что при выполнении логических и арифметических сдвигов освобождающиеся разряды заполняются нулем () при организации контроля по четности или единицами () при организации контроля по нечетности.

Сформированные таким образом на выходах блока 6 контрольные разряды

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297116A1 |

| Устройство для формирования сигнала четности при сдвигах двоичных кодов | 1987 |

|

SU1481770A1 |

| Устройство для сдвига информации с контролем | 1989 |

|

SU1691893A2 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1297055A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1325481A1 |

| Устройство для сдвига операндов | 1987 |

|

SU1481741A1 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных системах обработки информации. Цель изобретения - повышение достоверности контроля устройства. Устройство содержит формирователь 1 кода маски, группу 2 блоков элементов И, группы 3, 4 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу 5 коммутаторов, блок 6 сдвига контрольных разрядов, коммутаторы 7, 8 и элемент И 9. Совокупность формирователя 1 кода маски, группы 2 блоков элементов И, групп 3, 4 элементов 1исключающее или, группы 5 коммутаторов, коммутаторов 7, 8 и элемента И 9 позволяет формировать предсказанный код четности байтов сдвигаемого числа, поступившего по информационному входу 10 устройства с учетом контрольных разрядов, поступивших на группу 11 входов контрольных разрядов устройства. Управление этим процессом ведется кодами, поступающими на входы12, 13 задания типа и направления сдвига утройства с младшими разрядами входа 14 задания кода сдвига, указывающими величину сдвига в пределах байта. Величина сдвига в блоке 6 сдвига контрольных разрядов определяется старшими разрядами входа 14 устройства, указывающими на сколько байтов сдвигается информация. Результирующий сигнал четности на выход 15 устройства поступает с выхода блока 6. 3 табл., 1 ил.

сдвигов как вправо, так и влево и мо- жет быть выполнена на микросхемах 500ЛК117, представляющих собой два элемента 2-3 И-2ИЛИ-НЕ/ИЛИ, причем при поступлении на управляющие входы коммутаторов группы 5 коммутаторов уровня логического нуля с входа 13 направления сдвига устройства на выходы 19,-198 коммутаторов 5,-5j подается информация с их первых входов, обеспечивая тем самым формирование предсказанных значений контрольных разрядов байтов на группе 4 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ при выполнении сдвигов влево под управлением младших разрядов кода сдвига, а при поступлении на управляющие входы коммутаторов 5..-5. уровня логической единицы с входа 13 направления сдвига устройства на выходы 19 .,-19 коммутаторов

С

5,-5j подается информация с их вторых входов, что обеспечивает формирование предсказанных значений контрольных разрядов байтов на группе 4 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ при выполнении сдвигов вправо под управлением младших разрядов кода сдвига.

Блок 6 сдвига контрольных разрядов предназначен для формирования предсказанных значений контрольных разрядов байтов при выполнении сдвигов под управлением старших разрядов кода сдвига. На информационные входы блока 6 сдвига контрольных разрядов поступают с выходов 20.,-20g элементов 4,-4а ИСКЛЮЧАЮЩЕЕ ИЛИ значения предми контрольными разрядами четности результата сдвигателя.

20

35

Первый коммутатор 7 формирует для крайнего левого байта сигнал четности вдвигаемых разрядов при выполнении сдвига вправо под управлением младших разрядов кода сдвига, при этом на вы25 ход 21 коммутатора 7 поступает значение с выхода 18, элемента 3. ИСКЛЮЧАЮЩЕЕ ИЛИ, если выполняется циклический сдвиг, уровень логического нуля с входа 24 - если выполняется логи30 ческий сдвиг, значение с выхода 23 элемента И 9 - если выполняется арифметический сдвиг.

Второй коммутатор 8 формирует для крайнего правого байта сигнал четности сдвигаемых разрядов при выполнении сдвига влево под управлением младших разрядов кода сдвига, при этом на выход 22 коммутатора 8 поступает значение с выхода 18, элемента Зл ИСКПЮ40 ЧАЮЩЕЕ ИЛИ - если выполняется циклический сдвиг, или уровень логического нуля с входа 24 - если выполняется логический или арифметический сдвиг.

Коммутаторы 7 и 8 могут быть реали зованы на элементах 500 ЛС 118 или 500 ЛС 119, Необходимо особо отметить, что в случае использования в устройстве только сдвига циклического вправо (циклический сдвиг влево заменяется в этом случае циклическим вправо на дополнительный код величины сдвига) необходимость введения т коммутатора 8 отпадает. В этом случае

45

50

сказанных четностей байтов результата

сдвигателя при выполнении сдвигов под

управлением младших трех разрядов кода, 55 димо постоянно подавать уровень логисдвига. Под действием сигналов, посту- ческого нуля с входа 24 устройства.

пающих с входа 12 типа сдвига и 13

направления сдвига, а также под управ- Элемент И 9 предназначен для форна первый вход коммутатора 5 & необхолением старших разрядов

14

входа

14

мирования сигнала четности вдвигаемых

ми контрольными разрядами четности результата сдвигателя.

Первый коммутатор 7 формирует для крайнего левого байта сигнал четности вдвигаемых разрядов при выполнении сдвига вправо под управлением младших разрядов кода сдвига, при этом на выход 21 коммутатора 7 поступает значение с выхода 18, элемента 3. ИСКЛЮЧАЮЩЕЕ ИЛИ, если выполняется циклический сдвиг, уровень логического нуля с входа 24 - если выполняется логический сдвиг, значение с выхода 23 элемента И 9 - если выполняется арифметический сдвиг.

Второй коммутатор 8 формирует для крайнего правого байта сигнал четности сдвигаемых разрядов при выполнении сдвига влево под управлением младших разрядов кода сдвига, при этом на выход 22 коммутатора 8 поступает значение с выхода 18, элемента Зл ИСКПЮЧАЮЩЕЕ ИЛИ - если выполняется циклический сдвиг, или уровень логического нуля с входа 24 - если выполняется логический или арифметический сдвиг.

Коммутаторы 7 и 8 могут быть реализованы на элементах 500 ЛС 118 или 500 ЛС 119, Необходимо особо отметить, что в случае использования в устройстве только сдвига циклического вправо (циклический сдвиг влево заменяется в этом случае циклическим вправо на дополнительный код величины сдвига) необходимость введения т коммутатора 8 отпадает. В этом случае

на первый вход коммутатора 5 & необхомирования сигнала четности вдвигаемых

единиц при выполнении арифметического сдвига вправо. Этот сигнал равен единице только в том случае, когда в ус1) ройстве выполняется арифметический сдвиг вправо на нечетное число разрядов отрицательного числа.

Устройство работает следующим образом.

Работа устройства рассматривается JQ в различных режимах на примере сдвига в нем восьми байтов входной информации afa2a s - а ц. на 19 двоичных разрядов (на вход 14 устройства подается прямой двоичный код величины едвига $ 010 ОН).

Пусть первый байт - а # является самым старшим и сопровождается контрольным разрядом четности k , a

на выходе 181 элементов 31 формируется четность 0 © 0 © 0 © 0 (±

О

а элемента

,Ф 0 © а

QJ а 3 Фа,

penj

Ч -©а,

, на выходе 18э 0©ОфО©0©

на выхо1Y4 w IS a1l И де 18 элемента 3$ формируется четность 0©0©ОФО©-0© ,3©а,4

ч f,

Коммутатор 7 формирует четность разрядов, вдвигаемых в старший байт (при выполнении логического сдвига вправо четность вдвигаемых разрядов равна нулю), подключая вход 24 уровня логического нуля устройства к выходу 21 под управлением сигналом входа 12 типа сдвига устройства.

Поскольку выполняется сдвиг вправо, то на управляющие входы коммутаторов 5f-5g поступает уровень логивосьмой байт aflasia fg - аи являет- 20 ческой единицы, под действием которося самым младшим и сопровождается контрольным разрядом четности k..

Сдвиг вправо логический.

На первый информационный вход форго на выходы 19 f 9g коммутаторов поступают значения четностей

- -Я

выдвигаемых разрядов с выходов 18 - 187 соответственно (на выход 19Т ком- мирователя 1 кода маски поступает уро-25 мутатОра 5 поступает значение четно30

35

вень логической единицы с входа 13 задания направления сдвига устройства, соответствующий выполнению сдвига вправо, а на второй информационный вход формирователя 1 подается значение младших трех разрядов 14 входа 14 задания кода сдвига устройства (в рассматриваемом примере 011). В соответствии с работой формирователя 1 (табл.1) на его выходах 16 в этом случае формируется код маски 000001 И, который далее поступает на первые входы блоков 2,-2в элемен о

тов И, на вторые входы которых подаются значения соответствующих байтов 10Т - 108 входной информации с входа 10 устройства, В результате этого на выходы блоков 21-2 элементов И передаются только те разряды соответствующих байтов I0t-10g, кото- 45 рые должны быть выдвинуты за границу байтов при выполнении сдвига под управлением младших разрядов кода сдвига. Для рассматриваемого случая на г выходах блока 2 формируется ре- 50 зультат маскирования 00000а,а7а. на выходах I 74 блока 2 г- OOOOOa a lfu in т.д., на выходах 17$ блока 28 - результат маскирования ОООООа а а,

сти вдвигаемых в старший байт разрядов с выхода 21 коммутатора 7).

Таким образом, на входы элементов 4 -4а ИСКЛЮЧАЮЩЕЕ ИЛИ поступают три составляющие: контрольные разряды

11,-110 соответствующих байтов с вхог 1 в

да 11 контрольных разрядов устройства; четности выдвигаемых из данных байтов разрядов с выходов 18f-18g соответственно и четности выдвигаемых разрядов из соседних левых байтов с выходов соответственно, являющиеся четностями вдвигаемых в соответствие байты разрядов. На выходах

40 элементов формируются предсказанные значения контрольных

разрядов байтов при выполнении сдвига под управлением младших разрядов кода сдвига. Так, на выходе 20.. элемента 4, формируется контрольный разряд К К1 © © 0, на выходе 20 элемента к К () Р А © Р,, и т.д., на выходе 20g элемента 48 - контрольный разряд К, К8 © ф . В блоке 6 сдвига контрольных разрядов под действием управляющих сигналов, поступающих с входа 12 задания типа сдвига устройства, уровня логической единицы, поступающего с входа

Далее на основании результатов мае- „ 13 задания направления сдвига устройкнрования полученных на выходах 17, - 17д с помощью элементов 3f-3g ИСКЛЮЧАЮЩЕЕ ИЛИ формируются четности выдвигаемых ъ каждом байте разрядов. Так,

ства, а также под управлением старших разрядов 14., входа 14 задания кода сдвига устройства (в рассматриваемом примере значение трех старших разряна выходе 181 элементов 31 формируется четность 0 © 0 © 0 © 0 (±

О

а элемента

,Ф 0 © а

QJ а 3 Фа,

penj

Ч -©а,

, на выходе 18э 0©ОфО©0©

на выхо1Y4 w IS a1l И де 18 элемента 3$ формируется четность 0©0©ОФО©-0© ,3©а,4

ч f,

Коммутатор 7 формирует четность разрядов, вдвигаемых в старший байт (при выполнении логического сдвига вправо четность вдвигаемых разрядов равна нулю), подключая вход 24 уровня логического нуля устройства к выходу 21 под управлением сигналом входа 12 типа сдвига устройства.

Поскольку выполняется сдвиг вправо, то на управляющие входы коммутаторов 5f-5g поступает уровень логи ческой единицы, под действием которо0

5

5 0

сти вдвигаемых в старший байт разрядов с выхода 21 коммутатора 7).

Таким образом, на входы элементов 4 -4а ИСКЛЮЧАЮЩЕЕ ИЛИ поступают три составляющие: контрольные разряды

11,-110 соответствующих байтов с вхог 1 в

да 11 контрольных разрядов устройства; четности выдвигаемых из данных байтов разрядов с выходов 18f-18g соответственно и четности выдвигаемых разрядов из соседних левых байтов с выходов соответственно, являющиеся четностями вдвигаемых в соответствие байты разрядов. На выходах

0 элементов формируются предсказанные значения контрольных

разрядов байтов при выполнении сдвига под управлением младших разрядов кода сдвига. Так, на выходе 20.. элемента 4, формируется контрольный разряд К К1 © © 0, на выходе 20 элемента к К () Р А © Р,, и т.д., на выходе 20g элемента 48 - контрольный разряд К, К8 © ф . В блоке 6 сдвига контрольных разрядов под действием управляющих сигналов, поступающих с входа 12 задания типа сдвига устройства, уровня логической единицы, поступающего с входа

ства, а также под управлением старших разрядов 14., входа 14 задания кода сдвига устройства (в рассматриваемом примере значение трех старших разря915

дов равно 010) выполняется сдвиг контрольных разрядов, сформированных на выходах 20,, 20j и поступивших на соответствующие информационные входы блока 6, в соответствии с его работой (табл.3). На выходах блока 6 в рассматриваемом примере формируются сле

дующие контрольные разряды: О, О, К , K, К3, K4, K, Ks. Эти контрольные

разряды, поступающие на выход 15 контрольных разрядов устройства, являютс предсказанными четностями результата сдвигателя,

Несовпадение хотя бы для одного байта результата сдвигателя значений его фактической и предсказанной четно стей указывает на наличие ошибки либо во входной информации сдвигателя, либо в его аппаратуре.

Сдвиг вправо арифметический,

В этом режиме устройство работает аналогично предыдущему. Отличие состоит только в том, что коммутатор 7, формируя четность вдвигаемых в старший байт разрядов, подключает выход 23 элемента И 9 под управлением сигналов с входа 12 типа сдвига устройства к выходу 21 коммутатора. При этом на выходе 23 элемента И 9 формирует- ся признак П,учитывающий четность вдвигаемых единиц при сдвиге отрица- тельного числа (в рассматриваемом примере признак П а , поскольку выполняется сдвиг вправо и уровень логической единицы поступает на первый вход элемента И 9, а младший разряд 143 входа 14 задания кода сдвига устройства, подключенный к второму входу элемента И 9 установлен в единицу).

В соответствии с выше указанным на выходе 20., элемента 4, ИСКЛЮЧАЮЩЕЕ ИЛИ формируется контрольный разряд К,

кп К. ч @ П.

1 1 Сдвиг вправо циклический.

В этом режиме устройство работает аналогично описанному режиму сдвига вправо логического. Отличие состоит в том, что коммутатор 7, формируя четность вдвигаемых в старший байт разрядов, подключает выход I8g элемента 3S ИСКЛЮЧАЮЩЕЕ ИЛИ под управлением сигналов с входа I2 типа сдвига

вания блока на выходах

17з блока 2s - результат

устройства к выходу 21 коммутатора,

так как выдвигаемые из младшего бай- 55 маскирования а assa 00000

та разряды являются вдвигаемыми в1Далее, на основании результатов

старший байт разрядами при выполнении маскирования, полученных, н.-i выходах

циклического сдвига вправо под управ- I71-I7g, формируются четности выдвилением младших разрядов кода сдвига.гаемых в каждом байте раярядов с поВ соответс выходе 20.

твил с выше указанным на элемента 4 ИСКЛЮЧАЮЩЕЕ

O

0

JQ ИЛИ формируется контрольный разряд

К

К, © Р

вид

© Р

вид

1 |

Кроме того, в блоке 6 сдвига контрольных разрядов под управлением сигналов, поступающих с входа 12 задания типа сдвига устройства, уровня логической единицы, поступающего с входа 13 задания направления сдвига устройства, а также под управлением

старших разрядов 14 входа 14 зада„/

ния кода сдвига устройства (в рассматриваемом примере значение трех старших разрядов равно 010), выполняется сдвиг контрольных разрядов, сформированных на выходах 20f-20g и поступивших на соответствующие информационные входы блока 6, в соответствии с его работой (табл.3).

В рассматриваемом примере на выходах блока 6 формируются следующие конQ

5

0

5

трольные разряды:

г ПТТ П7Г Лтг (1

к1;, к

к,, к

5 Кэ, к, К Ј и К Ј. Эти контрольные разряды, являющиеся предсказанными четностями результата сдвигателя, поступают на выход 15 контрольных разрядов устройства.

Сдвиг влево логический.

На управляющий вход фоомирователя 1 кода маскг поступает уровень логического нуля с входа 13 задания направления сдвига устройства, соответствующий выполнению сдвига влево, а на информационные входы формирователя 1 подается значение младших трех разрядов 14-1 входы 14 задания кода сдвига устройства (в рассматриваемом примере 011). В соответствии с работой формирователя 1 (табл.1), на его выходах 16 в этом случае формируется код маски 11100000, который далее поступает на первые входы блоков . элементов И, на вторые входы которых подаются значения соответствующих байтов 101-10. входной ин1о

формации с входа 10 данных устройст- ства. В результате этого для рассмат0

риваемого случая на выходах 17,, блока 2. формируется результат маскиро-

на выходах 17 За,„ а„ иОООО и т.д.

(

вания блока на выходах

a,aza Э00000

0а„ 00000

2 17з блока 2s - результат

мощью элементов 3„-3 ИСКЛЮЧАЮЩЕЕ ИЛИ. Так, на выходе 18, элемента 3, формируется четность Р., @а3@0©0(± 0©0©0, на выходе 8г эле- мента Зг - четность а. ®0© 0(5 О©О©О, и т.д. , на выходе 18, элемента 3g - четность Р g ©ayj® 0® О ©0 ©0. Коммутатор 8форми рует четность разрядов, вдвигаемых в младший байт (при выполнении логического и арифметического сдвигов влево четность вдвигаемых разрядов равна нулю), подключая вход 24 уровня логического нуля устройства к выходу 22 под управлением сигналов с входа 12 задания типа сдвига устройства.

Поскольку выполняется сдвиг влево, то на управляющие входы коммутаторов 5,, -5 о поступает уровень логического нуля, под действием которого на выходы 19т-197 коммутаторов 5t-57 поступают значения четностей выдвигаемых разрядов с выходов соответственно (а на выход 9g коммутатора 5g поступает значение четности в двигае- мых в младший байт разрядов с выхода 22 коммутатора 8).

Таким образом, на входы элементов , ИСКЛЮЧАЮЩЕЕ ИЛИ поступают три составляющие: контрольные разряды 11.,-llj соответствующих байтов с входа 1 1 устройства; четности выдвигаемых из данных байтов разрядов с выходов JSj-lSj соответственно и четное- ти выдвигаемых разрядов из соседних правых байтов с выходов 19f-19« соответственно являющиеся четностями вдвигаемых в соответствующие байты разря- дов. На выходах 20 ,-20g элементов

4 -4„ формируются предсказанные значения контрольных разрядов байтов при выполнении сдвига под управлением младших разрядов кода сдвига. Так, на выходе 201 элемента 4 формируется контрольный разряд к К, ® Pe, A G

+ Р

6ЫЛ

на выходе 20 элемента 4 ВИА

вид

К Кг + Р р + Р и т.д., на выходе 20т элемента 47 - контрольный разряд К К7 ® Р ™ © Р V , на выходе 20, элемента 4 g - К К g © Р Ь А Ф О. В блоке 6 сдвига контрольных разрядов под действием сигналов, поступающих с входа 12 задания типа сдвига устройства,уровня логического нуля, поступающего с входа 13 задания направления сдвига устройства, а также под управлением старших разрядов 141 входа 14 задания кода сдвига устрой

,. о

5

ства (в рассматриваемом примере значение старших трех разрядов равно 010) выполняется сдвиг контрольных разрядов, сформированных на выходах 20. -20. и поступивших на соответствующие Информационные входы блока 6, в соответствии с его работой (табл.3). В рассматриваемом примере на выходах блока 6 формируются следующие контрольные разряды: Kf, KЈ, KЈ, K , к, К8°, О, О, Эти контрольные разряды являющиеся предсказанными четностями результата сдвигателя, поступают на выход 15 контрольных разрядов устройства.

Сдвиг вправо арифметический.

В этом режиме устройство работает точно также, как и в предыдущем режиме, и для тех же данных формируются те же значения предсказанных четностей результата сдвигателя.

Сдвиг влево циклический.

В этом режиме устройство работает аналогично описанному режиму сдвига влево логического. Отличие состоит в том, что коммутатор 8, формируя четность вдвигаемых в младший байт разрядов, подключает выход 18 элемента 3, ИСКЛЮЧАЮЩЕЕ ИЛИ под управлением сигналов с входа 12 задания типа - сдвига устройства к выходу 22 коммутатора, так как выдвигаемые из старшего байта разряды являются вдвигаемыми в младший байт разрядами при выполнении сдвига влево циклического под управлением младших разрядов кода сдвигу. В соответствии с вышеуказанным на выходе 20л элемента 4, ИСКЛЮЧАЮЩЕЕ ИЛИ формируется контрольный разряд Knt К, 0Р Г ©Р..

Кроме этого, в блоке 6 сдвига контрольных разрядов под управлением сигналов, поступающих с входа 12 задания типа сдвига устройства, уровня логического нуля, поступающего с входа 13 задания направления сдвига устройства, а также под управлением старших разрядов 14 входа 14 задания кода сдвига устройства (в рассматриваемом примере значение трех старших разрядов равно 010) , выполняетсяг сдвиг контрольных разрядов, сформированных на выходах 20,-20. и поступивших на соответствующие информационные входы блока 6, в соответствии с его работой (табл.3). В рассматриваемом примере на выходах блока 6 формируются следующие контрольные разряды: Kj, , KЈ, К/, К7П, К, К, К2- Эти | контрольные рйзряды, являющиеся предсказанными четностями результата сдви- с гателя, поступают на выход 15 контрольных разрядов устройства.

Формула изобретения

Устройство для предсказания четности результата сдвигателя, содержащее формирователь кода маски, два коммутатора, элемент И и группу блоков элементов И, причем первый и второй входы элемента И подключены соответственно к младшему разряду входа задания кода сдвига устройства и старшему разряду информационного входа устройства, разряды выхода формирователя кода маски соединены с первым входом первого блока элементов И группы, отличающееся тем, что, с целью повышения достоверности контроля устройства, в него введены группа коммутаторов, две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и блок сдвига контрольных разрядов, причем вход задания направления сдвига блока сдвига контрольных разрядов, третий вход - элемента И и первый информационный вход формирователя кода маски подключены к входу задания направления сдвига устройства, разряды байтов информа ционного входа устройства подключены к вторым входам соответствующих блоков элементов И группы, разряды выхода формирователя кода маски соединены с первыми входами соответствующих блоков элементов И гр уппы, выход 1-го блока элементов И группы соединен с соответствующим входом 1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, выход которого соединен с первым входом

1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы (1 4 i m, где m - число блоков И в группе), выход которого соединен с i-м информационным входом блока

сдвига контрольных разрядов, информационный выход которого является выходом контрольных разрядов устройства, выход элемента И соединен с первым информационным входом первого коммутатора, второй и третий информационные входы которого соединены соответственно с шиной нулевого потенциала устройства и выходом последнего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, первый и второй информационные входы второго коммутатора соединены соответственно с шиной нулевого потенциала и выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, выход первого коммутатора соединен с первым информационным входом первого коммутатора группы, выход каждого j-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединен с первым информационным входом (j+l)-ro коммутатора группы (I Јj m-1), выход каждого 1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединен с вторым информационным входом (1-1)-го коммутатора группы (2 1 4т), выход второго коммутатора соединен с вторым информационным входом последнего коммутатора группы, вход задания типа сдвига блока сдвига контрольных разрядов и управляющие входы первого и второго коммутаторов подключены к входу задания типа сдвига устройства, вход задания направления сдвига устройства подключен к управляющим входам коммутаторов группы, выходы которых соединены с вторыми входами соответствующих элементов ИС- ЛЮЧАЮЩЕЕ ИЛИ второй группы, третьи входы которых образуют группу входов контрольных разрядов устройства, младшие разряды входа задания величины сдвига устройства подключены к второму информационному входу формирователя кода маски,.старшие разряды входа задания кода сдвига устройства подключены к входу задания кода величины сдвига блока сдвига контрольных разрядов.

Примечание: R и R - прямой и инверсный уровня логического сигнала, установленного на управляющем входе формирователя 1 (на входе 13 направления сдвига устройства)

Таблица I

ичес

О (влево) 000

001 010 011 100 101 ПО 1 1 1

0 (влево)

ес-

000 001 010 011 100 101 ПО И)

Цикличес- 1 (впраТаблица 3

И2 ИЗ

И4

И5

И6

И7

И8

| Устройство для сдвига информации с контролем | 1983 |

|

SU1095184A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1300477, кл, G 06 F 11/10, 1985. | |||

Авторы

Даты

1990-07-23—Публикация

1988-04-04—Подача