31481796

Изобретение относится к вычисли

тельной технике и может быть использовано при определении функции распределения случайных процессов при малом числе наблюдений.

Цель изобретения - повышение точности оценивания функции распределения при малом числе наблюдений.

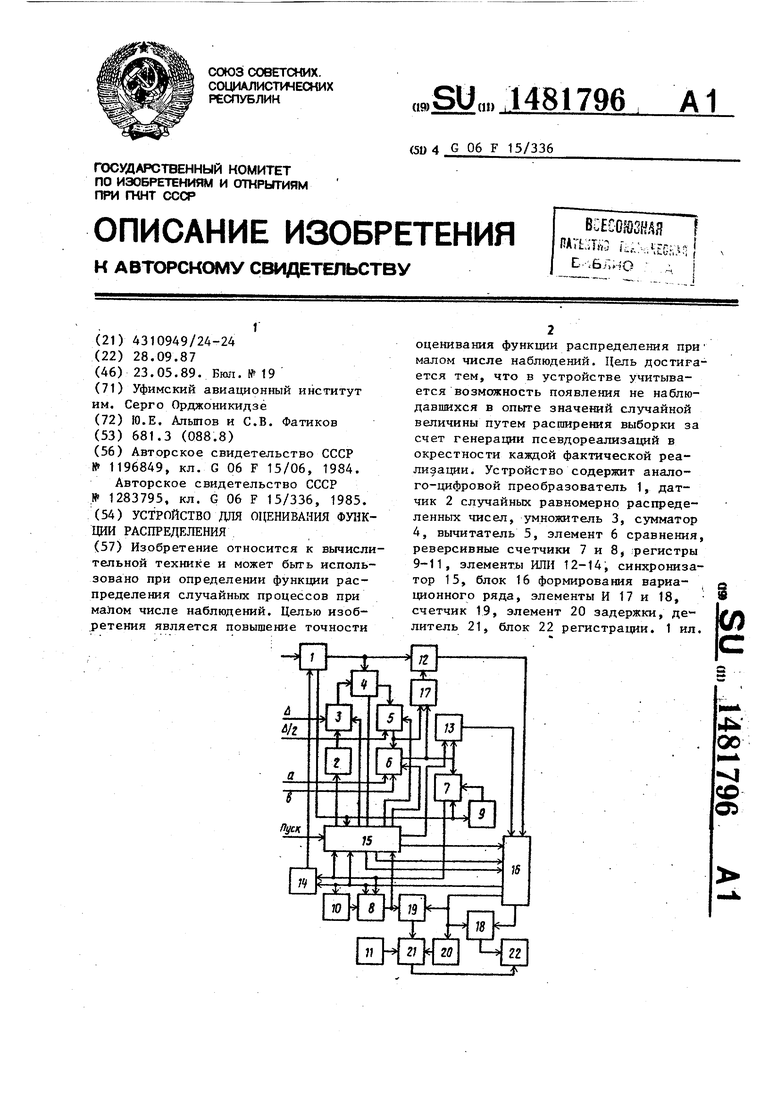

На чертеже приведена функциональная схема устройства.

Устройство содержит аналого-цифровой преобразователь 1, датчик 2 случайных равномерно распределенных чисел, умножитель 3, сумматор 4,вы- читатель 5, элемент 6 сравнения,реверсивные счетчики 7 и 8, регистры 9-11, элементы ИЛИ 12-14, многоступенчатый синхронизатор 15, блок 16 формирования вариационного ряда,элементы И 17, 18, счетчик 19, элемент 20 задержки, делитель 21 и блок 22 регистрации.

Устройство работает следующим образом,

При поступлении импульса на вход запуска синхронизатора 15 блок 16 устанавливается в режим очистки для подготовки к сортировке новой информации. По окончании цикла очистки на выходе сигнала готовности блока 16 появляется импульс, поступающий через элемент ИЛИ 14 на управляющий вход аналого-цифрового преобразователя (АЦП) 1, на информационный вход которого подан исследуемый случайный сигнал X(t). Кроме того, по этому импульсу с реверсивный счетчик 8 из регистра 10 заносится требуемое число реализаций случайного процесса N. Блок 16 устанавливается в режим записи. По окончании преобразования реализации процесса X(t) на одноименном выходе АЦП 1 формируется импульс разрешающий запись кода реализации в блок 16. Кроме того, по этому им пульсу в реверсивный счетчик 7 из регистра 9 заносится число псевдореа лизаций М, генерируемых для одной реализации процесса.

Рассмотрим цикл генерации псевдореализаций Х-,; (j 1 , М) для реализации Х1. По импульсу с выхода синхронизатора 15 на выходе датчика 2 случайных равномерно распределенных чисел формируется одно случайное чис ло, принадлежащее интервалу 0; 1J. Полученная псевдореализация X масштабируется на фактический интервал

-

10

15

20

25

30

i

, -

- 5S

35

40

45

50

4

Хп - А/2, X, + 4/2 (Д- апертура), Xij Х + X j .Д - Л/2.

Эта операция осуществляется умножителем 3, сумматором 4 и вычитате- лем 5. Элемент 6 сравнения проверяет принадлежность полученной псевдореализации Xti интервалу анализа. Если Хп, € а,ЬЗ , то на выходе элемента 6 формируется единичный импульс, разрешающий запись Хт} в блок сортировки. Одновременно содержимое реверсивного счетчика 7 уменьшается на единицу. Если же Xtj I a,b, то запись в блок 16 запрещена - псевдореализация отбрасывается. По окончании обработки i-й реализации; т.е. когда в блок 16 запишутся М псевдо-, реализаций X-,j, на выходе обнуления1 реверсивного счетчика 7 формируется импульс, поступающий через элемент ИЛИ 14 на вход запуска АЦП 1, на выходе которого формируется очередная (1+1)-я реализация процесса. Кроме того, по этому импульсу содержимое реверсивного счетчика 8 уменьшается на единицу.

По окончании цикла генерации псевдореализаций для реализации Хм на выходе обнуления реверсивного счетчика 8 формируется импульс, по кото- рому блок 16 устанавливается в режим чтения. Элементы полученного вариационного ряда длиной N M считываются поочередно из блока 16. Каждый элемент сопровождается импульсом на выходе окончания формирования члена ряда блока 16, поступающим в предварительно обнуленный счетчик 19. В регистре 11 хранится число К N-M элементов расширенной выборки. Таким образом, в блок 22 регистрации поступают значения функции распределения i/K, i - 1, К и соответствующие им значения аргумента.

Многоступенчатьй синхронизатор по сигналу запуска последовательно формирует на соответствующем выходе последовательности синхроимпульсов, обеспечивающие поочередную работу соответствующих блоков.

Формула изобретения

Устройство для оценивания функции распределения, содержащее умножитель,) сумматор, вычитатель, элемент сравнения, регистр, счетчик, элемент

514

задержки, делитель и блок регистрации, отличающееся тем, что, с целью повышения точности оценивания при малом числе наблюдений, в него введены аналого-цифровой преобразователь, датчик случайных равномерно распределенных чисел, два регистра, два реверсивных счетчика, три элемента ИЛИ, два элемента И, многоступенчатый синхронизатор и блок формирования вариационного ряда причем первый вход запуска многоступенчатого синхронизатора является входом запуска устройства, информационный вход аналого-цифрового преобразователя является информационным входом устройства, информационный выход аналого-цифрового преобразователя соединен с первым входом первого элемента ИЛИ и с первым информационным входом сумматора, выход.окончания преобразования аналого-цифрового преобразователя соединен с вторым входом запуска многоступенчатого синхронизатора, с входом разрешения считывания первого регистра и тактовым входом первого реверсивного счетчика, первый и второй выходы многоступенчатого синхронизатора соединены соответственно с входом обнуле-. ния блока формирования вариационного ряда и с первым входом второго элемента ИЛИ, третий выход многоступенчатого синхронизатора - с тактовым входом блока формирования вариационного ряда, четвертый выход многоступенчатого синхронизатора - с тактовым входом датчика случайных равномер но распределенных чисел, выход которого соединен с первым информационным входом умножителя, второй информационный вход которого является входом задания апертуры устройства, тактовый вход умножителя соединен с пятым выходом многоступенчатого синхронизатора, а выход соединен с.вторым информационным входом сумматора, тактовый вход которого соединен с шестым выходом многоступенчатого синхронизатора, выход сумматора соединен с входом уменьшаемого вычитателя, вход вычитаемого которого является входом задания половинного значения апертуры устройства, тактовый вход вычитателя соединен с седьмым выходом многоступенчатого синхронизатора, а выход соединен с первым входом первого элемента И и информационным

0

5

7966

входом элемента сравнения, входы задания значения верхнего и нижнего порога которого являются соответственно входами задания правой и левой

5 границ интервала анализа устройства, тактовый вход элемента сравнения соединен с восьмым выходом многоступенчатого синхронизатора, а выход соединен с вычитающим входом первого реверсивного счетчика, вторым входом первого элемента И и вторым входом второго элемента ИЛИ, выход которого соединен с входом разрешения записи блока формирования вариационного ряда, выход первого элемента И соединен с вторым входом первого элемента ИЛИ, выход которого соединен с информационным входом блока формирования вариационного ряда, вход разрешения считывания которого соединен с девятым выходом многоступенчатого синхронизатора, выход первого регистра соединен с входом задания начального

д значения первого реверсивного счетчика, выход обнуления которого соединен с первым входом третьего элемента ИЛИ, первым входом останова многоступенчатого синхронизатора и вычитающим входом второго реверсивного счетчика, вход задания начального состояния которого соединен с выходом второго регистра, вход разрешения считывания которого соединен с тактовым входом второго реверсивного

0

0

5

0

5

0

счетчика, вторым входом третьего элемента ИЛИ, третьим входом запуска многоступенчатого.синхронизатора и выходом сигнала готовности блока формирования вариационного ряда, выход обнуления второго реверсивного счетчика соединен с вторым входом останова многоступенчатого синхронизатора и входом установки в О счетчика, выход третьего элемента ИЛИ соединен с входом запуска аналого- цифрового преобразователя, выход окончания формирования члена ряда блока формирования вариационного ряда соединен со счетным входом счетчика, первым входом второго элемента И и-через элемент задержки с тактовым входом делителя, вход делителя которого соединен с выходом третьего регистра, вход делимого де- лителя соединен с выходом счетчика, а выход соединен с входом значения функции блока регистрации, вход значения аргумента которого соединен с

выходом второго элемента И, второй ционным выходом блока формирования вход которого соединен с информа- вариационного ряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Статистический анализатор | 1986 |

|

SU1401482A1 |

| Статистический анализатор | 1987 |

|

SU1499376A1 |

| Статистический анализатор | 1990 |

|

SU1698892A1 |

| Устройство для определения закона распределения случайной величины | 1986 |

|

SU1425713A1 |

| Статистический анализатор | 1986 |

|

SU1354211A1 |

| Статистический анализатор | 1987 |

|

SU1441418A1 |

| Статистический анализатор | 1986 |

|

SU1352518A1 |

| Устройство для определения закона распределения случайной величины | 1987 |

|

SU1425715A1 |

| Статистический анализатор | 1989 |

|

SU1631557A1 |

| Статистический анализатор | 1986 |

|

SU1397939A1 |

Изобретение относится к вычислительной технике и может быть использовано при определении функции распределения случайных процессов при малом числе наблюдений. Целью изобретения является повышение точности оценивания функции распределения при малом числе наблюдений. Цель достигается тем, что в устройстве учитывается возможность появления не наблюдавшихся в опыте значений случайной величины путем расширения выборки за счет генерации псевдореализаций в окрестности каждой фактической реализации. Устройство содержит аналого-цифровой преобразователь 1, датчик 2 случайных равномерно распределенных чисел, умножитель 3, сумматор 4, вычитатель 5, элемент 6 сравнения, рерсивные счетчики 7 и 8, регистры 9-11, элемент ИЛИ 12-14, синхронизатор 15, блок 16 формирования вариационного ряда, элементы И 17 и 18, счетчик 19, элемент 20 задержки, делитель 21, блок 22 регистрации. 1 ил.

| Устройство для сортировки информации | 1984 |

|

SU1196849A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Статистический анализатор | 1985 |

|

SU1283795A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1987-09-28—Подача