Изобретение относится к автоматике и вь числительной технике и может быть использовано при построении асинхронных вычислительных устройств приема и передачи информации.

Цель изобретения - упрощение асинхронного последовательного регистра.

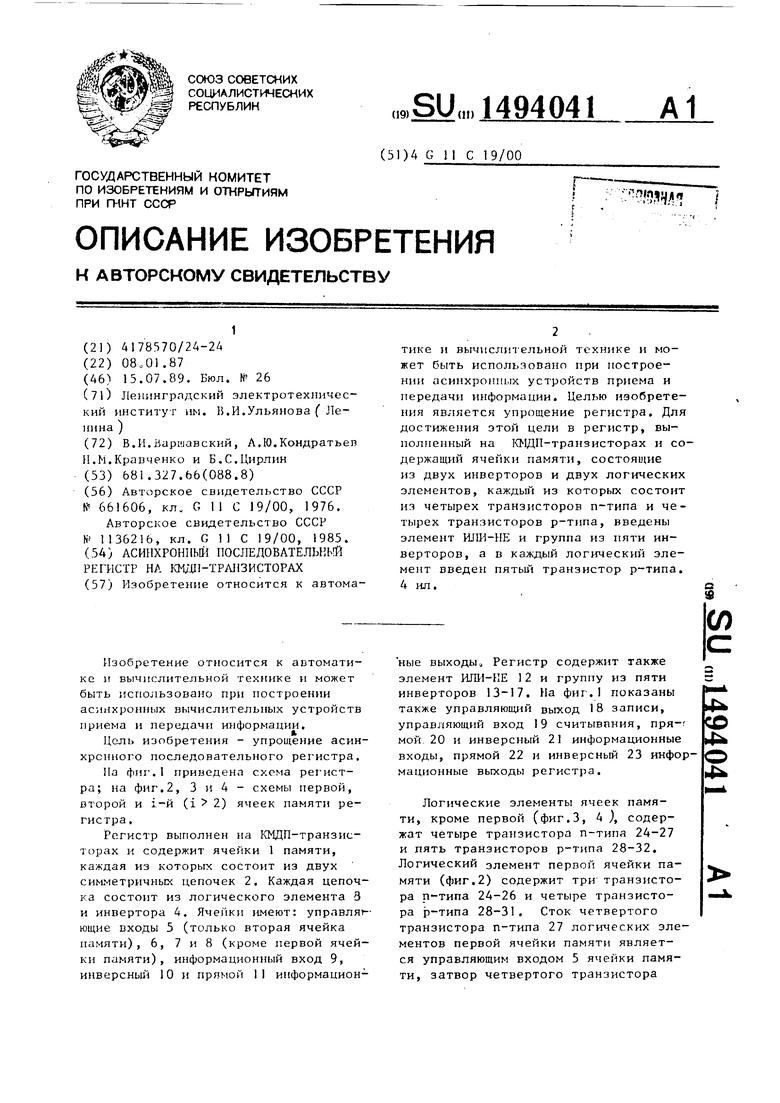

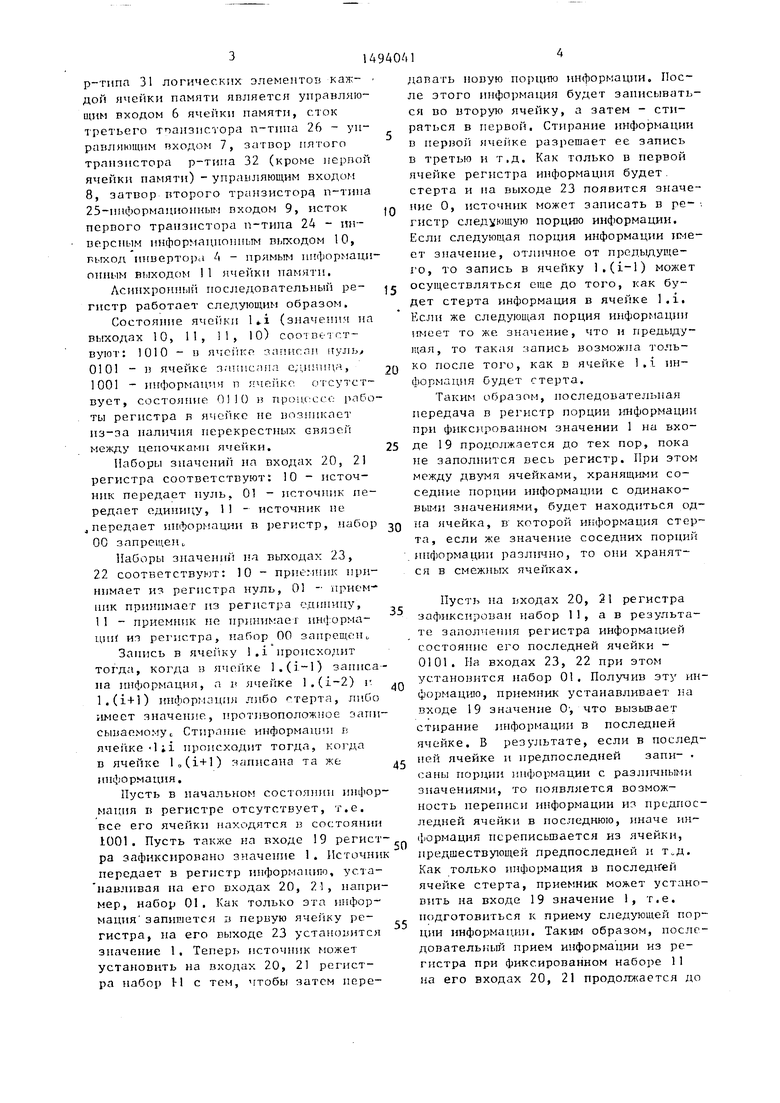

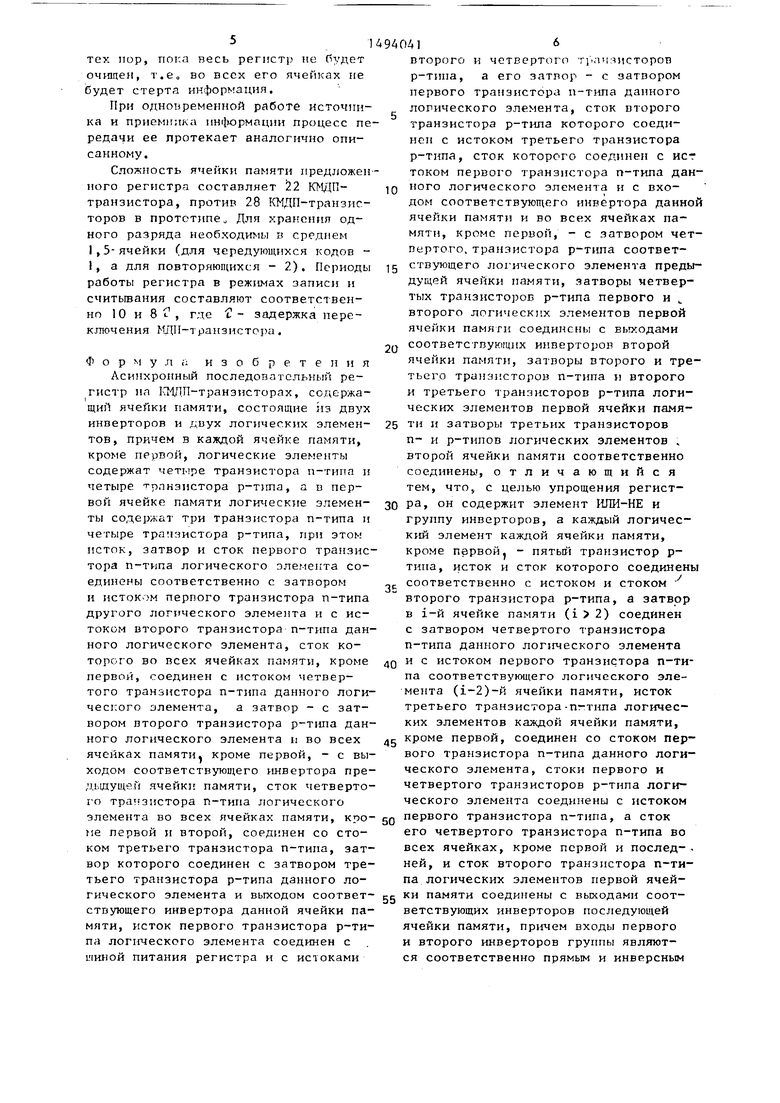

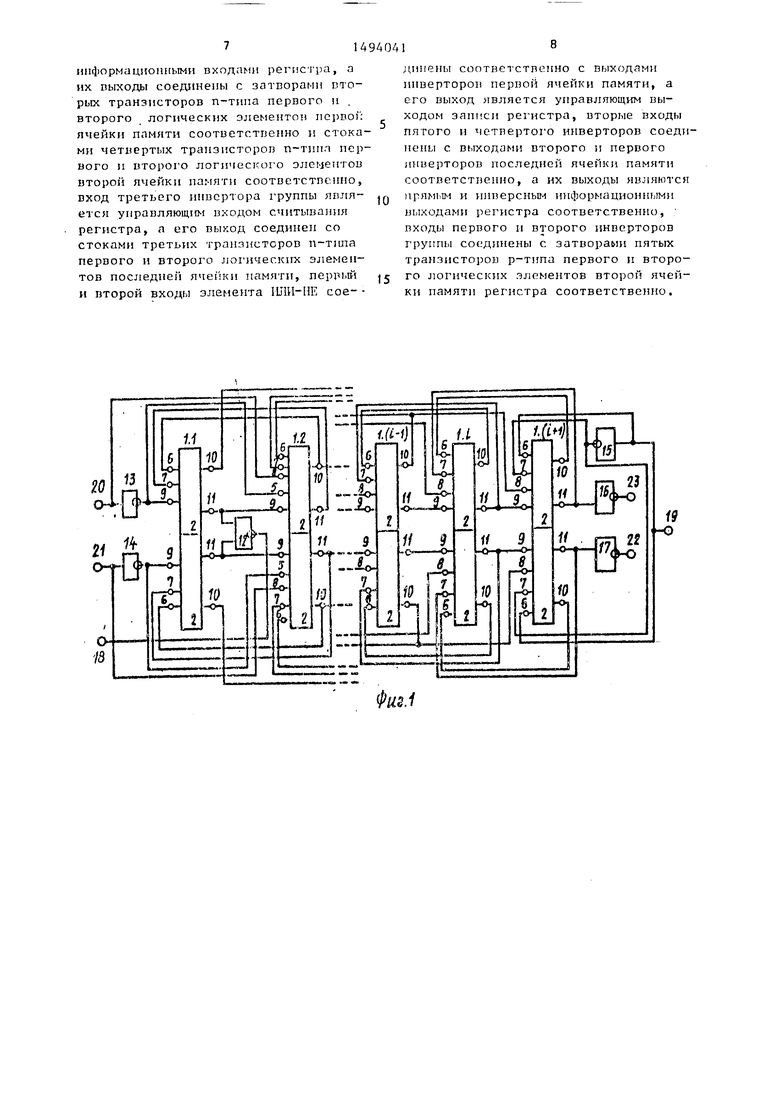

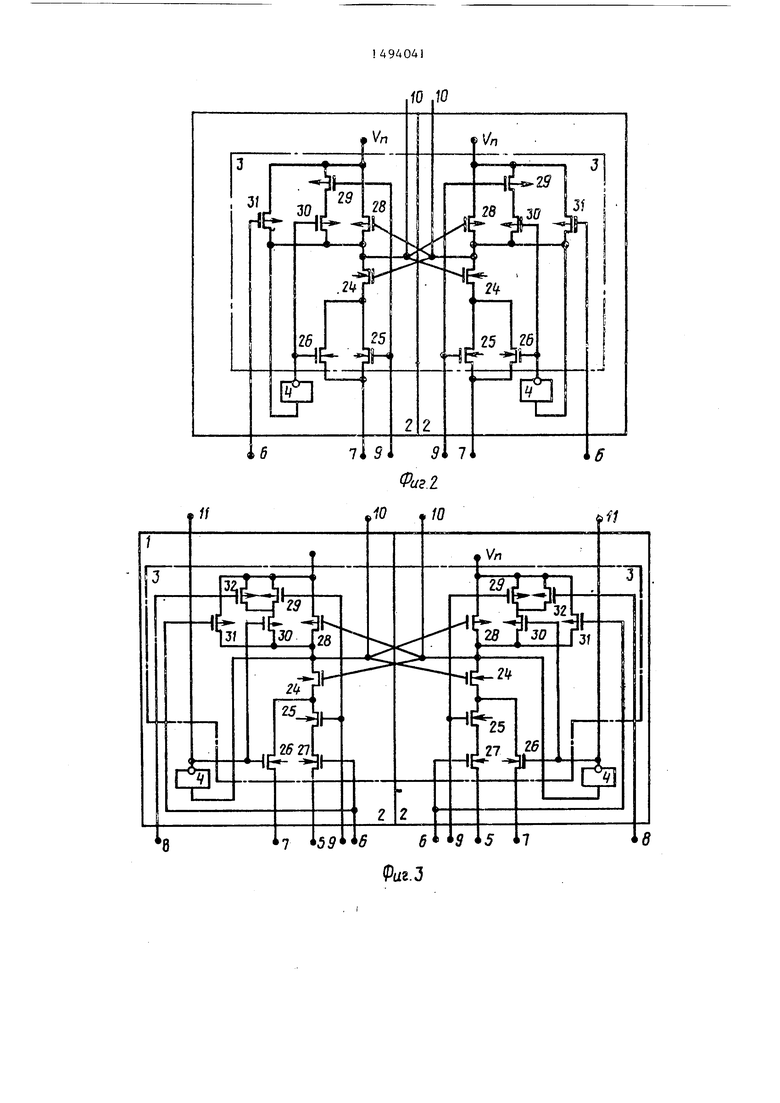

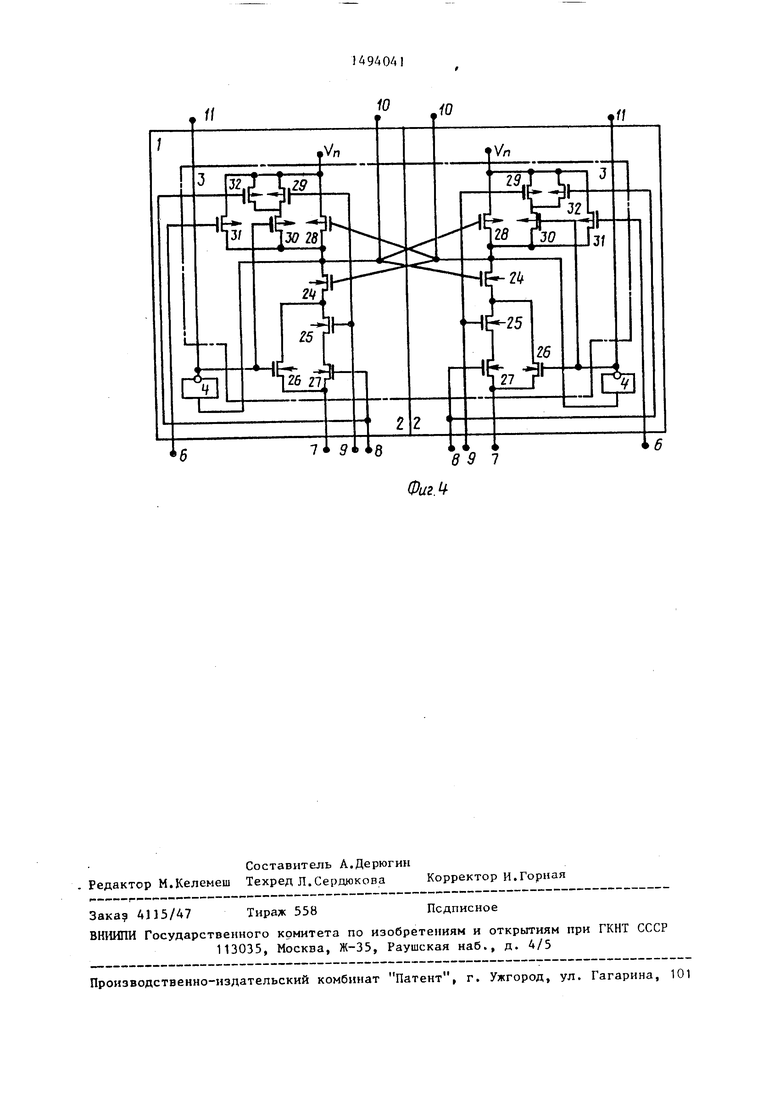

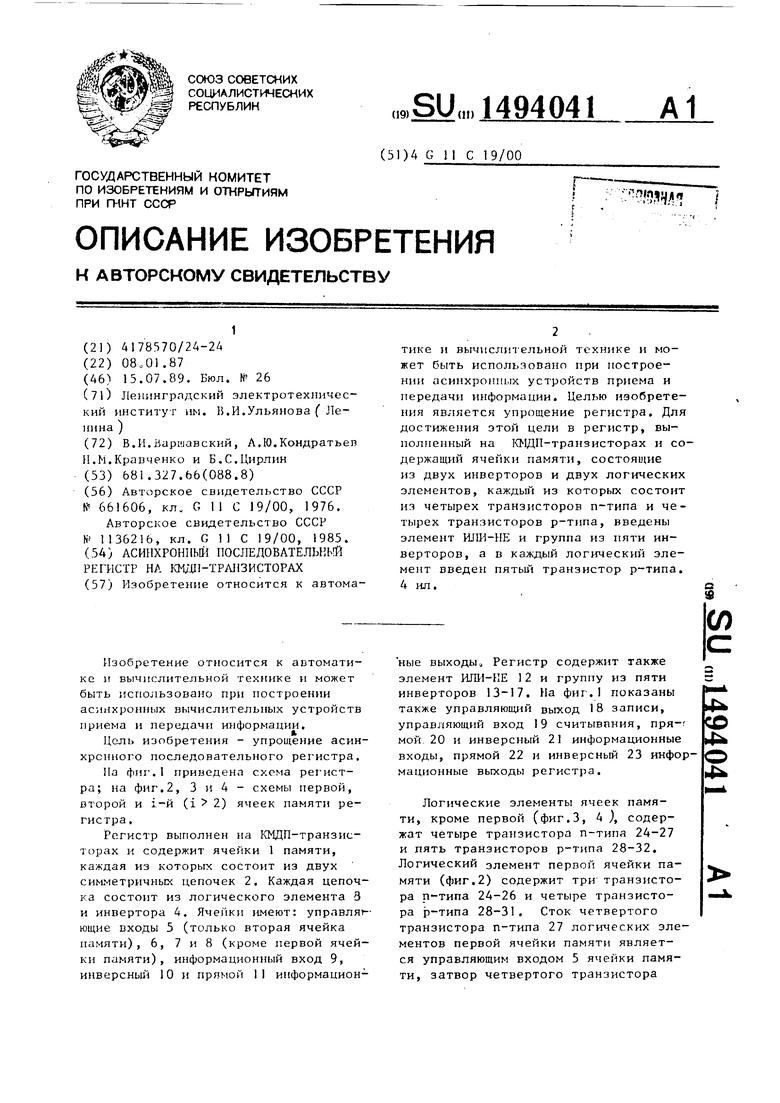

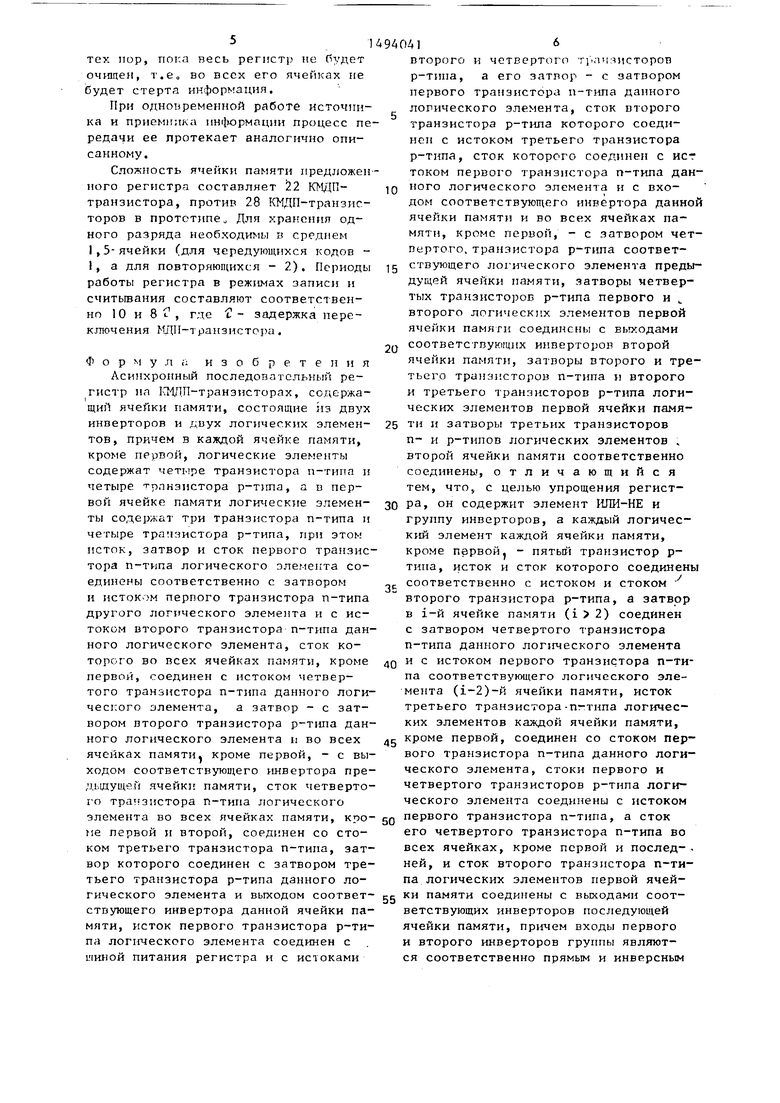

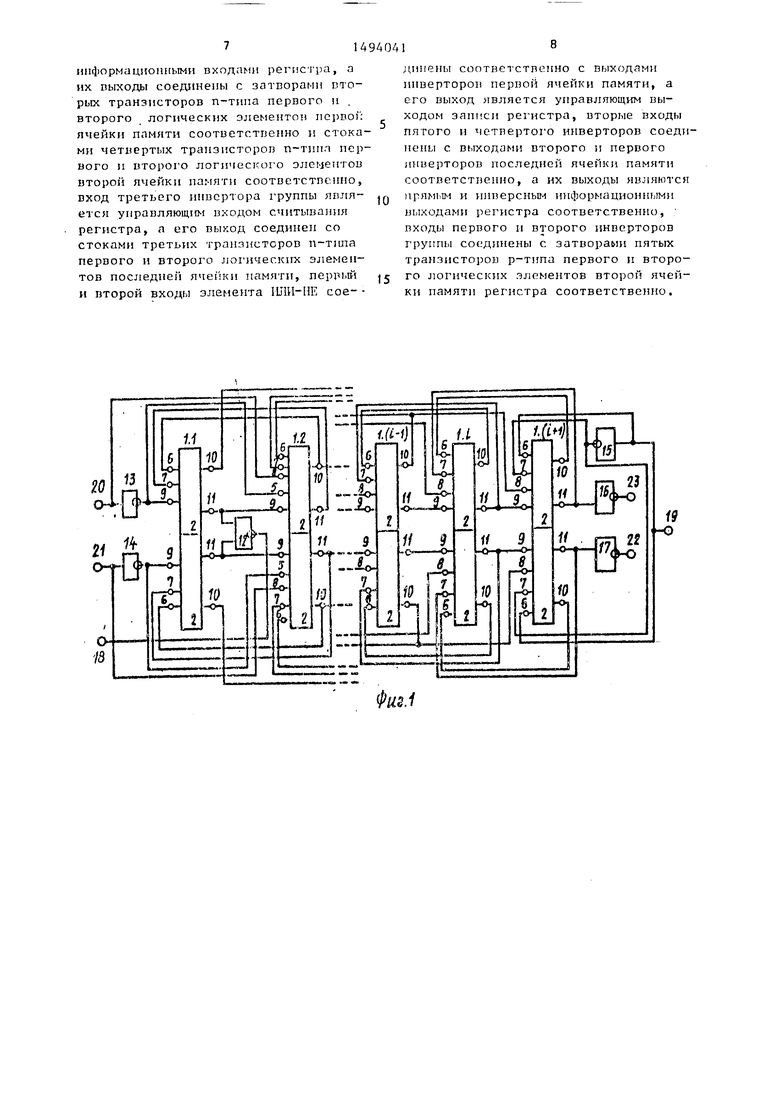

На фиг.1 приведена схема регистра; на фиг.2, 3 и 4 - схемы первой, второй и i-й (i 2) ячеек памяти регистра.

Регистр выполнен на КМДП-транзис- торах и содержит ячейки 1 памяти, каждая из которых состоит из двух симметричных цепочек 2. Каждая цепочка состоит из логического элемента 3 и инвертора 4. Ячейки имеют: управляв- ющие входы 5 (только вторая ячейка памяти), 6, 7 и 8 (кроме первой ячейки памяти), информационный вход 9, инверсньш 10 и прямой II информацион ные выходы. Регистр содержит также элемент ИЛИ-НЕ 12 и группу из пяти инверторов 13-17. На фиг.1 показаны также управляющий выход 18 записи, управляющий вход 19 считывания, пря-f мой 20 и инверсный 21 информационные входы, прямой 22 и инверсный 23 информационные выходы регистра.

Логические элементы ячеек памяти, кроме первой (фиг.З, 4 ), содержат четыре транзистора п-типа 24-27 и пять транзисторов р-типа 28-32, Логический элемент первой ячейки памяти (фиг.2) содержит три транзистора п-типа 24-26 и четыре транзистора р-типа 28-31. Сток четвертого транзистора п-типа 27 логических элементов первой ячейки памяти является управляющим входом 5 ячейки памяти, затвор четвертого транзистора

31

р-типа 31 логических элементов кал;- дои ячейки памяти является управляющим входом 6 памяти, сток третьего тпаизистора п-типа 26 - управляющим входом 7, затвор пятого транзистора р-типа 32 (кроме нерпой ячейки памяти) - управляющим входом 8, затвор второго транзисторс1 п-типа 25-информациониым входом 9, исток первого транзистора п-типа 24 инверсным информацнонным выходом 10, выход инверторе А - прямым информационным выходом 11 ячейки памяти,

Асинхронный последовательный ре- гистр работает следующим образом.

Состояние ячейки (значении па выходах 10, 11, 11, 10) соответствуют: 1010 - 13 ячсГпсп записпп. нуль, 0101 - в ячейке затшсана еднгпща, 1001 - информан иг п яче11кс. от сутст- вует, состо}И1ие 0110 в лрои,с:с(. о работы регистра в ячейке не возникает из-за наличия перекрестных связей между цепочками ячейки.

Наборы значений на входах 20, 21 регистра соответствуют: 10 - источник передает нуль. 01 - источник пе

редает единиг у.

источник не

30

35

передает информации в регистр, набор

00запрещези

Наборы значений на выходах 23, 22 соответствуют: 10 - приемник принимает из регистра нуль, 01 - прием 1U1K принимает из регистра единицу,

11 - приемник не npiiHiibuie г информации из регистра, набор 00 запрещеги

Занись в ячейку l.i происходит тогда, когда в ячейке l,(i-l) записана информация, а и ячейке l.(i-2) v. g l.(i+) информация либо стерта, либо шеет значение, нротивоположиое записываемому Стирание информации в яче1 1ке 1 1 происходит тогда, когда в ячейке lo(i+l) записана та же информация.

Пусть в начальном состоянии информация в регистре отсутствует, т.е. все его ячейки находятся в состояьи И 1001. Пусть также на входе 19 регистра зафиксировано значение 1. Источник передает в регистр информацшо, уста- навливая на его входах 20, 21, например, набор 01. Как только эта инфор- мацт1я запишется з первую ячейку регистра, на его выходе 23 установится значение 1 , Теперь источн1 к может установить на входах 20, 21 регистра набор I-1 с тем, чтобы затем нере50

55

j

0 5

0

5

g

0

5

давать новую порцию инфорь ации. После этого информация будет записываться во вторую ячейку, а затем - стираться в первой. Стирание информации в нервоГ ячейке разрешает ее запись в третью и т.д. Как только в первой ячейке регистра информацня будет. стерта и на выходе 23 появится значение О, источник может записать в ре- , гистр след ющую порцию информации. Если следующая порция информации имеет значение, отличное от предыдущего, то запись в ячейку l.(i-l) может осуществляться еще до того, как будет стерта информация в ячейке l.i. Если же следующая порция информации меет то же значение, что и предыду- гдая, то такая запись возможна только после того, как в ячейке l.i информация будет стерта.

Таким образом, последовательная передача в регистр порции шформации при фиксированном значении 1 на входе 19 продолжается до тех пор, пока не заполнится весь регистр. При этом между двумя ячейками, хранящими соседние порции информации с одинако- вьии значениями, будет находиться одна ячейка, в которой информация стерта, если же значение соседних порций Ш1формации различно, то они хранятся в смежных ячейках.

Пусть на входах 20, 21 регистра зафиксирован набор 11, а в результате запол11ення регистра информацией состояннс его последней ячейки - 0101. На входах 23, 22 при этом установится набор 01. Получив эту ин- формацио, приемник устанавливает на входе 19 значение О , что вызьюает стирание информации в последней ячейке. В результате, если в последней ячейке и предпоследней запи- саны иорции информации с различными значениями, то появляется возможность перениси информации из предпоследней ячейки в последнюю, иначе информация нсреписьшается из ячейки, иредшествующей предпоследней и . Как только информация ц последней ячейке стерта, приеьшик может установить на входе 19 значение 1, т.е. подготовиться к приему след: ющей нор- ции информации. Таким образом, после- дователЫ(ЬЙ прием информации из регистра при фиксированном наборе 11 на его входах 20, 21 продолжается до

тех пор, пока весь регистр не будет очищен, т.бо во всех его ячейках не будет стерта информация,

При одновременной работе источника и приемника информации процесс передачи ее протекает аналогично описанному.

Сложность ячейки памяти предложенного регистра составляет 2 траизистора, против 28 КМДП-транзис- торов в прототипе о Для хранения одного разряда необходимы в среднем 1,5-ячейки (для чередующихся кодов - 1, а для повторяющихся - 2), Периоды работы регистра в режимах записи и считьгоания составляют соответственно 10 и 8 i , где Г- задержка переключения ЩП-трапзистора.

Формул;; изобретения Асинхронный последовательный регистр на Ю-ЩП-транзисторах, содержащий ячейки памяти, состоящие из двух инверторов и двух логических элементов, причем в каждой ячейке памяти, кроме первой, логические содержат четмре транзистора п-типа и четыре транзистора p-Tima, а в первой ячейке памяти логические элементы содержат три транзистора п-типа и четыре трачзистора р-типа, при этом исток, затвор и сток первого транзистора п-типа логического элемента соединены соответственно с затвором и истоком первого транзистора п-типа другого логического элемента и с истоком второго транзистора п-типа данного логического элемента, сток которого во всех ячейках памяти, кроме первой, соединен с истоком четвертого транзистора п-типа данного логического элемента, а затвор - с затвором второго транзистора р-типа данного логического элемента и во всех ячейках памяти кроме первой, - с выходом соответствующего инвертора пре- дыдуи;ей ячейки памяти, сток четверто- г о тра зистора п-типа логического

9АОА16

второго и четвертого Т1 |пчзисторов р-типа, а его затвор - с затвором первого транзистора п-типа данного J. логического элемента, сток второго транзистора р-типа которого соединен с истоком третьего транзистора р-типа, сток которого соединен с исг током первого транзистора п-типа данного логического элемента и с входом соответствующего инвертора данной ячейки памяти и во всех ячейках па10

мяти, кроме первой, - с затвором четвертого, транзистора р-типа соответствующего логического элемента предыдущей ячейки памяти, затворы четвертых транзисторов р-типа первого и второго логических элементов первой ячейки памяти соединены с выходами

соответствующих инверторов второй

ячейки памяти, затворы второго и третьего транзисторов п-типа и второго и третьего транзисторов р-типа логических элементов первой ячейки памяти и затворы третьих транзисторов п- и р-типов логических элементов второй ячейки памяти соответственно соединены, отличающийся тем, что, с целью упрощения регистра, он содержит элемент 11ЛИ-НЕ и

группу инверторов, а каждый логический элемент каждой ячейки памяти, кроме первойJ - пятый транзистор р- типа, исток и сток которого соединены

соответственно с истоком и стоком

второго транзистора р-типа, а затвор

в i-й ячейке памяти (i 2) соединен с затвором четвертого транзистора п-типа данного логического элемента

и с истоком первого транзистора п-типа соответствующего логического элемента (1-2)-й ячейки памяти, исток третьего транзистора-пгтипа логических элементов каждой ячейки памяти,

кроме первой, соединен со стоком первого транзистора п-типа данного логического элемента, стоки первого и четвертого транзисторов р-типа логического элемента соединены с истоком

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Параллельный асинхронный регистр | 1988 |

|

SU1607016A1 |

| Параллельный асинхронный регистр на КМДП-транзисторах | 1989 |

|

SU1665405A1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| Асинхронный последовательный регистр | 1986 |

|

SU1410103A1 |

| Компаратор | 1989 |

|

SU1690184A1 |

| D-триггер на КМДП-транзисторах | 1990 |

|

SU1728963A1 |

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

| Параллельный асинхронный регистр на МДП-транзисторах | 1988 |

|

SU1615807A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении асинхронных устройств приема и передачи информации. Целью изобретения является упрощение регистра. Для достижения этой цели в регистр, выполненный на КМДП-транзисторах и содержащий ячейки памяти, состоящие из двух инверторов и двух логических элементов, каждый из которых состоит из четырех транзисторов P-типа и четырех транзисторов P-типа, введены элемент ИЛИ-НЕ и группа из пяти инверторов, а в каждый логический элемент введен пятый транзистор P-типа. 4 ил.

элемента во всех ячейках памяти, кро- go первого транзистора п-типа, а сток не первой и второй, соединен со сто- его четвертого транзистора п-типа во

ком третьего транзистора п-типа, затвор которого соединен с затвором третьего транзистора р-типа данного логического элемента и выходом соответствующего инвертора данной ячейки памяти, исток первого транзистора р-типа логггческого элемента соединен с шиной питания регистра и с истоками

55

всех ячейках, кроме первой и послед-, ней, и сток второго транзистора п-типа логических элементов первой ячейки памяти соединены с вькодами соответствующих инверторов последующей ячейки памяти, причем входы первого и второго инверторов группы являются соответственно прямым и инверсным

информационными входами регистра, а их выходы соединены с затворами вторых транзисторов п-типа периого и второго логических элементои ncpDoi : ячейки памяти соотиетствеино и стоками четвертых транзисторов п-тиил иср- вого и второго логического ojiei-jeiiTOB второй ячейки памяти соответственно, вход третьего инвертора группы является управляющим входом считывания регистра, а его выкод соединен со стоками третьих транзисторов п-тшта первого и второго ло1 ичес1сих элементов последнеГ| ячейки памяти, первый и второй входы элемента 1ШИ-НЕ сое-

дииены соответственно с В1 1ходами инверторов первой ячейки памяти, а его выход является управляющим выходом записи регистра, вторые входы пятого и четвертого инверторов соединены с выходами второго и первого инверторов последней ячейки памяти соответственно, а их выходы являются )1рямым и 1ПИ ерсны1-1 ипформадионн1 1ми выходами регистра соответственно, ; входы первого и второго инверторов группы соединены с затворами пятых транзисторов р-типа первого и второго логических элементов второй ячейки памяти регистра соответственно.

8

f/

891

| Ячейка памяти для буферного регистра | 1976 |

|

SU661606A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Асинхронный последовательный регистр | 1983 |

|

SU1136216A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-07-15—Публикация

1987-01-08—Подача