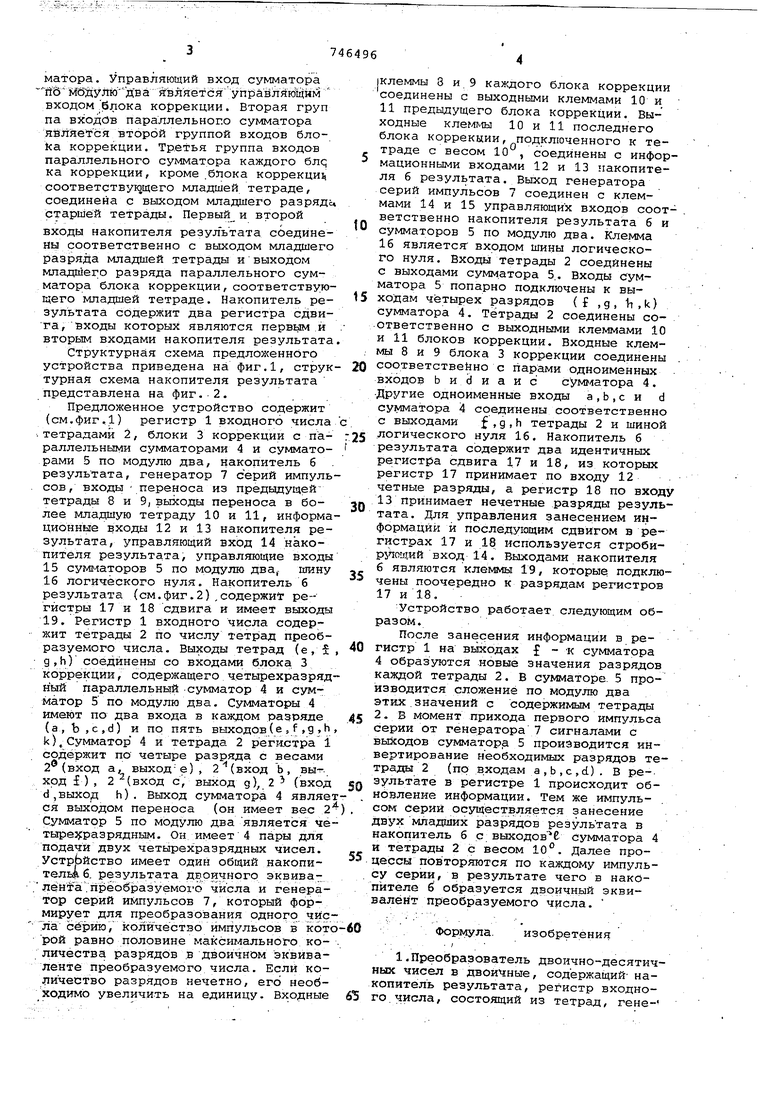

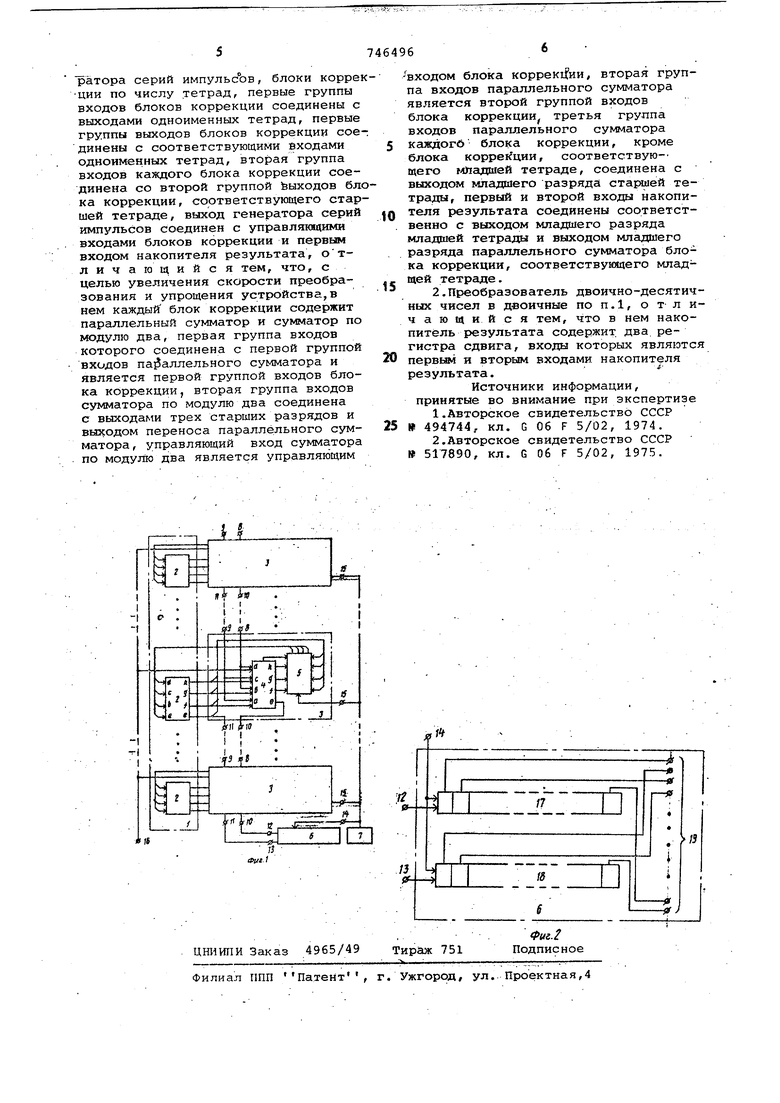

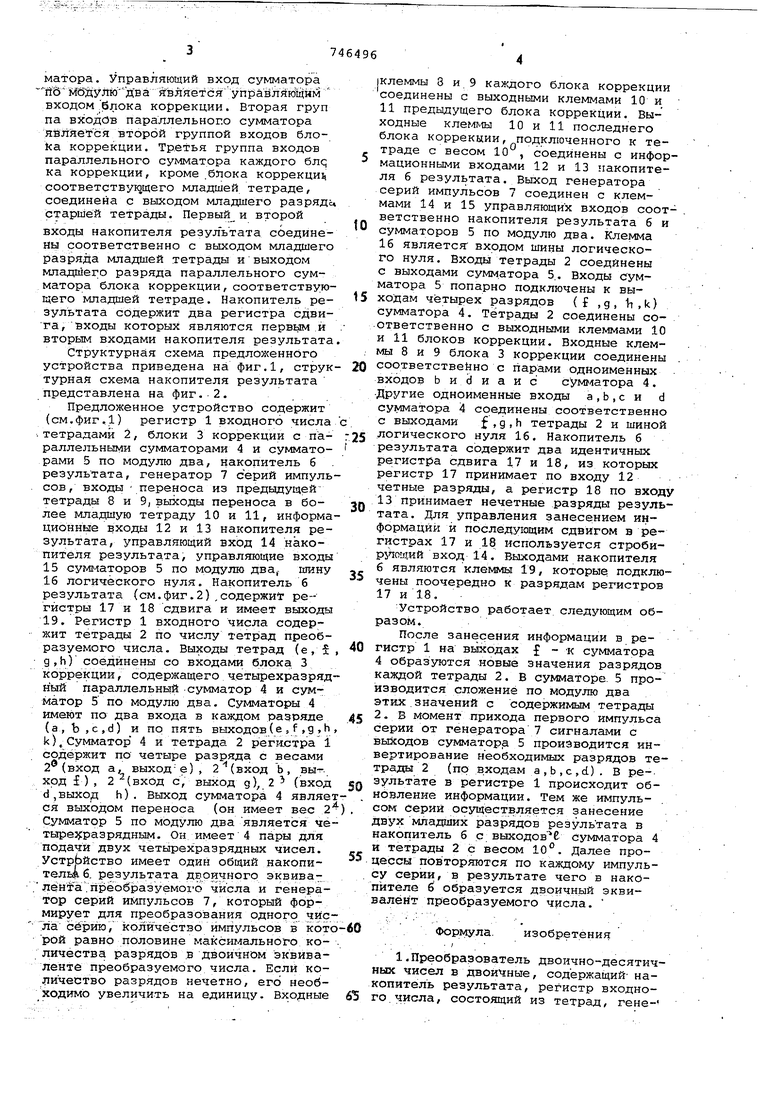

1 I Изобретение относится к области автоматики и цифровой вычислитель- . ной техники и может быть использова но при построении двоично-десятичных преобразователей в составе вычислительных машин и специальных устройс Известен преобразователь двоичнодесятичных чисел в двоичные, содержащий регистр сдвига, разделённый на тетрады, блоки коррекции, входы которых соединены с йыходами тетрад а выходы соединены со входами тетрад, регистр результата и блок управления 1 . ; Однако это устройство имеет относ тельно низкое быстродействие. Наиболее близким по технической сущности, и схемному решению к предло женному является преобразователь, содержащий накопитель результата, регистр входного числа, состоящий из тетрад, генератор серий импульсов, блоки коррекции по числу тет-. рад. Первые группы входов блоков кор рекции соединены с выходами одноимен ных тетрад. Первые группы выходов блоков коррекции соединены с соответ ствующими входами одноименных тетрад Вторая группа входов каждого блока кЬррёкШй с6ёдЙнёна сЬ группой выходов блока коррекции, соответствующего старшей тетраде. Выход генератора серий импульсов соединен с управляющймй входам блоков коррекции и первым входом накопителя результата. Кроме того известное устройство содержит блок переноса, а регистр входного числа является также сумматором 2. Однако это устройство также имеет относительно иэкое быстродействие и сравнительно большой объем аппаратуры. ; .Цель изобретения - увеличение скорости преобразования и упрощение преобразователя. Это достигается тем, что в устройстве каждый блок коррекции содержит параллельный сумматор и сумматор по модулю два, первая группа входов которого соединена с первой группой входов параллельного сумматора и является первой группой входов блр;Ка коррекции. Вторая группа входов сумматора по модулю два соединена с :выходами трех старших разрядов и выходом переноса параллельного сумматора. Управляющий вход сумматора бмбдуШдва является упра ляйгцнм входомблока коррекции. Вторая труп па входов параллельного сумматора является второй группой входов блока коррекции. Третья группа входо-в параллельного сумматора каждого блq ка коррекции, кроме .блока коррекции соответству1дщего младшей тетраде, соединена с выходом младшего разряд старшей тетрады. Первый и второй входы накопителя результата соединены соответственно с выходом младшего разряда младшей тетрады ивыходом младшего разряда параллельного сумматора блока коррекции,соответствующего младшей тетраде. Накопитель результата содержит два регистра сдвита,ВХОДЫ которых являются первым и вторым входами накопителя результата структурная схема предложенного устройства приведена на фиг.1, струк турная схема накопителя результата представлена на фиг.-2. Предложенное устройство содержит (см.фиг,1) регистр 1 входного числа .тетрадами 2, блоки 3 коррекции с параллельными сумматорами 4 и сумматорами 5 по модулю два, накопитель 6 результата, генератор 7 серий импуль сов, входы Переноса из предыдущей тетрады 8 и 9, выходы переноса в более младшую тетраду 10 и 11, информа ционные входы 12 и 13 накопителя результата, управляющий вход 14 накопителя результата, управляющие входы 15суГП 1аторов 5 по модулю два,- шину 16логического нуля. Накопитель 6 результата (см.фиг.2).содержит регистры 17 и 18 сдвига и имеет выходы 19. Регистр 1 входного числа содержит тетрады 2 по числу тетрад преобразуемого числа. Выходы тетрад (е, g , h) соединены со входами блока 3 коррекции, содержащего четырехразряд ный параллельный -сумматор 4 и сумматор 5 по модулю два. Сумматоры 4 имеют по два входа в каждом разряде (а, b,c,d) и по пять выходов(е,f,д,h k). Сумматор 4 и тетрада 2 регистра 1 содержит по четыре разряда с весами 2(вход а, выход-е), 2(вход Ъ, вы-г. ход ) , 2 (вхс5д с, выход g), 2 (вход d,выход h). Выход сумматора 4 являе ся выходом переноса (он имеет вес 2 Сумматор 5 по модулю два является че тырез разрядным. Он, имеет4 пары для подачи двух четырехразрядных чисел. УстрЬйство имеет один общий накопитель& б. резу льтата двоичного эквива, лента . прёобразуемохО числа и генератор серий И1№ульсов 7, который формирует для преобразования одного чис Ласерию, колй чество импульсов в кот рой равно половине максимального количества разрядов .в двоичном эквиваленте преобразуемого числа. Если ко:г1ичество разрядов нечетно, его необходимо увеличить на единицу. Входные |клеммы 3 и.9 каждого блока коррекции соединены с выходными клеммами 10 и 11 предыдущего блока коррекции. Выходные клеммы 10 и 11 последнего блока коррекции, подключенного к тетраде с весом 10 , соединены с информационными входами 12 и 13 накопителя 6 результата. Выход генератора серий импульсов 7 соединен с клеммами 14 и 15 управляющих входов соответственно накопителя результата 6 и сумматоров 5 по модулю два. Клемма 16является входом шины логического нуля. Входы тетрады 2 соединены с выходами сумматора 5.. Входы сумматора 5 попарно подключены к выходам четырех разрядов ( f , g , li , k} сумматора 4, Тетрады 2 соединены соответственно с выходными клеммами 10 и 11 блоков коррекции. Входные клеммы 8 и 9 блока 3 коррекции соединены соответствейно с парами одноименных входов Ь и d и а и с cyм 1aтopa 4. Другие одноименные входы а,Ь,с и d сугупугатора 4 соединены соответственно с выходами f , g , h тетрады 2 и шиной логического нуля 16, Накопитель 6 результата содержит два идентичных регистра сдвига 17 и 18, из которых регистр 17 принимает по входу 12 четные разряды, а регистр 18 по входу 13 принимает нечетные разряды результата. Для управления занесе;нием информации и последующим сдвигом в регистрах 17 и 18 используется стробир Ьощий вход 14, Выходами накопителя б являются клеммы 19, которые подключены поочередно к разрядам регистров 17и 18, Устройство работает следующим образом. После занесения информации в регистр 1 на выходах f - к сумматора 4 образ5потся новые значения разрядов каждой тетрады 2, В сумматоре. 5 производится сложение по модулю два этих значений с содержимым тетрады 2, В момент прихода первого импульса серии от генератора 7 сигналами с выходов сумматора 5 производится инвертирование необходимых разрядов тетрады 2 (по входам a,b,c,d.) . В результате в регистре 1 происходит обнЬвление информации. Тем же импульсом серий осуществляется занесение двух младших разрядов результата в накопитель 6 с выходов С сумматора 4 и тетрады 2 с весом 10°. Далее процессы повторяются по каждому импульсу серии, в результате чего в накопителе б образуется двоичный эквивалент преобразуемого числа, Формула. изобретения ... . ; 1.Преобразователь двоично-десятичных чисел в двоичные, содержащий- накопитель результата, регистр входного, числа, состоящий из тетрад, гене

Авторы

Даты

1980-07-05—Публикация

1975-11-10—Подача