Изобретение относится к вычисли- тельйой технике и может быть использовано для буферизации сообщений при обмене массивами информации между двумя электронными вычислительными машинами.

изобретения - повышение помехозащищенности устройства при обмене информацией.

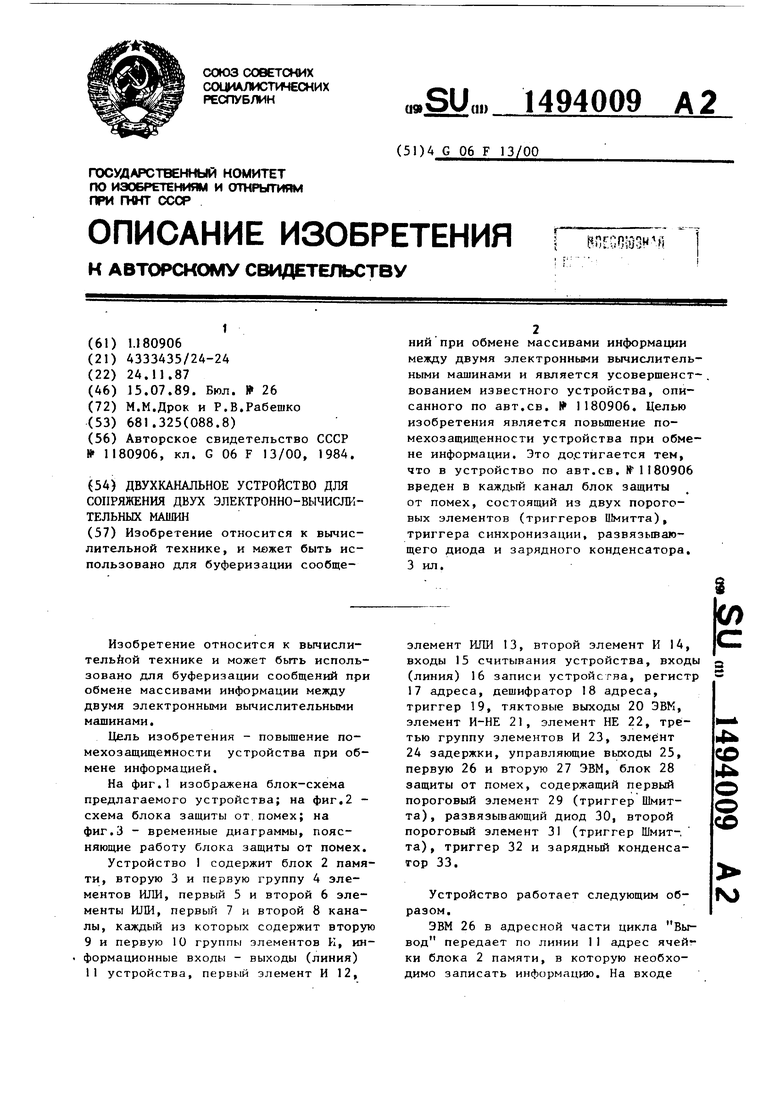

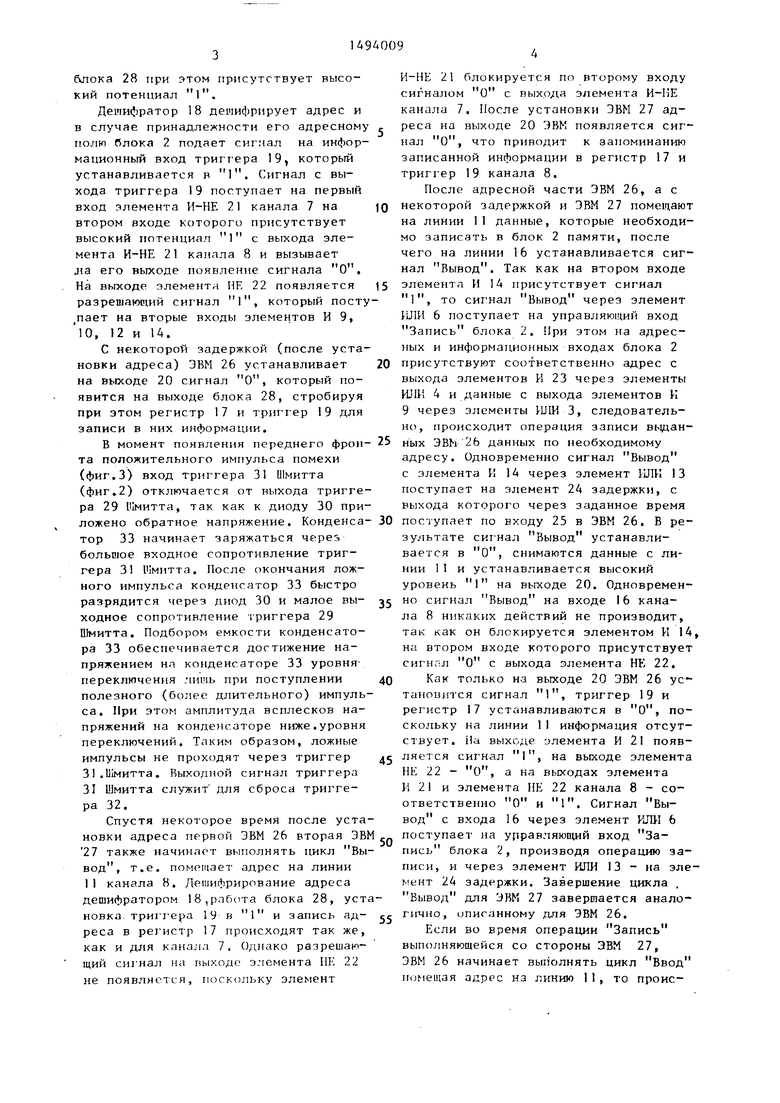

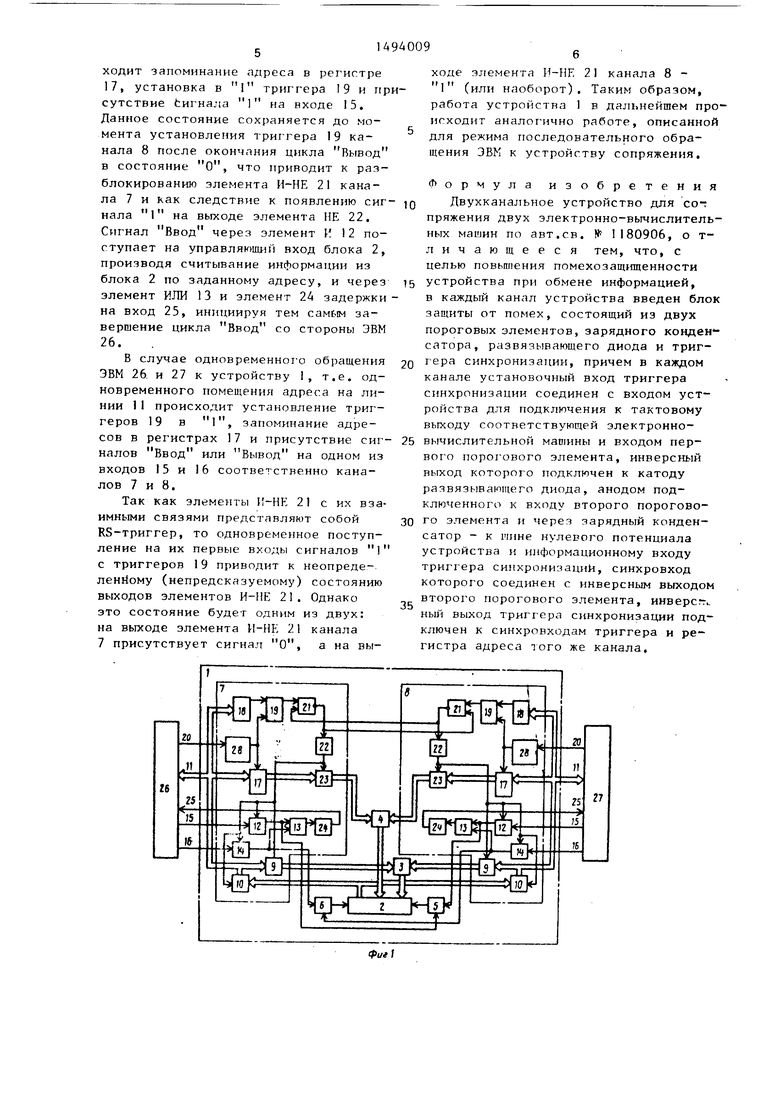

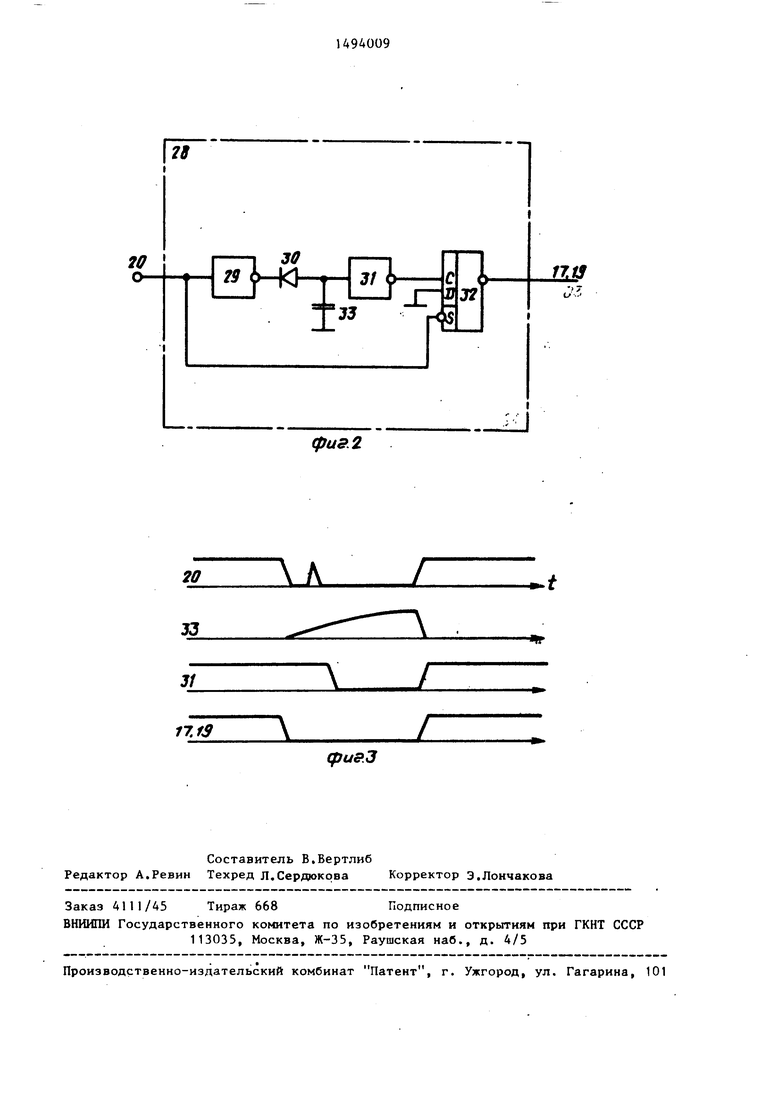

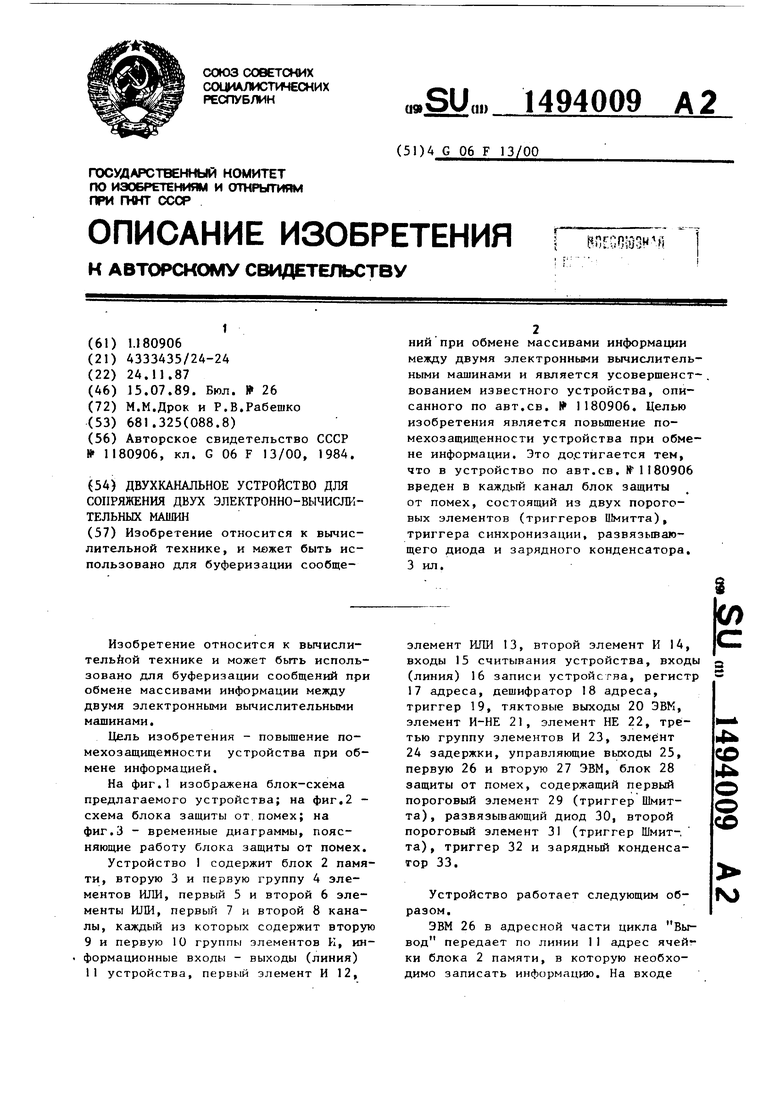

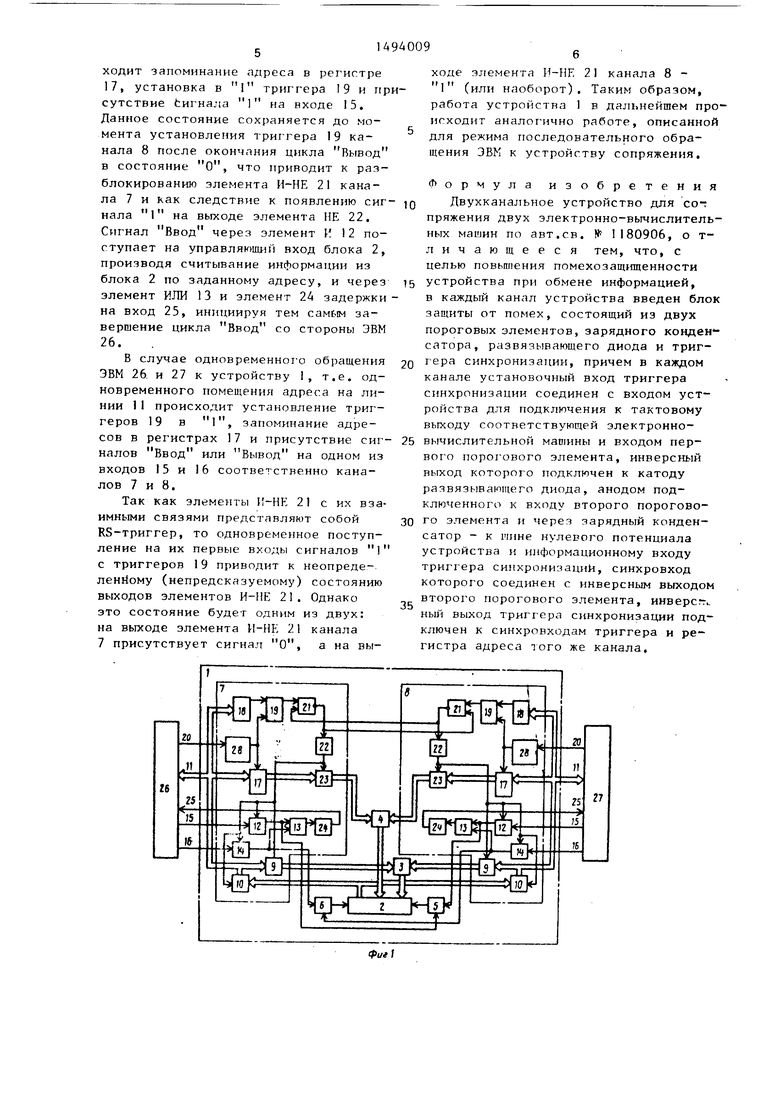

На фиг.1 изображена блок-схема предлагаемого устройства; на фиг.2 - схема блока защиты от.помех; на фиг.3 - временные диаграммы, поясняющие работу блока защиты от помех.

Устройство 1 содержит блок 2 памяти, вторую 3 и первую группу 4 элементов ИЛИ, первый 5 и второй 6 элементы ИЛИ, первый 7 и второй 8 каналы, каждый из которых содержит вторую 9 и первую 10 группы элементов К, информационные входы - выходы (линия) II устройства, первый элемент И 12,

элемент ИЛИ 13, второй элемент И 14, входы 15 считывания устройства, входы (линия) 16 записи устройства, регистр 17 адреса, дешифратор 18 адреса, триггер 19, тяктовые выходы 20 ЭВК, элемент И-НЕ 21, элемент НЕ 22, третью группу элементов И 23, 24 задержки, управляющие выходы 25, первую 26 и вторую 27 ЭВМ, блок 28 защиты от помех, содержащий первый пороговый элемент 29 (триггер Шмитта), развязывающий диод 30, второй пороговый элемент 31 (триггер Шмит-. та), триггер 32 и зарядный конденсатор 33.

Устройство работает следующим образом.

ЭВМ 26 в адресной части цикла Вывод передает по линии 11 адрес ячейг ки блока 2 памяти, в которую необходимо записать информацию. На входе

(

4

СС

N)

блока 28 при этом присутствует высокий потенциал 1.

Де1чифратор 18 дешифрирует адрес и в случае принадлежности его адресному полю блока 2 подает сигнал на информационный вход триггера 19, который устанавливается в 1. Сигнал с выхода триггера 19 поступает на первый вход элемента И-НЕ 21 канала 7 на втором входе которого присутствует высокий потенциал 1 с выхода элемента И-НЕ 21 канала 8 и вызывает ла его выходе появление сигнала О, На выходе элемента НЕ 22 появляется разрешаюр1ий сигнал 1, который пост пает на вторые входы элементов И 9, ю, 12 и 14.

С некоторой задержкой (после установки адреса) ЭВМ 26 устанавливает на выходе 20 сигнал О, который появится на выходе блока 28, стробируя при этом регистр 17 и триггер 19 для записи в них информации,

В момент появления переднего фрон та положительного импульса помехи (фиг.З) вход триггера 31 Шмитта (фиг.2) отключается от выхода триггера 29 11 митта, так как к диоду 30 приложено обратное напряжение. Конденса тор 33 начинает заряжаться чефез большое входное сопротивление триггера 31 Шмитта. После окончания ложного импульса конденсатор 33 быстро разрядится через диод 30 и малое вы- ходное сопротивление триггера 29 Шмитта. Подбором емкости конденсатора 33 обеспечивается достижение напряжением на конденсаторе 33 уровня- переключения . при поступлении полезного (более длительного) импульса. При этом амплитуда всплесков напряжений на кондеясаторе ниже,уровня переключений. Таким образом, ложные импульсы не проходят через триггер 31.Шмитта. Выходной сигнал триггера 31 Шмитта служит для сброса триггера 32.

Спустя некоторое время после установки адреса первой ЭВМ 26 вторая ЭВМ

27 также начинает выполнять цикл Вывод, т.е. помещает адрес на линии II канала 8. Дешифрирование адреса дешифратором 18,работа блока 28, установка трихтера 19 в 1 и запись ад- реса в регистр 17 происходят так же, как и для канала 7, Однако разрешающий си1 нал на выходе элемента НЕ 22 не появляется, поскольку элемент

5 0 5 0 5

0

И-НЕ 2 блокируется по второму входу сигналом О с выхода элемента И-НЕ канала 7. После установки ЭВМ 27 адреса на выходе 20 ЭВМ появляется сигнал О, что приводит к запоминанию записанной информации в регистр 17 и триггер 19 канала 8.

После адресной части ЭВМ 26, а с некоторой задержкой и ЭВМ 27 помещают на линии 11 данные, которые необходимо записать в блок 2 памяти, после чего на линии 16 устанавливается сигнал Вывод. Так как на втором входе элемента И 14 присутствует сигнал 1, то сигнал Вывод через элемент {ШИ 6 поступает на управляющий вход Запись блсжа 2. При этом на адресных и информационных входах блока 2 присутствуют соответственно адрес с выхода элементов И 23 через элементы ИЛИ 4 и данные с выхода элементов И 9 через элементы Ш1И 3, следовательно, происходит операция записи выданных 3Bh 26 данных по необходимому адресу. Одновременно сигнал Вывод с элемента И 14 через элемент ИЛИ 13 поступает на элемент 24 задержки, с выхода которого через заданное время поступает по входу 25 в ЭВМ 26. В результате сигнал Вывод устанавливается в О, снимаются данные с линии 11 и устанавливается высокий уровень 1 на выходе 20. Одновременно сигнал Вывод на входе 16 канала В HHKHKtix действий не производит, так как он блокируется элементом И 14, на втором входе которого присутствует сигнал О с выхода элемента НЕ 22.

Как только на выходе 20 ЭВМ 26 установится сигнал 1, триггер 19 и регистр 17 устанавливаются в О, поскольку на линии 11 информация отсутствует. На выходе элемента И 21 появляется сигнал 1, на выходе элемента НЕ 22 - О, а на выходах элемента И 21 и элемента НЕ 22 канала 8 - соответственно О и 1. Сигнал Вывод с входа 16 через элемент ИЛИ 6 поступает па управляюпщй вход Запись блока 2, производя операцию записи, и через элемент ИЛИ 13 - на элемент 24 задержки. Завершение цикла . Вывод для ЭВМ 27 завершается аналогично, описанному для ЭВМ 26.

Если во время операции Запись выполняющейся со стороны ЭВМ 27, ЭВМ 26 начинает выполнять цикл Ввод nohieuiaH адрес на линию II, то проис20О29

УО

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1987 |

|

SU1425692A2 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1984 |

|

SU1180906A1 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1987 |

|

SU1481780A1 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1989 |

|

SU1647581A2 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1988 |

|

SU1587523A2 |

| Устройство для сопряжения двух элект-РОННыХ ВычиСлиТЕльНыХ МАшиН | 1979 |

|

SU809147A1 |

| Устройство для сопряжения ЭВМ с микропроцессором | 1987 |

|

SU1411763A1 |

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения эвм с внешним устройством | 1988 |

|

SU1513462A1 |

Изобретение относится к вычислительной технике, может быть использовано для буферизации сообщений при обмене массивами информации между двумя электронными вычислительными машинами и является усовершенствованием известного устройства, описанного в авт.св. N 1180906. Целью изобретения является повышение помехозащищенности устройства при обмене информацией. Это достигается тем, что в устройство по авт.св. N 1180906 введен в каждый канал блок защиты от помех, состоящий из двух пороговых элементов (триггеров Шмитта), триггера синхронизации, развязывающего диода и зарядного конденсатора. 3 ил.

фиЭ.2

20

лл

(fjuff.3

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1984 |

|

SU1180906A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-15—Публикация

1987-11-24—Подача