и

Л.

0-

№

в

U

ел

СО

3149

Изобретение относится к цифровой вычислительной технике и может быть использовано в .системах передачи информации и в системах управления.

Цель изобретения - расширение функциональных возможностей путем передачи как сигналов инверсной двузначной логики, так и сигналов с тремя логическими значениями.

На фиг. 1 изображена структурная электрическая схема предложенного устройства; на фиг, 2 - структурная электрическая схема дискриминатора.

Устройство для приема и передачи информации содержит 1тервый 1 и второй 2 буферные элементы, первый 3 и второй А дискриминаторы, первый 5 и второй 6 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый 7 и второй 8 элементы ИЛИ, пер- вый 9 и второй 10 инверторы, третий 11 и четвертый 12 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ.

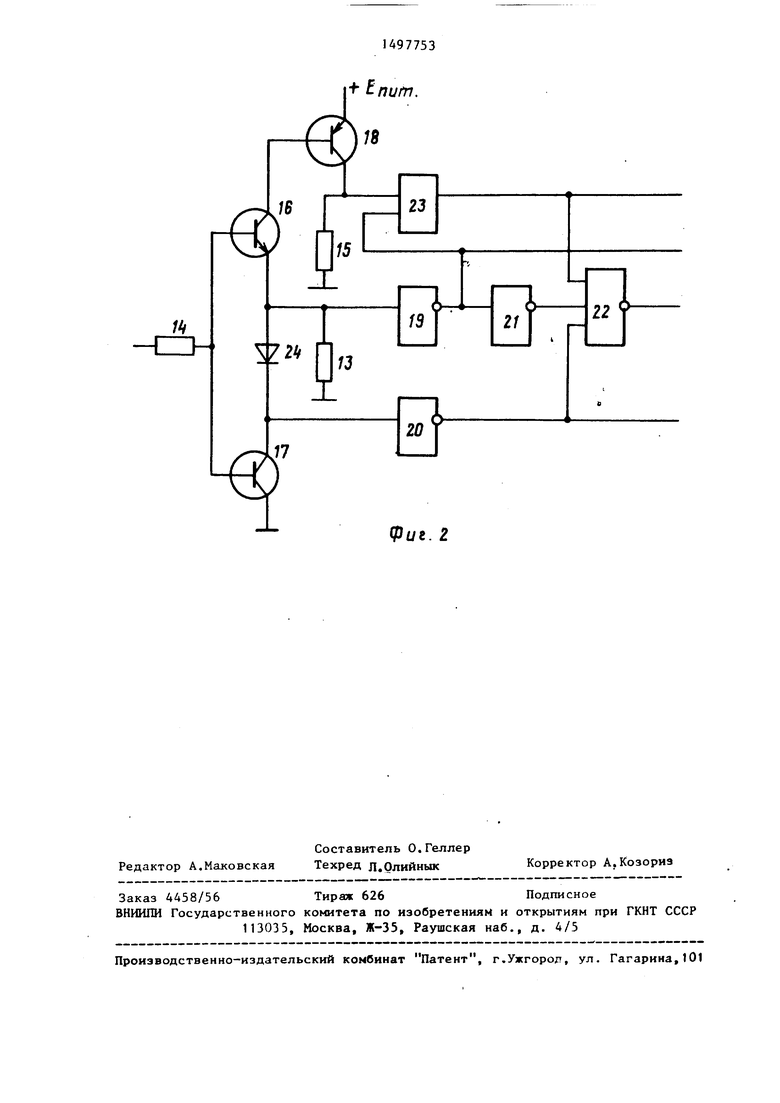

Каждый дискриминатор содержит первый 13,. второй 14 и третий 15 резисторы, первый 16, второй 17 и третий 1 транзисторы, первый 19, второй 20 и третий 21 инверторы, элемент ИЛИ-НЕ 22, элемент И 23 и диод 24.

Устройство работает следукщим об- разом.

В исходном состоянии на входах - выходах устройства присутствует третье (высокоимпедансное) состояние. На первых выходах дискриминаторов при этом формируется логическая единица, на вторых выходах дискриминаторов 3,4- логический нуль. В результате на выходах первого и второ - го элементов 5, 6 ИСКЛЮЧАЮЩЕЕ ИЛИ формируется логическая единица, ко- торая через первый 7 и второй 8 эле менты ИЛИ поступает на первые управляющие бходы второго 2 и первого 1 соответственно буферных элементов и переводит их выходы в высокоимпедансное состояние.

.1

При поступлении, например, на jiep- вый вход-выход логического сигнала (О или 1) этот же сигнал появляется на первом и втором выходах дискриминатора 3, что приводит к появлению логического нуля на вйходе первого элемента 5 ИСКЛЮЧАЮЩЕЕ ИЛИ и - через первый элемент ИЛИ 7 - на уцравляющем входе второго буферного элемента 2, который при этом отпирается и транслирует на второй вход

с

10

15 208

3540 4525

5

выход сигнал с второго выхода первого дискриминатора 3 (в прямом или инверсном виде - в зависимости от значения сигнала (1 или О) на третьем управляющем входе устройства). Одновременно логический нуль с выхода первого элемента ИЛИ 7 через инвертор 10 и элемент ИЛИ 8 поступает на управляющий вход первого буферного элемента 1, удерживая его в высокоимпедансном состоянии и разрывая таким образом нежелательную обратную связь между вторым и первым входами-выходами. После исчезновения логического сигнала с первого входа- выхода устройство возвращается в исходное состояние.

Аналогичным образом происходит передача с второго входа-выхода на первый вход-выход. Первьй и второй управляющие входы обеспечивают возможность изменения направления пере- . дачи информации. В исходном состоя- НИИ на первый и второй управляющие входы должны подаваться уровни логического О, что обеспечивает двунаправленную передачу между первым и вторым входами-выходами. При подаче на первый (или второй) управляющий вход устройства уровня логической 1 второй (или первый) буферный элемент 2 (1) переходит в высокоимпедансное состояние, и трансляция сигналов с первого входа-выхода на второй вход- выход (с второго входа-выхода на первый вход-выход) прекращается.

В качестве входного усилителя использован дискриминатор 3 (4) с высоким входным сопротивлением.

Резистор 14 осуществляет зациту дискриминатора 3 (4) от выхода из строя при случайном попадании на входы-выходы устройства больших уров-- ней напряжения и увеличивает входное сопротивление дискриминатора 3 (4). Резисторы 13, 15 задают уровни логического нуля на входах инвертора 19 и элемента И 23 при закрытых транзисторах 16 и 18, Диод 24 слутхнт для смещения уровня напряжения на величину порядка 0,7 В между эмиттерами транзисторов 16 и 17. При нулевом уровне напряжения (0-0,8 В) на выходе дискриминатора 3(4) транзисторы 16 и 18 закрыты, транзистор 17 открыт. На вход инвертора 20 передается вход- iiQB н-а-пояжение в сумме с падением

напряжения на эмиттериом переходе транзистора 17. Это суммарное напряжение соответствует для Hi BepTopa 20 уровню логического нуля, при этом на втором выходе дискриминатора 3(4) формируется логическая единица, а на четвертом выходе - логический нуль. Запирание транзистора 16 вызывает появление уровня логического нуля на выходе инвертора 19 и логической единицы - на первом выходе дискриминатора 3(4). Запирание транзистора 18 вызывает появление логического нуля на втором входе элемента К 23 и на третьем выходе дискриминатора 3(4).

При наличии на входе дискриминатора 3(4) уровня логической единицы (больше 2 В) на первом, втором и третьем выходах дискриминатора 3{4) формируются уровни логического нуля. Через инвертор 21 и элемент ИЛИ-НЕ 22 логический нуль поступает и на четвертый выход дискриминатора 3(4).

При наличии на входе дискриминатора 3(4) напряжения 1,3-1,9 В, что соответствует третьему состоянию входов-выходов устройства, на входе инвертора 20 формируется уровень логической единицы, на входе инвертора 19 - уровень логического нуля. Транзистор 18 открыт током, протекающим через открытый транзистор 16, на втором входе элементе И 23 формируется уровень логической единицы. В результате на первом и третьем выходах дискриминатора 3(4) устанавливаются уровни логической единицы, а на втором и четвертом выходах - уровни логического нуля.

Если на вход дискриминатора 3(4) не подается напряжение, что соответствует обрыву внешних цепей, подключенных к входам - выходам, из-за отсутствия базового тока заперты все три транзистора 16 - 18. На входе инвертора 19 и на втором входе элемент та И 23 формируется уровень логического нуля, а на входе инвертора 20 - уровень логической единицы. При этом на выходах инверторов 20 и 21 и элемента И 23 формируется уровень логического нуля, на первом и четвертом выходах дискриминатора 3(4) - уровни логической единицы.

Таким образом, на первом и втором выходах дискриминатора 3(4) формируются уровни, определякадие логическое значение сигнала на входе дискриминатора 3(4), а на третьем и четвертом выходах - уровни, позволяющие контролировать состояние линии, подключенной к входу дискриминатора 3(4): логическая единица на третьем выходе дискриминатора 3(4) появляется при переходе линии в третье состояние, а на четвертом выходе дискриминатора 3(4) - при отсоединении внешних связей или обрыве линии.

Использование предлагаемого устройства позволяет организовать магистрали для двунаправленной передачи данных, представленных сигналами положительной,, отрицательной логики или сигналами с тремя состояниями; преобразовывать положительную логику в отрицательную и наоборот, что особенно важно для современных систем, построенных на микропроцессорных комплектах, и, кроме того, при необходимости изменять направление передачи данных или прерывать передачу

данных, благодаря чег- можно использовать устройство в системах управления дпя изменения структуры (конфигурации) объекта управления. Наконец, использование устройства позволяет эффективно контролировать исправность каналов передачи данных и повышает надежность и ремонтопригод- , ность систем передачи данных.

35

Формула изобретения

1. Устройство для приема и передачи информации, содержащее первый и второй буферные элементы, первый

и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и первый и второй инверторы, при этом выходы первого и второго буферных элементов являются соответственно первым и вторым входами-выходами

устройства, отличающее ся тем, что, с целью расширения функциональных возможностей путем,передачи как сигналов инверсной двузначной логики, так и сигналов с тремя

логическими значениями, введены два элемента ИЛИ, третий и четвертый элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и первый и второй дискриминаторы, первые выходы которых соединены с первыми входами

соответственно первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых соединены с первыми входа1Ф1 соответственно первого и второго элементов ИЛИ, вторые входы которых

подключены к выходам соответственно первого и второго инверторов, входы которых соединены с первыми входами соответственно первого и второго буферных элементов, вторые входы которых подключены к выходам соответственно третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых подключены к вторым выходам соответственно второго и первого дискриминаторов, входы которых подключены к выходам соответственно второго и первого буферных элементов, при этом второй выход первого дискриминатора соединен с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ второй вход второго дискриминатора соединен с вторым входом второго элемента ИСКЛЮЧАЩЕЕ ИЛИ, выход вто- торого элемента ИЛИ подключен к входу fiepBoro инвертора, выход первого элемента ИЛИ соединен с входом BTq- рого инвертора, второй вход третьего элемента.ИСКЛЮЧАЮ ЦЕЕ ИЛИ подключен к второму входу четвертого элемента ИСКЛЮЧАЮПЩЕ ИЛИ и является третьим управляющим входом устройства, первым и вторым управляющими входами которого являются третьи входы соот- Ьетственно первого и второго элемен - тов ИЛИ, а третий и четвертый выходы первого дискриминатора являются соответственно первым и вторым контрольными выходами устройства, третьим и четвертым контрольными выхо- .дами которого являются соответственно третий и четвертый выходы второго дискриминатора.

2. Устройство по п. 1, о т л и - чающее ся тем, что каждый дискриминатор содержит три транзистора, три резистора, три инвертора, элемент ИЛИ-НЕ, элемент 41 и диод, анод которого соединен с входом первого инвертора, с первым выводом первого резистора и с эмиттером первого транэистора, база которого соединена с первым выводом второго ре- эит:тора и с базой второго транзистора, эмиттер которого подключен к катоду диода и к входу второго инвертора, выход которого подключен к первому входу элемента ИЛИ-НЕ, второй вход которого соединен с выходом третьего инвертора, вход которого подключен к выходу первого инвертора и к первому входу элемента И,

второй вход которого соединен с первым выводом третьего резистора и с коллектором третьего транзистора, база которого подключена к коллектоРУ первого транзистора, выход элемента И соединен с третьим входом элемента ИЛИ-НЕ, второй вывод первого резистора, второй вывод третьего резистора и коллектор второго транзистора подключены к общей шине питания, эмиттер третьего транзистора подключен к положительной шине питания, при этом второй вывод второго резистора является входом дискриминатора, первым, вторым, третьим и четвертым выходами которого являются соответственно выход первого инвертора, выход второго инвертора, выход элемента И и выход элемента ИЛИ-НЕ.

f/7(//Г7.

| название | год | авторы | номер документа |

|---|---|---|---|

| СХЕМА ЗАЩИТЫ ОТ ПЕРЕГРУЗОК ВЫХОДОВ ЦИФРОВЫХ УСТРОЙСТВ | 2023 |

|

RU2817570C1 |

| Способ поиска дефектов в цифровых блоках и устройство для его осуществления | 1985 |

|

SU1260884A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| Зонд для проверки сигналов цифровых микросхем | 1986 |

|

SU1348759A1 |

| Ждущий генератор импульсов | 1980 |

|

SU894832A1 |

| Преобразователь логического уровня | 1979 |

|

SU786006A1 |

| Зонд для проверки сигналов цифровых микросхем | 1984 |

|

SU1228055A1 |

| Логический элемент "Исключающее ИЛИ" | 2022 |

|

RU2792407C1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

Изобретение относится к вычислительной технике. Цель изобретения - расширение функциональных возможностей путем передачи как сигналов инверсной двузначной логики, так и сигналов с тремя логическими значениями. Устройство для приема и передачи информации содержит буферные эл-ты 1 и 2, эл-ты исключающие ИЛИ 5 и 6, инверторы 9 и 10. Цель достигается введением дискриминаторов 3 и 4, эл-тов ИЛИ 7 и 8 и эл-тов Исключающее ИЛИ 11 и 12, с помощью которых осуществляется передача сигналов инверсной двузначной логики и сигналов с тремя логическими значениями. Устройство по п.2 формулы отличается выполнением дискриминаторов 3 и 4. 1 з.п. ф-лы, 2 ил.

Фиг. 2

| Устройство для приема и передачи информации | 1982 |

|

SU1088145A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-07-30—Публикация

1987-11-03—Подача