вход

СП

00 00 QD 1чЭ

Изобретение относится к электро- снязи и может быть использовано для кшгтроля состояния каналов связи.

Цель изобретения - повышение точности контроля в условиях организо- 1 апных помех.

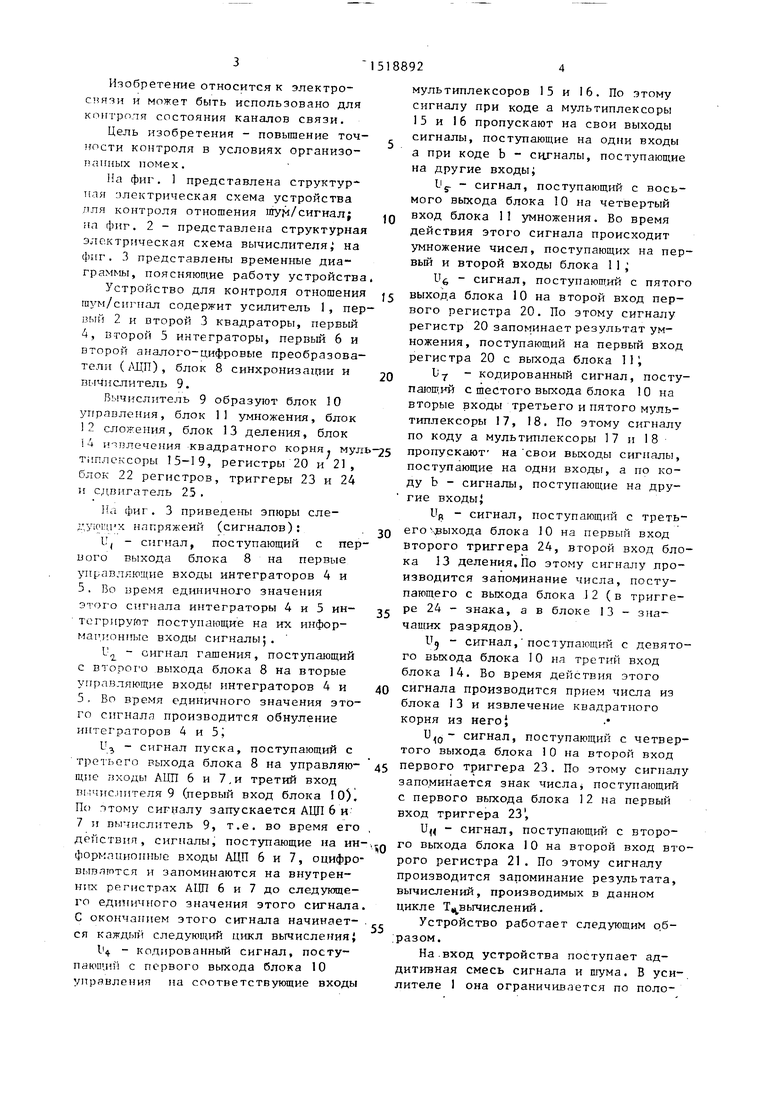

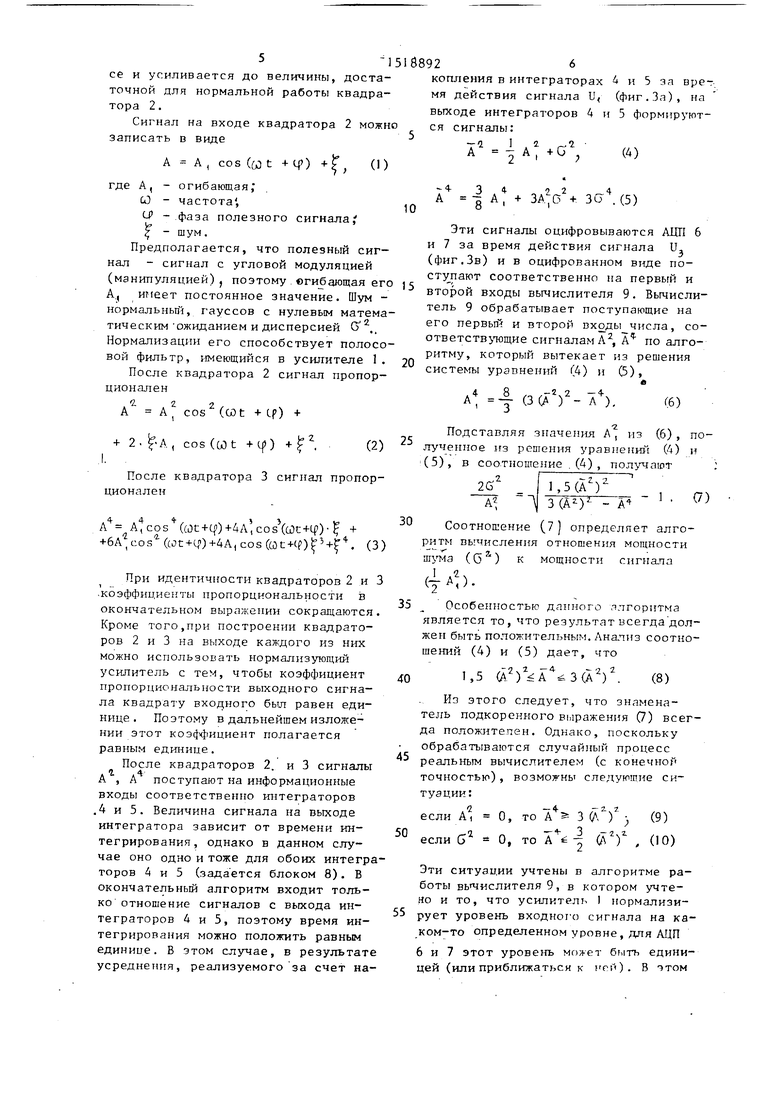

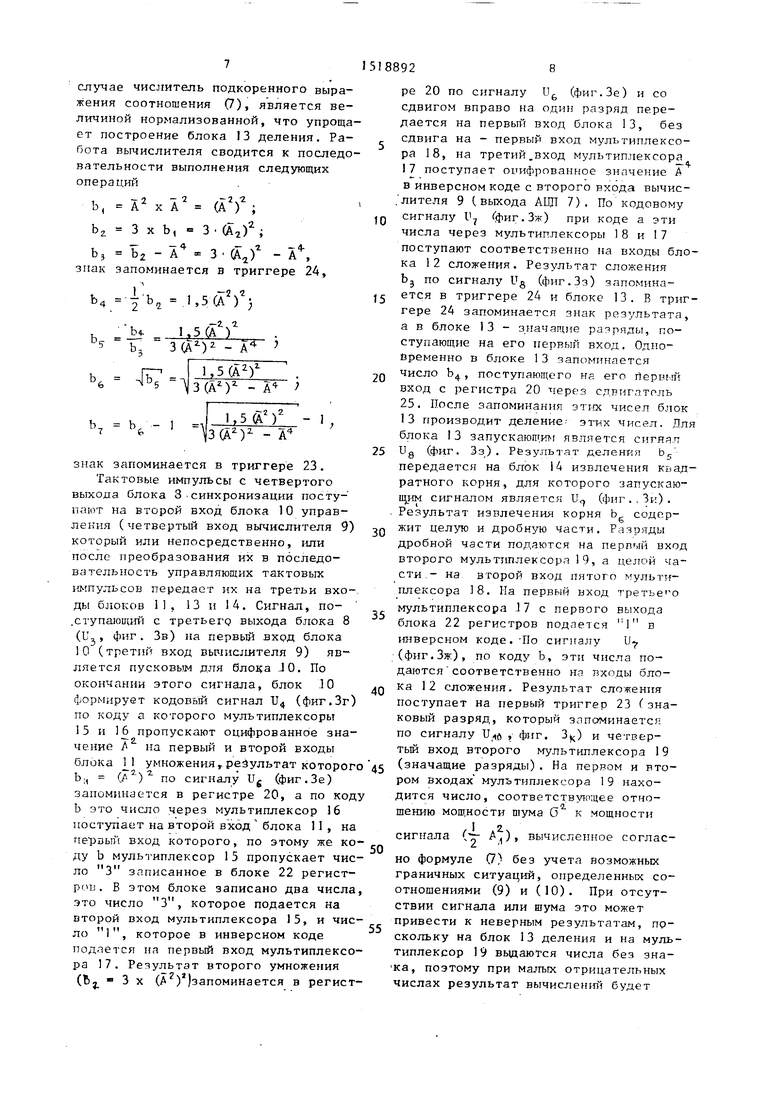

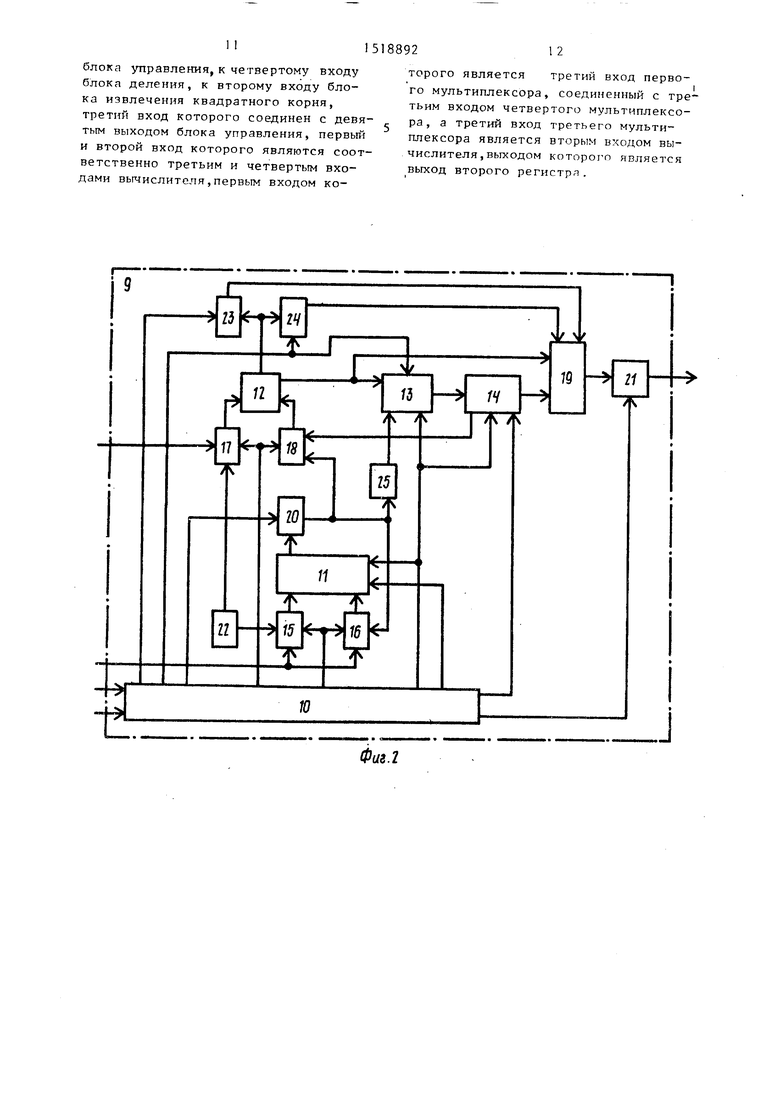

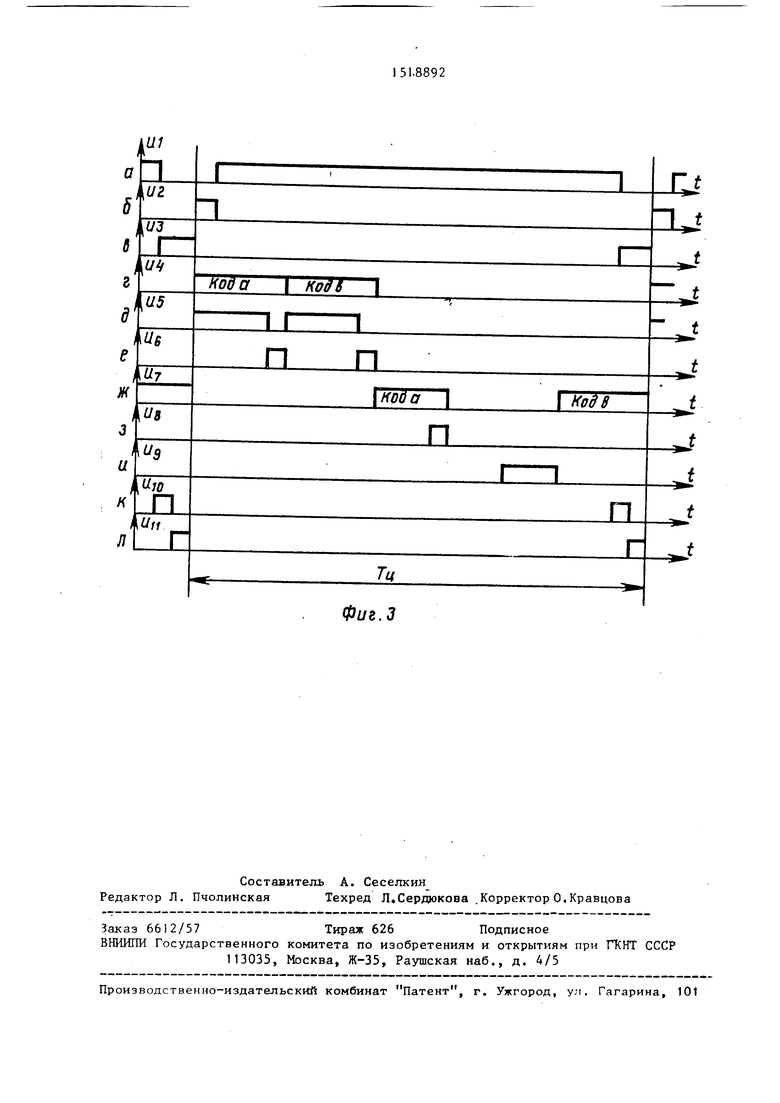

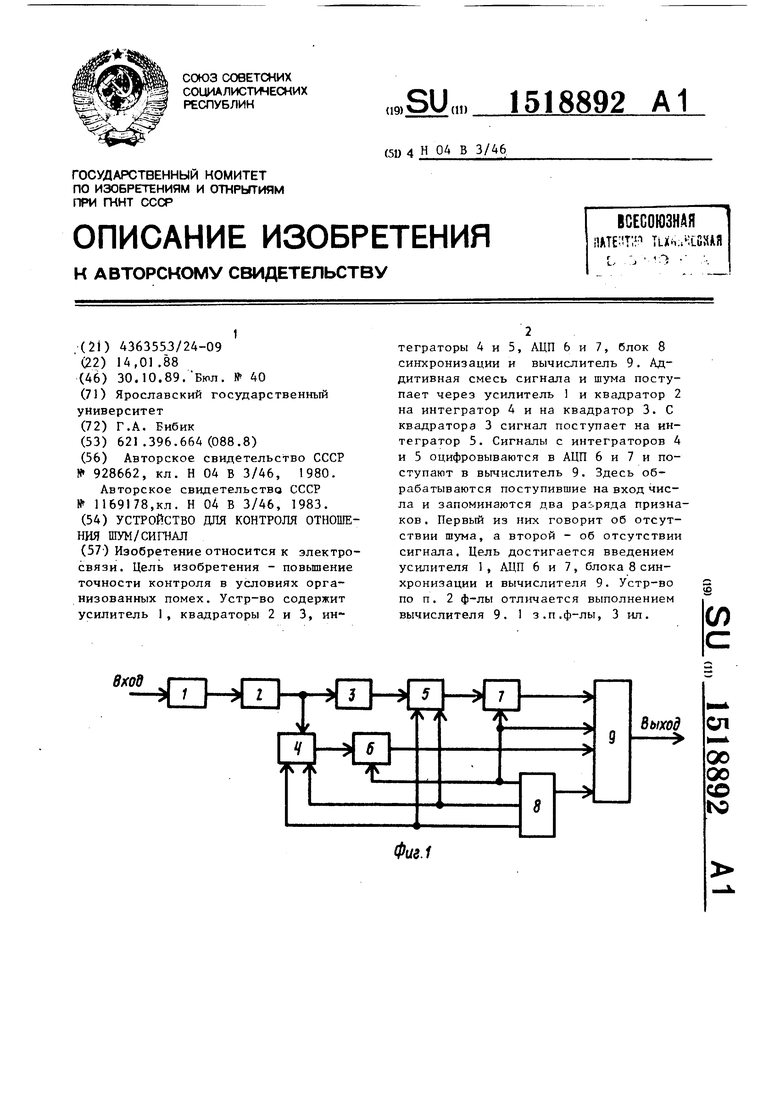

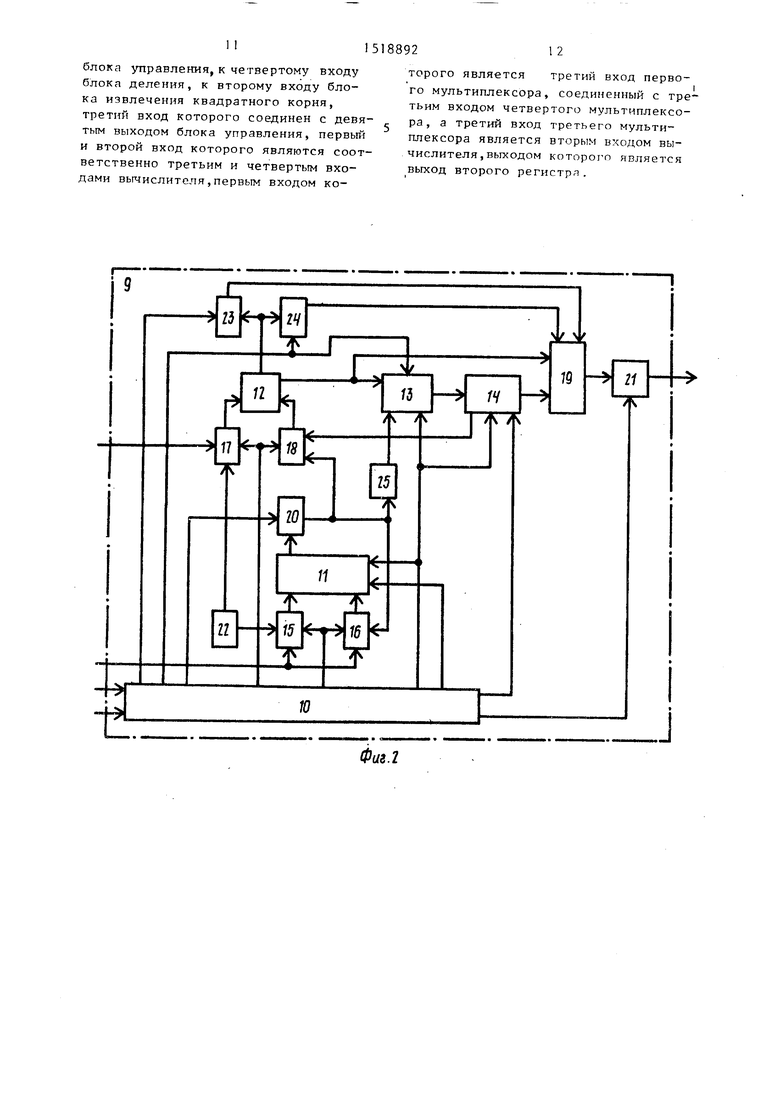

На фиг. 1 представлена структур пая электрическая схема устройства /тля контроля отношения шу} /сигнал; на фиг. 2 - представлена структурная электрическая схема вычислителяi на фиг. 3 представлены временные диаграммы, поясняющие работу устройства

Устройство для контроля отношения гаум/спгнал содержит усилитель 1, первый 2 и второй 3 квадраторы, первый

4,второй 5 интеграторы, первый 6 и второй аналого-цифровые преобразователи (ЩП) , блок В синхрониза11;ии и вычислитель 9.

Вычислитель 9 образуют блок 10 управления, блок 11 умножения, бхгок 12 сложения, блок 13 деления, блок 14 итплечения квадратного корня, мул типлсксоры 15-19, регистры 20 и 21, блок 22 регистров, триггеры 23 и 24 и сдвигагель 25.

Па фиг. 3 приведены эпюры сле- дуюиц х нлпряжеий (сигналов):

U( - сигнал, поступающий с первого выхода блока 8 на первые управляющие входы интеграторов 4 и

5.Во время единичного значения этого сигр1ала интеграторы 4 и 5 ий- тсгриругот поступающие на их инфор- магионные входы сигналы;.

и - сигнал гашения, поступающий с второг о выхода блока 8 на вторые управляющие входы интеграторов 4 и 5, Во время единичного значения этого сигнала производится обнуление интеграторов 4 и 5;

и - сигнал пуска, поступающий с третьего выхода блока 8 на управляющие входы АЦП 6 и 7,и третий вход вычислителя 9 (первый вход блока 10), По этому сигналу запускается АЦП 6 и 7 и вычислитель 9, т.е. во время его действия, сигналы, поступающие на информационные входы АЦП 6 и 7, оцифро и запоминаются на внутрен- Hitx регистрах АЦП 6 и 7 до следующего единичного значения этого сигнала С окончанием этого сигнала начинает- ся каждгзш следующий цикл вычисления}

li - кодированный сигнал, поступающий с первого выхода блока 10 управления на соответствующие входы

0

5

0

5

0

5

0

О

5

мультиплексоров 15 и 16. По этому сигналу при коде а мультиплексоры 15 и 16 пропускают на свои выходы сигналы, поступающие на одни входы а при коде b - сигналы, поступающие на другие входы;

L|J. - сигнал, поступающий с восьмого выхода блока 10 на четвертый вход блока 11 умножения. Во время действия этого сигнала происходит згмножение чисел, поступающих на первый и второй входы блока 11;

и - сигнал, поступающий с пятого выхода блока 10 на второй вход первого регистра 20. По этому сигналу регистр 20 запоминает результат умножения, поступающий на первый вход регистра 20 с выхода блока 11i

Ijf - кодированный сигнал, поступающий с шестого выхода блока 10 на вторые входы третьего и пятого мультиплексоры 17, 18, По этому сигналу по коду а мультиплексоры 17 и 18 пропускают на свои выходы сигналы, поступающие на одни входы, а по коду b - сигналы, поступающие на другие входы

Up - сигнал, поступающ1ш с третьего -зыхода блока 10 на первый вход второго триггера 24, второй вход блока 13 деления,По этому сигналу производится запоминание числа, поступающего с выхода блока 12 (в триггере 24 - знака, а в блоке 13 - значащих разрядов).

Ug - сигнал, поступающий с девятого выхода блока 10 на третий вход блока 14. Во время действия этого сигнала производится прием числа из блока I3 и извлечение квадратного корня из него}

сигнал, поступающий с четвертого выхода блока 10 на второй вход 5 первого триггера 23. По этому сигналу запоминается знак числаj поступающий с первого выхода блока 12 на первый вход триггера 23,

Uf - сигнал, поступающий с второго выхода блока 10 на второй вход второго регистра 21. По этому сигналу производится запоминание результата, вычислений, производимых в данном цикле Т вычислений.

Устройство работает следующим о.б- разом.

На.вход устройства поступает аддитивная смесь сигнала и шума. В уси-. лителе 1 она ограничивается по полосе и усиливается до величины, достаточной для нормальной работы квадратора 2.

Сигнал на входе квадратора 2 можно записать в виде

А, cos (ojt -fq ) + (1)

копления в интеграторах мя действия сигнала U,

4 и 5 за вре- (фиг .За) , на

выходе интеграторов ся сигналы:

4 и 5 формируют(А)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля качества канала связи | 1987 |

|

SU1499508A1 |

| Устройство контроля качества канала связи | 1988 |

|

SU1573543A1 |

| Устройство для контроля качества канала связи с шумоподобными сигналами | 1989 |

|

SU1628210A1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| Устройство для адаптивного скользящего сглаживания | 1986 |

|

SU1387017A1 |

| Аналого-цифровой преобразователь действующего значения напряжения | 1987 |

|

SU1585898A1 |

| Устройство для зондирования ионосферы | 1990 |

|

SU1742762A1 |

| Цифровой обнаружитель-измеритель частоты | 1986 |

|

SU1370584A2 |

Изобретение относится к электросвязи. Цель изобретения - повышение точности контроля в условиях организованных помех. Устройство содержит усилитель 1, квадраторы 2 и 3, интеграторы 4 и 5, АЦП 6 и 7, блок 8 синхронизации и вычислитель 9. Аддитивная смесь сигнала и шума поступает через усилитель 1 и квадратор 2 на интегратор 4 и на квадратор 3. С квадратора 3 сигнал поступает на интегратор 5. Сигналы с интеграторов 4 и 5 оцифровываются в АЦР 6 и 7 и поступают в вычислитель 9. Здесь обрабатываются поступившие на вход числа и запоминаются два разряда признаков. Первый из них говорит об отсутствии шума, а второй - об отсутствии сигнала. Цель - достигается введением усилителя 1, АЦП 6 и 7, блока 8 синхронизации и вычислителя 9. Устройство по п. 2 ф-лы отличается выполнением вычислителя 9. 1 з.п. ф-лы, 3 ил.

где

А,

СО J

Г А

I.

cos (Wt + Lp) + 2. -А, cos (cot +q)) +

Г(2)

огибающая;

частота ,

фаза полезного сигнала,

шум.

Предполагается, что полезный сигнал - сигнал с угловой модуляцией (манипуляцией), поэтому,огибающая ег А,, имеет постоянное значение. Шум - нормальньм, гауссов с нулевьм математическим ожиданием и дисперсией o ,, Нормализации его способствует полосовой фильтр, имеющийся в усилителе 1. После квадратора 2 сигнал пропорционален

2

После квадратора 3 ционален

сигнал пропорА A|cos (Mt+q )+4A cos cOt+4 )- + (wt+ti )+4A,cos(«t;+(p) +p. (3

При идентичности квадраторов 2 и 3 .коэффициенты пропорциональности в окончательном выражении сокращаются. Кроме того,при построении квадраторов 2 и 3 на выходе каждого из них можно использовать нормализующий усилитель с тем, чтобы коэффициент пропорциональности выходного сигнала квадрату входного был равен единице. Поэтому в дальнейшем изложении этот коз4х 1ициент полагается равным единице.

После квадраторов 2. и 3 сигналы А , А поступают на информационные входы соответственно интеграторов .4 и 5. Величина сигнала на выходе интегратора зависит от времени интегрирования, однако в данном случае оно одно и тоже для обоих интеграторов 4 и 5 (задается блоком 8). В окончательный алгоритм входит только отношение сигналов с выхода интеграторов 4 и 5, поэтому время интегрирования можно положить равным единице. В этом случае, в результате усреднетпш, реализуемого за счет на10

-4- А

(5)

Эти сигналы оцифровываются АЦП 6 и 7 за время действия сигнала U, (фиг.Зв) и в оцифрованном виде поступают соответственно на первый и второй входы вычислителя 9. Вычислитель 9 обрабатывает поступающие на его первьш и второй входы числа, со- ответств пощие сигналам А, А по алгоритму, который вытекает из решения

cиcтe ы уравнений (4) и (5),

«

А -| ()- Л). Г6)

25

Подставляя значения A , из (6) , лученное из решения уравнений (4) (5), в соотношение .(4), получают

2G

А

3 (А - А

по- и

(7)

Соотношение (7) определяет алгоритм вычисления отношения мощности шума (G ) к мощности сигнапа

(.

Особенностью данного ялгоритма является то, что результат всегда должен быть положительным. Анатиз соотношений (4) и (5) дает, что

1,5

-01. -4 -92

(А ) А 3(А ) .

(8)

Из этого следует, что знаменатель подкоренного выражения (7) всегда положителен. Однако, поскольку обрабатываются случайный процесс реальным вычислителем (с конечной точностью), возможны следующие ситуации:

0

если AI -2

О, если G - О,

то А э

3 (/,)то А (ЛЪ

(9) (10)

Эти ситуации учтены в алгоритме работы вь числителя 9, в котором учте- ко и то, что усилитель I нормализирует уровень входного сигнала на каком-то определенном уровне, для Aljn 6 и 7 этот уровень мг)жет единицей (или приближаться к игй). В этом

случае числитель подкоренного выражения соотношения (7), является величиной нормализованной, что упрощает построение блока 13 деления. Работа вычислителя сводится к последовательности выполнения следующих операций

знак запоминается в триггере 2А,

л 1 1

Ь ч 1 5 (А ) 5

Ьч. Ь.

кзслЪ

3(А) - А

ь.

ь.

l,5( . 3(А) - А-

ь. 1 -

hsrf

|3(А) - А

знак запоминается в триггере 23.

Тактовые импульсы с четвертого выхода блока 3.синхронизации поступают на второй вход блока 10 управления (четвертьй вход вычислителя 9) который или непосредственно, или после преобразования их в последователь пость управляющих тактовых импульсов передает их на третьи вхо-, ды блоков 11, 13 и 14. Сигнал, по- .ступающий с третьего выхода блока 8 (и,, фиг. Зв) на первый вход блока 10 (третий вход вьгчис;штеля 9) является пусковым для JO. По окончании этого сигнала, блок .10 формирует кодовый сигнал Б (фит.Зг) по коду а которого мультиплексоры 15 и 16 пропускают оцифрованное значение А па первый и второй входы

30

35

40

, лителя 9 (выхода АПД 7). По кодовому сигналу 1 (фиг.Зж) при коде а эти числа через мультиплексоры 18 и I 7 поступают соответственно на входы бло ка 12 сложения. Результат сложения bj по сигналу Ug (фиг.Зз) запоминается в триггере 24 и блоке 13. В триг гере 24 запоминается знак результата, а в блоке 13 - з.иачащие разряды, поступающие на его первый вход. Одновременно в блоке 13 запоминается число Ьф, поступающего на его Первьп вход с регистра 20 -через сдвигатпль 25. После запоминания эпос чисел блок 13 производит деление; эттчх чисел. Дл блока 13 запускаюпги. является сигнял Ug (фиг. Зз) . Результат деления Ь передается на блок 14 извлечения квад ратного корня, для которого запускаю- iiyiM сигналом является U (фиг . , Зи) .

. Результат извлечения корня Ь содеро

жит целую и дробную части. Разряды дробной части подаются на первый вход второго мультиплексора 19, а целой части.- на второй вход пятого мультиплексора 18. На первый вход третье о мультиплексора .17с первого выхода блока 22 регистров подается в инверсном коде. -По сигналу U (фиг.Зж), по коду Ь, эти числа подаются соответственно на входы блока 12 сложения. Результат сложения поступает на первый триггер 23 (знаковый разряд, который запоминается по сигналу иди , фиг. и четвер- тьш вход второго мультиплексора 19

блока 11 умножения J результат которого dS (значащие разряды). На первом и вто, о . ,-. .HJJ,

Ь|, ( по сигналу Ug

ром входах мультиплексора 19 находится число, соответствующее отношению мощности шума (3 к мощности

сигнала

( 2

Р.

вычисленное соглас(фиг.Зе)

запоминается в регистре 20, а по коду b это число через мультиплексор 16 поступает на второй вход блока II, на первьш вход которого, по этому же ко- ду b мультиплексор 15 пропускает чис- но формуле (7) без учета возможных ло 3 записанное в блоке 22 регист- рои. В этом блоке записано два числа, это число 3, которое подается на второй вход мультиплексора 15, и число 1, которое в инверсном коде подается на первый вход мультиплексора 17. Результат второго умножения (bj 3 X (А))запоминается в регист55

граничных ситуаций, определенных соотношениями (9) и (10). При отсутствии сигнала или шума это может привести к неверным результатам, поскольку на блок 13 деления и на мультиплексор 19 вьщаются числа без зна- ка, поэтому при малых отрицательных числах результат вычислений будет

0

5

0

5

0

ре 20 по сигналу U (фиг.Зе) и со сдвигом вправо на один разряд передается на первый вход блока 13, без сдвига на - первый вход мультиплексора 18, на третий.вход мультиплексора

-.

17 поступает оиифроваппое значение А В инверсном коде с второго входа вычис, лителя 9 (выхода АПД 7). По кодовому сигналу 1 (фиг.Зж) при коде а эти числа через мультиплексоры 18 и I 7 поступают соответственно на входы блока 12 сложения. Результат сложения bj по сигналу Ug (фиг.Зз) запоминается в триггере 24 и блоке 13. В триггере 24 запоминается знак результата, а в блоке 13 - з.иачащие разряды, поступающие на его первый вход. Одновременно в блоке 13 запоминается число Ьф, поступающего на его Первьп вход с регистра 20 -через сдвигатпль 25. После запоминания эпос чисел блок 13 производит деление; эттчх чисел. Для блока 13 запускаюпги. является сигнял Ug (фиг. Зз) . Результат деления Ь передается на блок 14 извлечения квадратного корня, для которого запускаю- iiyiM сигналом является U (фиг . , Зи) .

. Результат извлечения корня Ь содеро

жит целую и дробную части. Разряды дробной части подаются на первый вход второго мультиплексора 19, а целой части.- на второй вход пятого мультиплексора 18. На первый вход третье о мультиплексора .17с первого выхода блока 22 регистров подается в инверсном коде. -По сигналу U (фиг.Зж), по коду Ь, эти числа подаются соответственно на входы блока 12 сложения. Результат сложения поступает на первый триггер 23 (знаковый разряд, который запоминается по сигналу иди , фиг. и четвер- тьш вход второго мультиплексора 19

J,

ром входах мультиплексора 19 находится число, соответствующее отношению мощности шума (3 к мощности

но формуле (7) без учета возможных

Р.

вычисленное соглас(7) без учета возможных

но формуле (7) без учета возможных

граничных ситуаций, определенных соотношениями (9) и (10). При отсутствии сигнала или шума это может привести к неверным результатам, поскольку на блок 13 деления и на мультиплексор 19 вьщаются числа без зна- ка, поэтому при малых отрицательных числах результат вычислений будет

противоположен истинному состоянию канала, из-за представления отрицательных чисел в дополнительном коде. Для выявления этих ситуаций исполь- з тотся триггеры 23 и 24. При отсутствии сигнала выполняется соотношение

(9), в этом случае (при любом значении чисел на входах мультиплексора

19) триггер 24 заставляет мультиплексор 19 выдать во всех разрядах результата единицы, которые запоминаются в регистре 21. Кроме разрядов результата, в регистре 21 запоминаются еще два разряда признаков. Первьй из них говорит об отсутствии шума (G 0), а второй об отсутствии сигнала (А 0) При отсутствии сигнала триггер 24 заставляет мультиплексор 19 установить цервый разряд признаков в нулевое, а второй - в единичное состояния. При отсутствии шума (триггер 23 - в единичном состоянии, триггер 24 - в нулевом) мультиплексор 19 вьщает все нули в разрядах результата. Разряды признаков устанавливаются: первый в единичное, а второй - в нулевое состояние. При отсутствии осо- бенностер (оба триггера 23 и 24 - в нулевом состоянии) мультиплексор

13 пропускает результаты расчета по формуле (7) без изменения, т.е. содержание разрядов на соответствующих вход,ах мультиплексора 19 передаются

на его выход без изменения, а в разрядах признаков зацисьшаются нули.

Ф ормула изобретения

5

0

5

0

5

0

5

0

5

синхронизации, первый и второй выходы которого соединены соответственно с первым и вторым управляющими входами первого и второго интеграторов, третий выход подключен к управляющим входам первого и второго аналого-цифровых преобразователей и к третьему входу вычислителя, а четвертый выход блока синхронизации подключен к четвертому входу вычислителя.

блока управления, к четвертому входу блока деления, к второму входу блока извлечения квадратного корня, третий вход которого соединен с девятым выходом блока управления, первьш и второй вход которого являются соответственно третьим и четвертым входами вычислителя,первым входом которого является третий вход первого мультиплексора, соединенный с третьим входом четвертого мультиплексора, а третий вход третьего мультиплексора является вторым входом вычислителя, выходом KOTopoi o является выход второго регистра.

Фие.З

| Устройство для контроля амплитудно-частотных характеристик каналов связи | 1980 |

|

SU928662A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Авторское свидетельство СССР № 1169178,кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-10-30—Публикация

1988-01-14—Подача