(Л

077

ел

1Ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1986 |

|

SU1405047A1 |

| Вычислительное устройство | 1987 |

|

SU1456949A1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| Операционное устройство | 1985 |

|

SU1367012A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

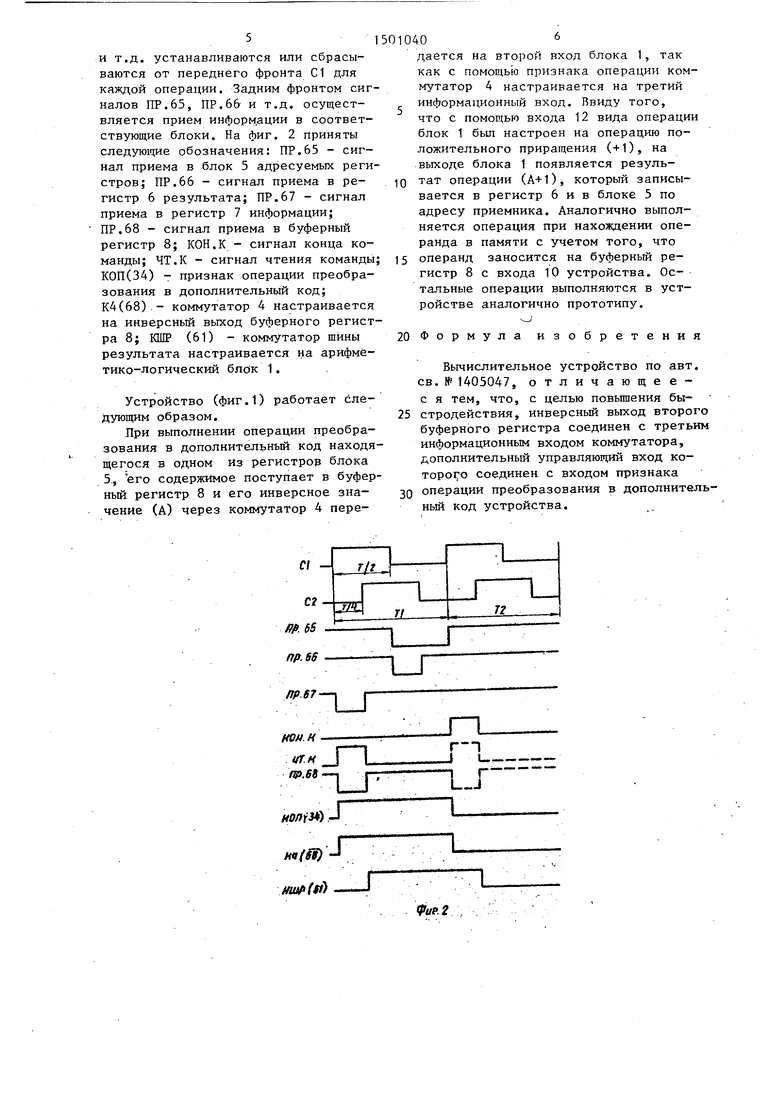

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ. ЦЕЛЬ ИЗОБРЕТЕНИЯ - ПОВЫШЕНИЕ БЫСТРОДЕЙСТВИЯ УСТРОЙСТВА. УСТРОЙСТВО СОДЕРЖИТ АРИФМЕТИКО-ЛОГИЧЕСКИЙ БЛОК 1, СДВИГАТЕЛЬ 2, КОММУТАТОР 4, ТРИ БУФЕРНЫХ РЕГИСТРА 3,8 И 9, БЛОК 5 АДРЕСУЕМЫХ РЕГИСТРОВ, РЕГИСТР 6 РЕЗУЛЬТАТА И РЕГИСТР 7 ИНФОРМАЦИИ. НОВЫМ ЯВЛЯЕТСЯ ВВЕДЕНИЕ ТРЕТЬЕГО ИНФОРМАЦИОННОГО ВХОДА И ВТОРОГО УПРАВЛЯЮЩЕГО ВХОДА КОММУТАТОРА 4, ПОЗВОЛЯЮЩИЕ ВЫПОЛНИТЬ КОМАНДУ ПРЕОБРАЗОВАНИЯ В ДОПОЛНИТЕЛЬНЫЙ КОД ЗА ОДИН МАШИННЫЙ ТАКТ. 2 ИЛ.

cpue.i

Изобретение относится к области вычислительной техники и может быть использовано в ЭВМ,

Целью изобретения является повы- шенйе быстродействия.

На фиг.1 представлена схема вычислительного устройства; на фиг.2- временная диаграмма пocтз лeния тактовых и управляющих сигналов.

Вычислительное устройство (Лиг,1) содержит арифметико-логический блок 1, сдвигатель 2, первый буферный регистр 3, коммутатор 4, блок 5 адресуемых регистров, регистр 6 резуль- тата, регистр 7 информации, второй и третий буферные регистры 8,9,первый и второй информационные входы 10,11 устройства, вход 12 задания вида операции устройства, вход 13 задания величины сдвига устройства, адресный вход 14 устройства, выход 15 блока 5,. выход 16 результата устройства, выход 17 адреса устройства, тактовые с первого по шестнадцатый входы 18-33 устройства, вход 34 признака операции.преобразования в дополнительный код устройства, причем выход арифметико-логического блока 1 объединен с выходом сдвига- теля 2 и соединен с информационным входом блока 5 адресуемых регистров, с первым -иформационным входом реги- стра 7 информации и с первым информационным входом регистра 6 резуль- тата, первый выход которого соединен с информационным входом третьего буферного регистра 9 и является вькодом 16 результата устройства, входы 12 и 13 задания вида операции и величины сдвига которого соединены соответственно с входом вида операци арифметико-логического блока 1 и входом величины сдвига сдвигателя 2, входы разрешения выдачи арифметико - логического блока 1 и сдвигателя 2 соединены соответственно с первым и вторым тактовыми входами 18 и 19 устройства, адресный вход 14 которого соединен с входом адреса блока 5 ад- ресуемых регистров, входы разрешения записи и разрешения выдачи которого содинены соответственно с третьими чет- вертым тактовыми входами 20 и 21 устрой ства,пятый тактовый вход 22 которого соединен с входом разрешения записи первого буферного регистра 3 выход ко торого является выходом 17 -адреса усройства, первый информационный вход

5

0

5 0 0 5 0 5 п

10 которого объединен с выходом 15 блока 5 адресуемых регистров, с вторым выходом регистра 6 результата, с первым выходом регистра 7 информации и соединен с информационным входом второго буферного регистра 8, выход третьего буферного регистра соединен с первьм информационным входом арифметико-логического блока 1, выход первого буферного регистра 3 соединен с первым информационным входом коммутатора 4,выход которого соединен с вторым информационным входом арифметико-логического блока 1 и с информационным входом сдвигателя 2, выход второго буферного регистра 8 соед1«1ен с информационньм входом первого буферного регистра 3 с объединенными вторыми информационными входами регистров 6 и 7 результата и информации, с вторым информационным входом коммутатора 4, первый управляющий вход которого соединен с шестым тактовым входом 23 устройства седьмой и восьмой тактовые входы 24 и 25 которого соединены соответственно с первым и вторым входами разреше- ния выдачи регистра 6 результата, второй выход и третий информационный вход регистра 7 и информации объединены и соединены с вторым информационным входом 11 устройства, входы разрешения записи и установки в нуль третьего,буферного регистра 9 соединены соответственно с девятым и десятым тактовыми входами 26 и 27 устройства, вход направления приема регистра 6 результата, первый и второй входы разрешения выдачи, регистра 7 информации, вход направления приема .регистра 7 информации, входы разреше- ния записи и установки в нуль второго буферного регистра 8 соединены соот- вественно с тактовьми входами 28-33 с одиннадцатого по шестнадцатьй устройства, вход 34 признака операции преобразования в дополнительный код которого соединен со вторым управляющим входом коммутатора 4, третий информационный вход которого соединен с инверсным выходом второго буферного регистра 8..

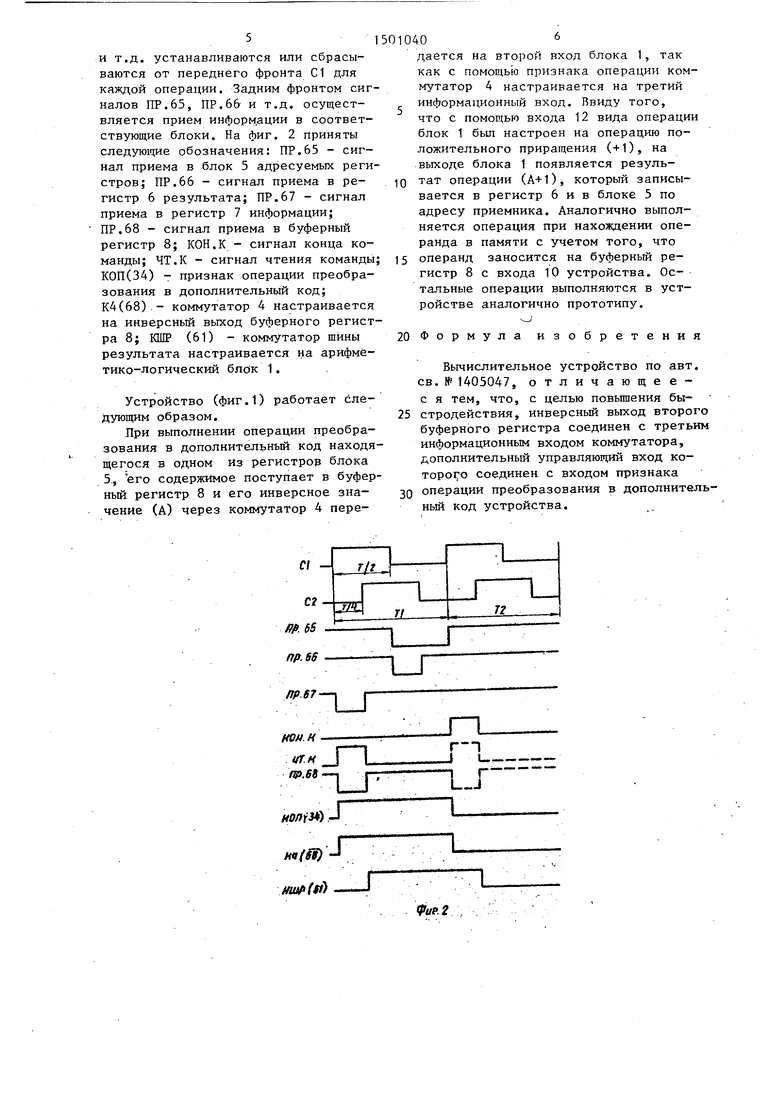

Временная диаграмма (фиг.2) поступления основных управляющих сигналов приведена в соответствии с синхросигналами С1 и С2. Например, управляющие сигналы К4(68), КОП (34)

5

и т.д. устанавливаются или сбрасываются от переднего фронта С1 для каждой операции. Задним фронтом сигналов ПР.65, ПР.6& и т.д. осуществляется прием информации в соответствующие блоки. На фиг. 2 приняты следующие обозначения: ПР.65 - сигнал приема в блок 5 адресуемых регистров; ПР.66 - сигнал приема в регистр 6 результата; ПР.67 - сигнал приема в регистр 7 информации; ПР.68 - сигнал приема в буферный регистр 8; КОН.К - сигнал конца команды; ЧТ.К - сигнал чтения команды; КОП(34) - признак операции преобразования в дополнительный код; К4(68).- коммутатор 4 настраивается на инверсный выход буферного регистра 8; КШР (61) - коммутатор шины результата настраивается на арифметико-логический блок 1.

Устройство (фиг.1) работает слеующим образом.

При выполнении операции преобразования в дополнительный код находяегося в одном Из регистров блока 5., его содержимое поступает в буферный регистр 8 и его инверсное знаение (А) через коммутатор 4 пере010406

дается на второй вход блока 1, так как с помощью признака операции коммутатор 4 настраивается на третий , информационный вход. Ввиду того,

что с помощью входа 12 вида операции блок 1 был настроен на операцию положительного приращения (+1), на выходе блока 1 появляется резуль- 10 тат операции (А+1), который записывается в регистр бив блоке 5 по адресу приемника. Аналогично выполняется операция при нахождении операнда в памяти с учетом того, что 15 операнд заносится на буферный регистр 8 с входа 10 устройства. Ос- тальные операции выполняются в устройстве аналогично прототипу.

20 Формула изобретения

Вычислительное устройство по авт. св. № 1405047, отличающее- с я тем, что, с целью повьшения бы-

25 стродействия, инверсный выход второго буферного регистра соединен с третьим информационным входом коммутатора, дополнительный управляющий вход ко- Topoi o соединен с входом признака

0 операции преобразования в дополнительный код устройства.

| Авторское свидетельство СССР jno заявке № 4090698/24-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1987-12-04—Подача