Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для считывания информации с ее последующим вводом в ЭВМ.

Цель изобретения - повышение надежности устройства.

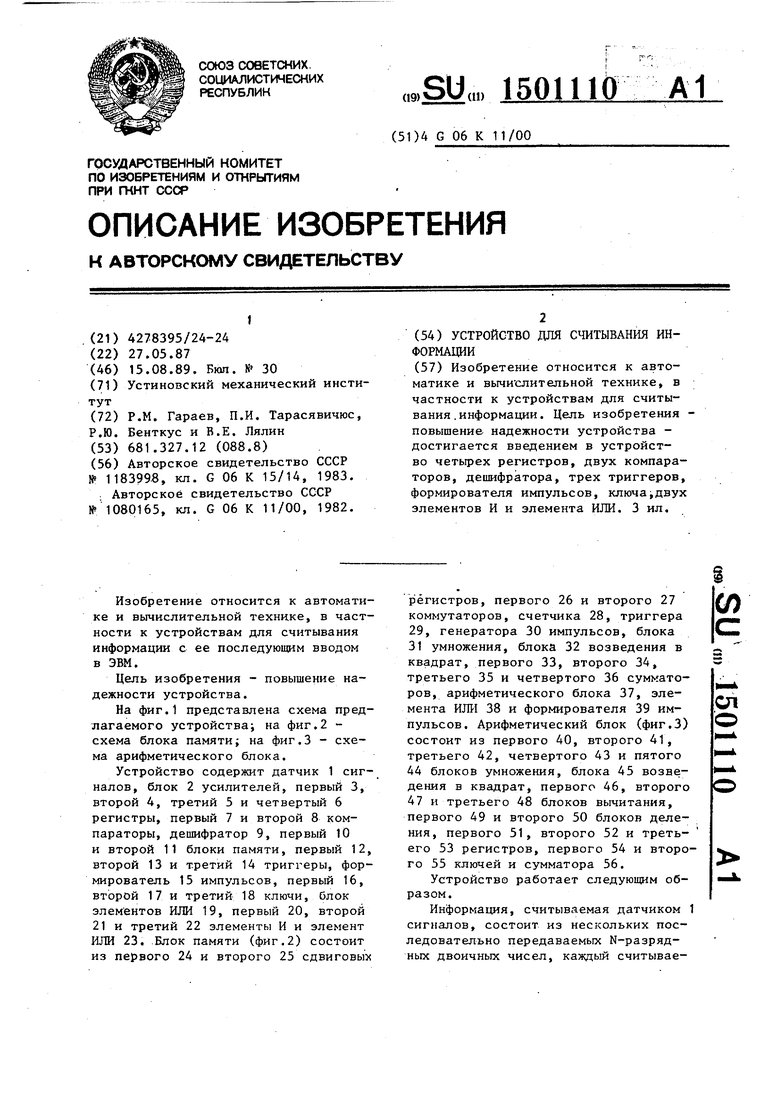

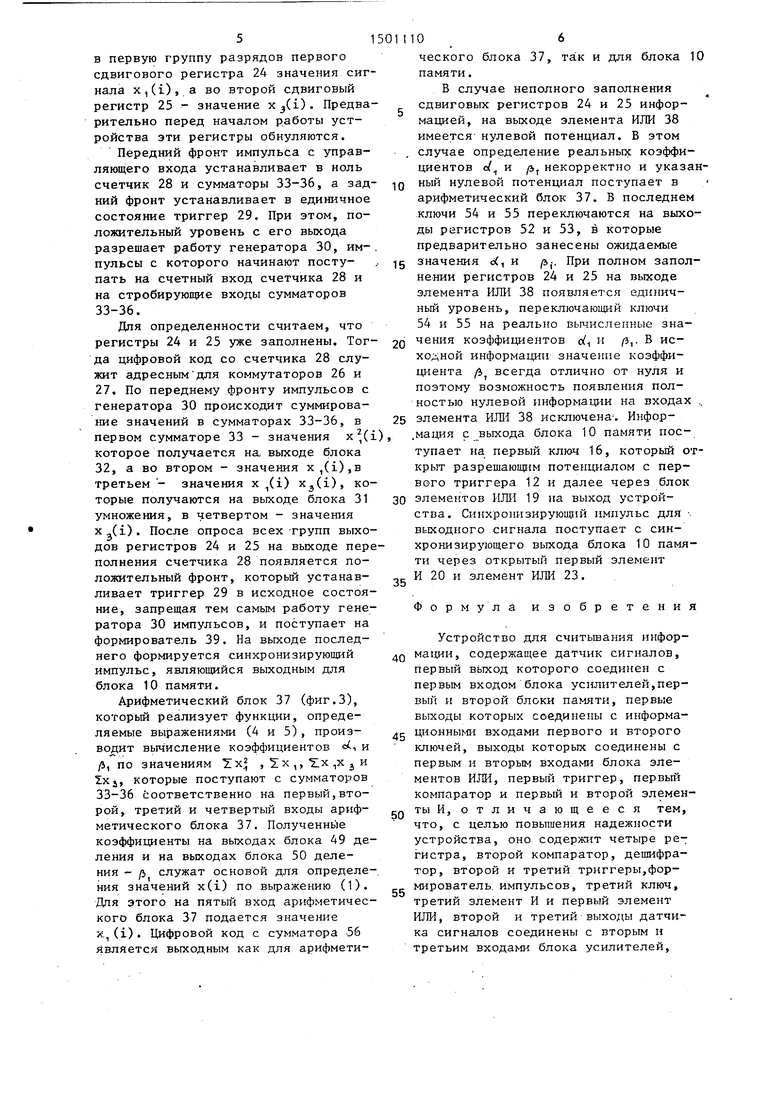

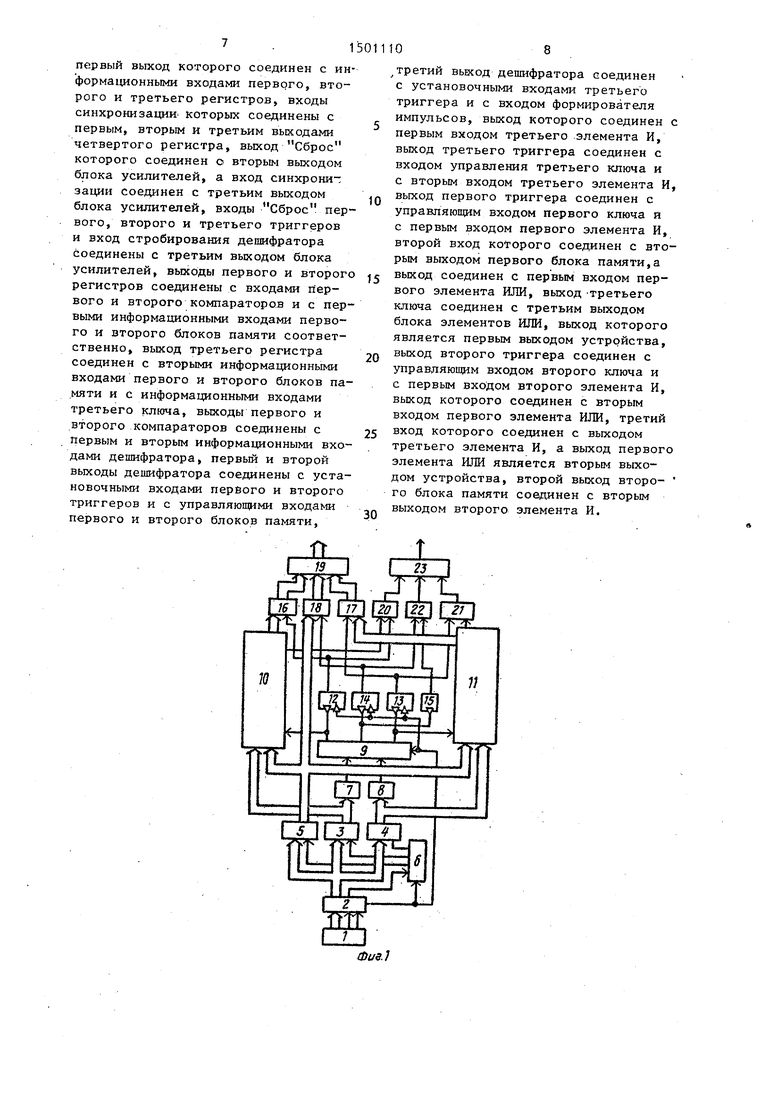

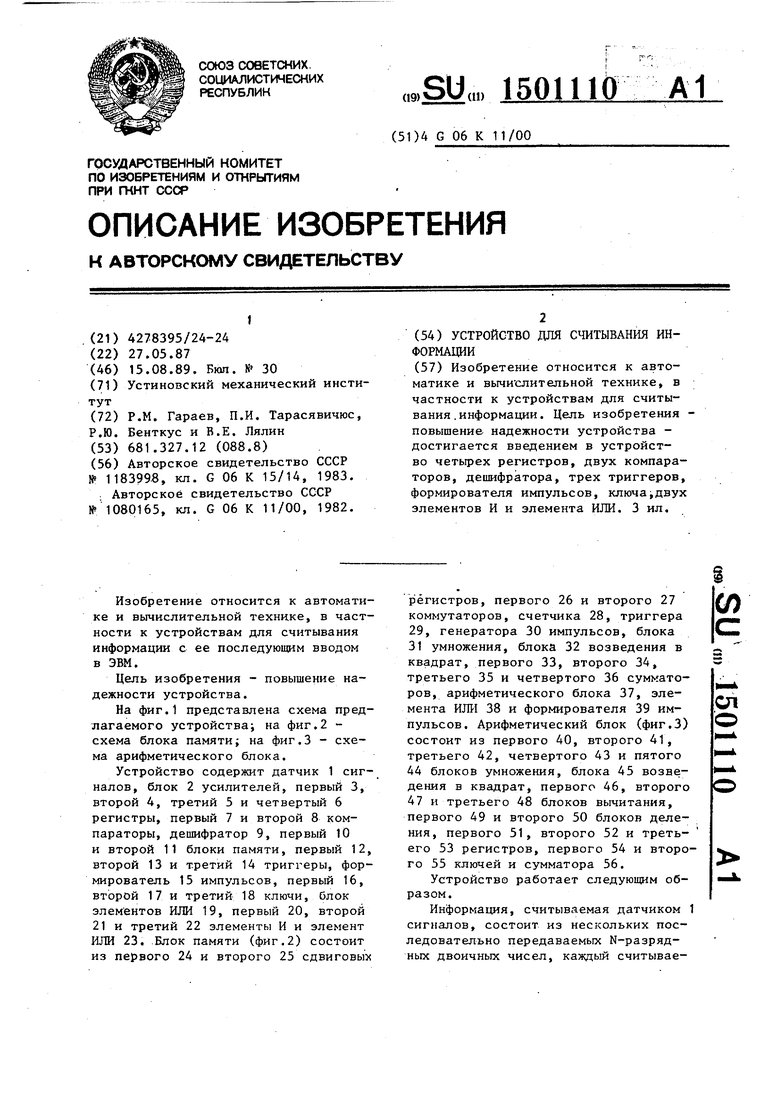

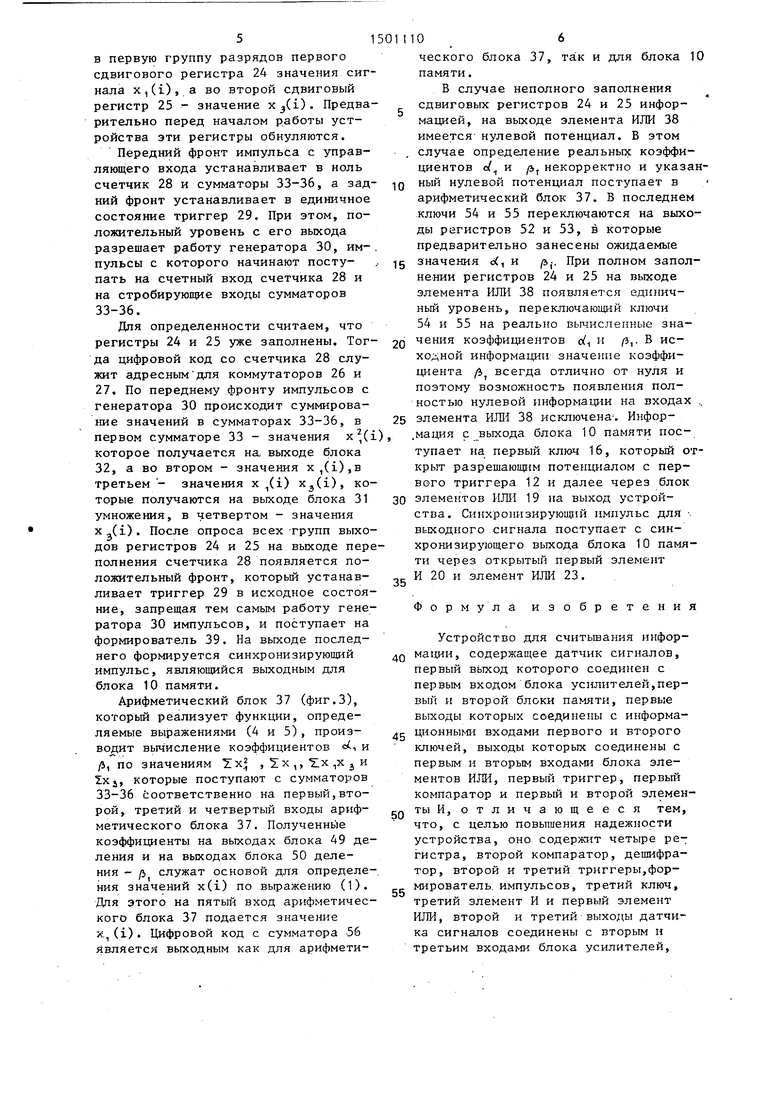

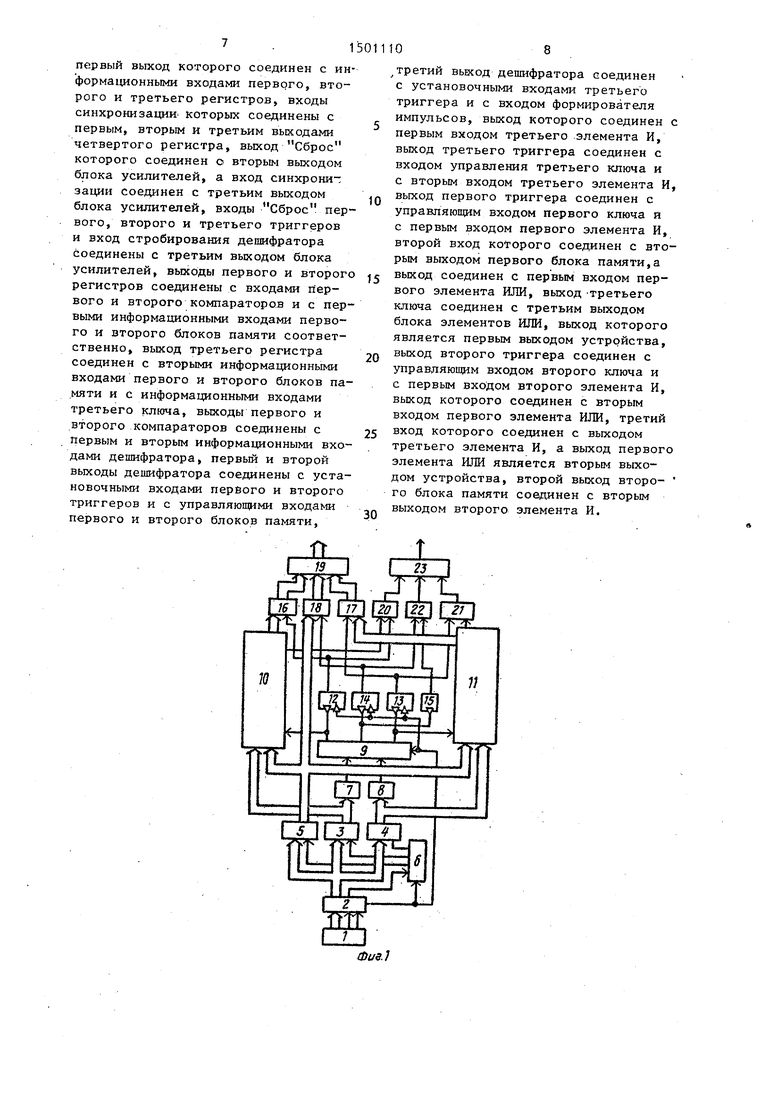

На фиг.1 представлена схема предлагаемого устройства; на фиг.2 - схема блока памяти; на фиг.З - схема арифметического блока.

Устройство содержит датчик 1 сигналов, блок 2 усилителей, первый 3, второй 4, третий 5 и четвертый 6 регистры, первый 7 и второй 8 компараторы, дешифратор 9, первый 10 и второй 11 блоки памяти, первый 12, второй 13 и третий 14 триггеры, формирователь 15 импульсов, первый 16, второй 17 и третий 18 ключи, блок элементов ИЛИ 19, первый 20, второй 21 и третий 22 элементы И и элемент ИЛИ 23. -Блок памяти (фиг.2) состоит из первого 24 и второго 25 сдвиговых

регистров, первого 26 и второго 27 коммутаторов, счетчика 28, триггера 29, генератора 30 импульсов, блока 31 умножения, блока 32 возведения в квадрат, первого 33, второго 34, третьего 35 и четвертого 36 сумматоров, арифметического блока 37, элемента ИЛИ 38 и формирователя 39 импульсов. Арифметический блок (фиг.З) состоит из первого 40, второго 41, третьего 42, четвертого 43 и пятого 44 блоков умножения, блока 45 возведения в квадрат, первого 46, второго 47 и третьего 48 блоков вычитания, первого 49 и второго 50 блоков деления, первого 51, второго 52 и треть- его 53 регистров, первого 54 и второго 55 ключей и сумматора 56.

Устройство работает следующим образом.

Информация, считываемая датчиком 1 сигналов, состоит из нескольких последовательно передаваемых N-разряд- ных двоичных чисел, каждый считывае л

с

ел

. 150

мый код с:опровож.и1(ссл пмпу.ньсом по первому синхронизирующему выходу датчика 1 , Латчик 1 сигналов передает в одном кадре информацию об одном исследуемом процессе тремя аналого-цифровыми представлениями с различиьми коэффициентами усиления, что повышает динамический диапазон передаваемой информации при жестко заданной ее разрядности. После установки четвертого регистра 6 в исходное состояние импульсом с второго синхронизирующего выхода датчика 1 происходит последовательный сдвиг единичного потенциала на выходах регистра 6 по первым синхронизирующим импульсам с датчика 1. Полученные импульсы на выходах четвертого сдвигового регистра 6 являются исинхронизирую- шими для первого 3, второго 4 и третьего 5 регистров. В первый регистр 3 принимается информация о максимально усиленном представлении процесса (коэффициент усиления - с/), гзо второй регистр 5 - с меньшим коэффициентом усиления d ,а в тре- ;Тий регистр 6 - информация о процессе без усиления. Из-за неидеальности характеристик этих усилителей отношение цифровых кодов усиленных сигналов об исследуемом процессе к концу неусиленного сигнала будет отличаться от предварительно заданнькс/. Кроме того, появляется постоянный амплитудный сдвиг i и /5 Если

О 4

значения сигналов в неусиленном канале, усиленном в ci -R максимально усиленном в d раз, обозначим соответственно x.(i), x(i) и x,(i), то Искомое значение сигнала об ис- следуемом процессе обозначим x(i), i - 1,М, которое необходимо ввести в ЭВМ, в случае, если x(i) не це- реполнено, принимается равным

x(i) у5,+ о/, хД),

если x,(i) переполнено, а x,2(i) - нет, то

x(i) /3.jb d(..

Если же х(i) и ) переполнены,то x(i) Xj(i)

Коэффициенты , ,с,, /5 и cL определяются методом наименьших квадратов по последним п переполненным значениям сигналов х х . х минимизируя выражение

X(Xj(i-j) - (,-t-c,x(i-j))) У Г

30

Z(x.j(i-j) - (/J,+ c,(x /i-j)))2.

Минимум первого из них достигается на значениях

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| Устройство для выделения признаков изображений | 1988 |

|

SU1553997A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

Изобретение относится к автоматике и вычислительной технике , в частности, к устройствам для считывания информации. Цель изобретения - повышение надежности - достигается введением в устройство четырех регистров, двух компараторов, дешифратора, трех триггеров, формирователя импульсов, ключа, двух элементов И и элемента ИЛИ. 3 ил.

с/,

Х,(

hп

i-j) x,(i-j) - п ,, x,(i-j) х, (i-j) ,

С 1 x,(i-j))2 - п i: (x,(i-j))2

J 1/- 1

hи

. .) - о(, г. x/i-j)

п

Аналогичные выражения и для коэффициентов d. р,.

Таким образом, в первом регистре 3 будет значение x(i), а во втором регистре 4 - х (i), а в третьем XjCi).

Компараторы 7 и 8 определяют наличие переполнения информации.в первом регистре 3 и во втором регистре 4. В случае переполнения на их выходах появляется сигнал.. В случае, если не переполнено, импульс

с второго выхода датчика 1 через стробирующий вход дешифратора 9 проходит на первый выход дешифратора 9. Этот импульс поступает на управляющий вход первого блока 10 памяти и задним фронтом установит в единичное состояние первый триггер 12.

Блоки 10 и 11 памяти (фиг.2) работают следующим образом. По переднему фронту импульса на управляющем входе происходит одновременный, сдвиг параллельных разрядов и запись

5

в первую группу разрядов первого сдвигового регистра 24 значения сигнала x,(i), а во второй сдвиговый регистр 25 значение ). Предварительно перед началом работы устройства эти регистры обнуляются.

Передний фронт импульса с управляющего входа устанавливает в ноль счетчик 28 и сумматоры 33-36, а зад НИИ фронт устанавливает в единичное состояние триггер 29. При этом, положительный уровень с его выхода разрешает работу генератора 30, импульсы с которого начинают посту- пать на счетный вход счетчика 28 и на стробирующие входы сумматоров 33-36.

Для определенности считаем, что регистры 24 и 25 уже заполнены. Тог да цифровой код со счетчика 28 служит адресным для коммутаторов 26 и 27. По переднему фронту импульсов с генератора 30 происходит суммирование значений в сумматорах 33-36, в первом сумматоре 33 - значения x(i которое получается на выходе блока 32, а во втором - значения х,(1),в третьем - значения х (i) x(i), которые получаются на выходе блока 31 умножения, в четвертом - значения Xjd). После опроса всех трупп выходов регистров 24 и 25 на выходе переполнения счетчика 28 появляется положительный фронт, который устанав- ливает триггер 29 в исходное состояние, запрещая тем самым работу генератора 30 импульсов, и поступает на формирователь 39. На выходе последнего формируется синхронизирующий импульс, являющийся выходным для блока 10 памяти.

Арифметический блок 37 (фиг.З), который реализует функции, определяемые выражениями (4 и 5), произ- водит вычисление коэффициентов т и /1, по значениям Тх , 2х ,, Тх х и Ixj, которые поступают с сумматоров 33-36 Соответственно на первый,второй, третий и четвертый входы ариф- метического блока 37. Полученное коэффихщенты на выходах блока 49 деления и на выходах блока 50 деления - /J служат основой для определеНИН значений x(i) по вьгражению (1). Для этого на пятый вход арифметического блока 37 подается значение X,(i). Цифровой код с сумматора 56 является выходным как для арифмети106

ческого блока 37, та1к и для блока памяти.

В случае неполного заполнения сдвиговых регистров 24 и 25 информацией, на выходе элемента ИЛИ 38 имеется нулевой потенциал. В этом случае определение реальных коэффициентов о и /ъ некорректно и указный нулевой потенщ1ал поступает в арифметический блок 37. В последне ключи 54 и 55 переключаются на выхды регистров 52 и 53, в которые предварительно занесены ожидаемые значения о, и р,-. При полном запонении регистров 24 и 25 на выходе элемента ИЛИ 38 появляется единичный уровень, переключающий ключи 54 и 55 на реально вычисленные значения коэффициентов с, и ,. В исходной информации значение коэффициента ft всегда отлично от нуля и поэтому возможность появления полностью нулевой информации на входах элемента ИШ 38 исключена-. Инфор- .ма1Д1я с выхода блока 10 памяти поступает на первый ключ 16, который окрыт разрешающим потенциалом с первого триггера 12 и далее через блок элементов ИЛИ 19 на выход устройства. Синхронизирующий импульс для выходного сигнала поступает с синхронизирующего выхода блока 10 памяти через открытый первый элемент И 20 и элемент ИЛИ 23.

Формула изобретени

Устройство для считьшания инфор- матдаи, содержащее датчик сигналов, первый вьгход которого соединен с первым входом блока усилителей,первый и второй блоки памяти, первые выходы которых соединены с информационными входами первого и второго ключей, выходы которых соединены с первым и вторым входам блока элементов ИЛИ, первый триггер, первьш компаратор и первый и второй элементы И, отличающееся тем, что, с целью повышения надежности устройства, оно содержит четыре регистра, второй компаратор, дешифратор, второй и третий триггеры,фор- М1 рователь. импульсов, третий ключ, третий элемент И и первый элемент И1Ш, второй и третийвыходы датчика сигналов соединены с вторым и третьим входами блока усилителей.

первый выход которого соединен с информационными входами первого, второго и третьего регистров, входы синхронизации которых соединены с первым, вторым и третьим выходами четвертого регистра, выход Сброс которого соединен о вторым выходом блока усилителей, а вход синхронизации соединен с третьим выходом блока усилителей, входы Сброс первого, второго и третьего триггеров и вход стробирования дешифратора соединены с третьим выходом блока усилителей, выходы первого и второго регистров соединены с входами п ер- вого и второго компараторов и с первыми информационными входами первого и второго блоков памяти соответственно, выход третьего регистра соединен с вторыми информационнь1ми входами первого и второго блоков па- .мяти и с информационными входами третьего ключа, выходы первого и второго компараторов соединены с первым и вторым информационными входами дешифратора, первьй и второй выходы дешифратора соединены с установочными входами первого и второго триггеров и с управляющими входами первого и второго блоков памяти,

третий вьЕход дешифратора соединен с установочными входами третьего триггера и с входом формирователя импульсов, выход которого соединен с первым входом третьего элемента И, выход третьего триггера соединен с входом управления третьего ключа и с вторым входом третьего элемента И, выход первого триггера соединен с управляющим входом первого ключа и с первым входом первого элемента И, второй вход которого соединен с вторым выходом первого блока памяти,а выход соединен с первым входом первого элемента ИЛИ, выход третьего ключа соединен с третьим выходом блока элементов ИЛИ, выход которого является первым выходом устройства, выход второго триггера соединен с управляюш:им входом второго ключа и с первым входом второго элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, третий вход которого соединен с выходом третьего элемента И, а выход первого элемента ИЛИ является вторым выходом устройства, второй выход второ- го блока памяти соединен с вторым выходом второго элемента И.

Редактор Ю. Середа

Фие.З

Составитель А. Глотов

Корректор М. Васильева

Техред М.Дидык

Заказ 4873/48

Тираж 668

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

тг

фиг. 2

Подписное

| Дозирующее устройство | 1958 |

|

SU118399A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для считывания информации | 1982 |

|

SU1080165A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1987-05-27—Подача