(Л

ел

о

О)

1

00

щенности устройства для измерения -. временных интервалов и расширение функциональных возможностей. Устройство содержит элементы И-НЕ триггеры 2,-2„, элемент ИЛИ-НЕ 3, блокировки, элемент И А запуска, элементы И 5,-5, триггер 6 пуска, элемент И-НЕ 7 пуска, формирователь 8 микрокоманд, элемент ИЛИ-НЕ 9 останова, элемент И-НЕ 10 пуска частоты, триггер 11 подключения частоты, элемент И 12 блокировки частоты, счетчик 13 импульсов, запоминанидий блок, состоящий из регистров .,, первый коммутатор 15, второй коммутатор 16, элементы ИЛИ-НЕ 17,-17„, входы 18i-18n запускающих импульсов устройства, вход 19 коммутации частоты

и регистров устройства, входы 20,-20„ частот устройства, вход 21 сброса устройства, выход 22 устройства. Формирователь 8 микрокоманд содержит четыре D-триггера, элемент И и элемент ИЛИ-НЕ. В предложенном устройстве по сравнению с прототипом помехозащищенность при наличии помех в линиях связи с внешними датчиками выше за счет последовательного разрешения триггерами 2,-2 приема запускающих импульсов через элементы И-НЕ Введение второго коммутатора расширяет функциональные возможности устройства за счет измерения временных интервалов для объектов с широким диапазоном скоростей движения. 1 з.п. ф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1986 |

|

SU1400326A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для измерения фазовых сдвигов сигналов от многоканальных интерферометров термоядерных установок | 1983 |

|

SU1352395A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1265769A1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1282121A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Мультимикропрограммное устройство управления | 1983 |

|

SU1161942A1 |

Изобретение относится к измерительной технике и может быть использовано для измерения временных интервалов, по значению которых рассчитывается мгновенная скорость или ускорение движущихся объектов с широким диапазоном скоростей. Цель изобретения - повышение помехозащищенности устройства для измерения временных интервалов и расширение функциональных возможностей. Устройство содержит элементы И-НЕ 11-1N, триггеры 21-2N, элемент ИЛИ-НЕ 3, блокировки, элемент И 4 запуска, элементы И 51-5N, триггер 6 пуска, элемент И-НЕ 7 пуска, формирователь 8 микрокоманд, элемент ИЛИ-НЕ 9 останова, элемент И-НЕ 10 пуска частоты, триггер 11 подключения частоты, элемент И 12 блокировки частоты, счетчик 13 импульсов, запоминающий блок, состоящий из регистров 141-14N-1, первый коммутатор 15, второй коммутатор 16, элементы ИЛИ-НЕ 171-17N входы 181-18N запускающих импульсов устройства, вход 19 коммутации частоты и регистров устройства, входы 201-20K частот устройства, вход 21 сброса устройства, выход 22 устройства. Формирователь 8 микрокоманд содержит четыре D-триггера, элемент И и элемент ИЛИ-НЕ. В предложенном устройстве по сравнению с прототипом помехозащищенность при наличии помех в линиях связи с внешними датчиками выше за счет последовательного разрешения триггерами 21 - 2N приема запускающих импульсов через элементы И-НЕ 11 - 1N. Введение второго коммутатора расширяет функциональные возможности устройстваза счет измерения временных интервалов для объектов с широким диапазоном скоростей движения. 1 з.п. ф-лы, 2 ил.

Изобретение относится к измери- тельной технике и может быть использовано в спортивной метрологии для измерения временных интервалов, по значению которых рассчитывается в дальнейшем мгновенная скорость или отрицательное (положительное) ускорение движущихся объектов с широким диапазоном скоростей (спортивных снарядов, спортсменов и т.д.).

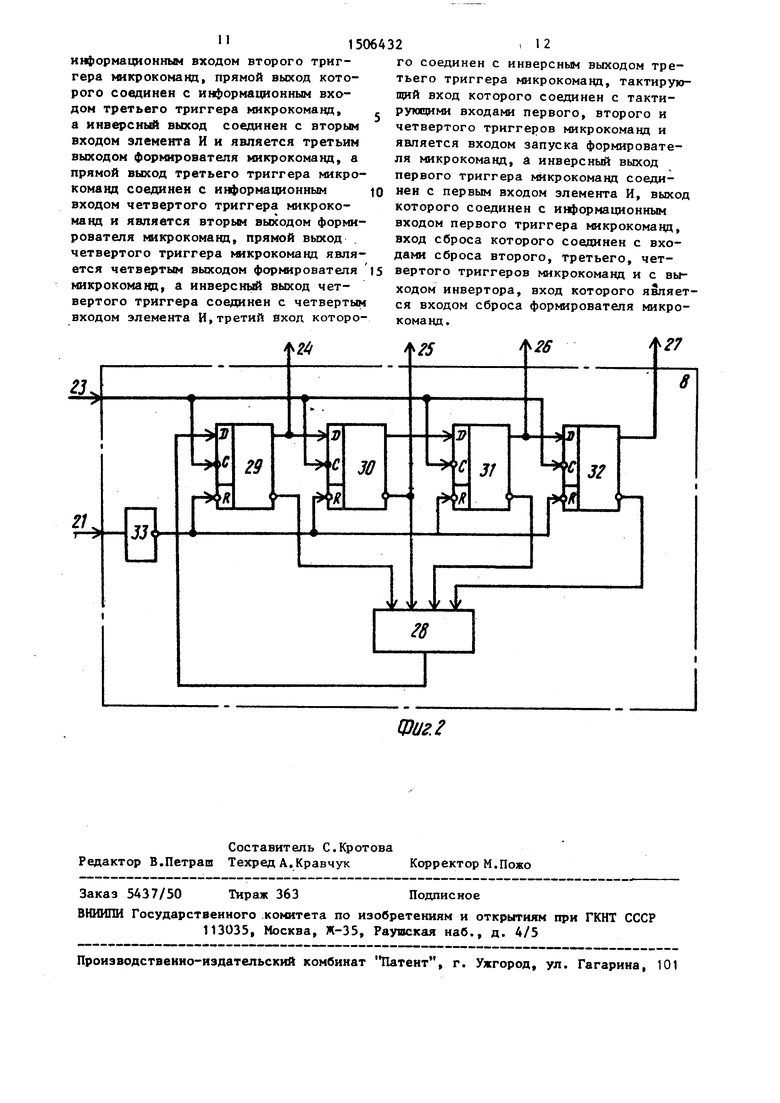

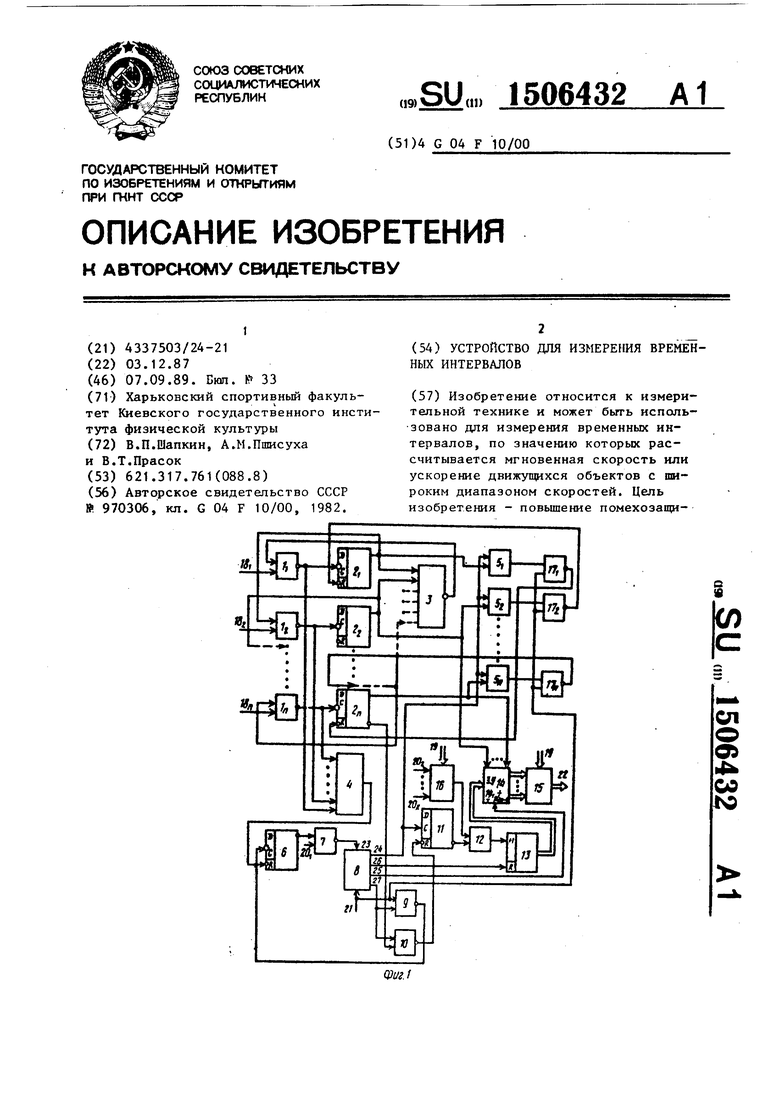

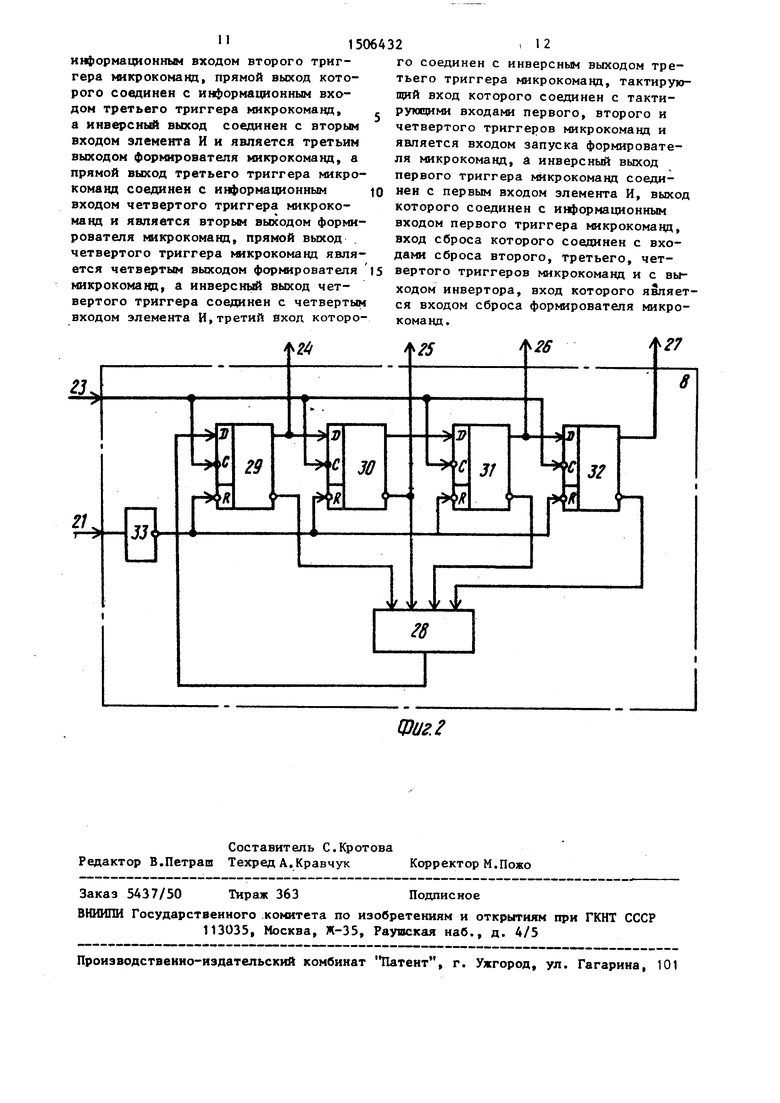

Цель изобретения - повышение по--- мехозащищенности и расширение функциональных возможностей устройства. На фиг. 1 представлена функциональная схема устройстваi на фиг. 2 функциональная схема формирователя микрокоманд.

Устройство содержит элементы И-НЕ ° 1,-1„, триггеры 2,-2п, элемент ИЛИ- НЕ 3 блокировки, элемент И 4 запуска, элементы И 5i-5 , триггер 6 пус ка, элемент И-НЕ 7 пуска, формирователь 8 микрокоманд, элемент ИЛИ-НЕ 9 останова, элемент И-НЕ 10 пуска частоты, триггер 11 подключения частоты, элемент 12 И блокировки часто- ты, счетчик 13, запоминающий блок 14 состоящий из регистров ,, первый коммутатор 15, второй коммутатор 16, элементы ИЛИ-НЕ , входы 18,-18„ запускающих импульсов уст- ройства, вход 19 коммутации частоты и регистров устройства, входы 20т- 20 частот устройства, вход 21 сброса устройства, выход 22 устройства.

Причем входы запускающих импульсов устройства соединены соответственно с вторыми входами элементов И-НЕ , первые входы которых за исключением первого входа первого элемента И-НЕ 1,, соединены соответственно с выходами триггеров 2,-2„,, соответственно с первыми входами элементов И 5, -5 f,.| и соответственно с первого по (п-1)-й входами элемента ИЛИ-НЕ 3 блокировки, выход которого соединен с первым входом первого элемента И-НЕ 1,. Прямой выход п-го триггера 2 р соединен с первым входом п- го элемента И 5 и входом разрешения записи (п-1)-го регистра 14 f,.,. Выходы с второго по (п-1)-й триггеров 2,-2 , соединены соответственно с входами разрешения записи с первого по (п-2)-й регистров 14,-14 вторые входы с первого по п-й элементов 5 ,- 5п соединены между собой, с первым выходом 24 формирователя 8 микрокоманд и с тактирующим входом триггера 11 подключения частоты, выход которого соединен с первым входом элемента И 12 блокировки частоты, второй вход которого соединен с выходом второго коммутатора, первая группа входов которого является с второго по к-й .входами частот устройства, включая и первый вход 20, который соединен с вторым входом элемента И-НЕ 7 пуска, а вторая группа входов соединена с группой управляющих

входов первого коммутатора 15 и является входом 19 коммутации частоты.

Второй 25, третий 26 и четвертый 27 выходы формирователя 8 микрокоманд соединены соответственно с сии- хровходами с первого по (п-1)-й регистров 1,,., запоминающего блока 14, входом сброса счетчика 13, с первым входом элемента И-НЕ 10 пуска ча тоты и вторым входом элемента ИЛИ-НЕ 9 останова, nepBbDi вход которого соединен с вторыми входами с первого по п-й элементов ИЛИ-НЕ 17,-17, входом сброса формирователя 8 микрокоманд и является входом 21 сброса устройства Вход 23 запуска формирователя 8 микрокоманд соединен с выходом элемента И-НЕ 7 пуска, первый вход которого соединен с выходом триггера 6 пуска, тактирующий вход которого соединен с выходом элемента ИЛИ-НЕ 9 останова. Выход элемента И-НЕ 10 пуска частоты соединен с входом сброса триггера 11 подключения частоты, выход элемента И 12 блокировки частоты соединен с входом счета счетчика 13, группа выходов которого соединена с группами входов с первого по (п-1)-й регистров , запоминающего блока 14, с первой по (п-1)-ю группы выходов которых соединены с соответствующими группами входов первого коммутатора 15, группа выходов которого является выходом 22 устройства.

Вход сброса триггера 6 пуска соединен с выходом элемента И 4 пуска, с первого по п-й входы которого соединены с выходами соответственно с первого по п-й элементов И-НЕ 1,-1, и тактирующими входами с первого по п-й триггеров 2,-2. Вход сброса п- го триггера 2 соединен с выходом первого элемента ИЛИ-НЕ 17., выходы с второго по п-й элементов ИЛИ-НЕ 17,-17 соединены соответственно с входами сброса с первого по (п-1)-й триггеров 2,-.,. Первые входы с первого по п-й элементов ИЛИ-НЕ 17,- 17 соединены соответственно с выходами с первого по п-й элементов И 5,-5j,. Инверсный выход п-го триггера 2 соединен с вторым входом элемента И-НЕ 10 пуска частоты.

Формирователь 8 микрокоманд содер--гс хождение запускающего импульса. Оджит элемент И 28, первый 29, второй 30, третий 31 и четвертый 32 триггеры ми1фок( манд, инвертор 33, причем прямой выког первого триггера 29 микроновременно высокий уровень на выходе первого триггера 2 разрешает (подготавливает) прием запускающего импульса с входа 181 через второй эле5

0

5

д

0

5

0

5

0

команд является первым выходом 24 формирователя 8 микрокоманд и соединен с информационным входом второго триггера 30 микрокоманд, прямой выход которого соединен с информационным входом третьего триггера 31 микрокоманд, а инверсный выход соединен с вторым входом элемента И 28 и является третьим выходом 25 формирователя 8 микрокоманд. Прямой выход третьего триггера 31 микрокоманд соединен с информационным входом четвертого триггера 32 микрокоманд и является вторым выходом 26 формирователя 8 микрокоманд. Прямой выход четвертого триггера 32 микрокоманд является четвертым выходом 27 формирователя 8 микрокоманд. Инверсный выход четвертого триггера 32 микрокоманд соединен с четвертым входом элемента И 28, третий вход которого соединен с инверсным выходом третьего триггера 31 микрокоманд, тактирующий вход которого соединен с тактирующими входами первого 29, второго 30 и четвертого 32 триггеров микрокоманд и является входом запуска формирователя 8 микрокоманд. Инверсньй выход первого триггера 29 микрокоманд соединен с первым входом элемента И 28, выход которого соединен с информагщонным входом первого триггера 29 микрокоманд, вход сброса которого соединен с входами сброса второго 30, третье-го 31 и четвертого 32 триггеров микрокоманд и с выходом инвертора 33, вход которого является входом сброса формирователя 8 микрокоманд.

Устройство работает следующим образом.

На вход 21 сброса устройства поступает импульс, который сбрасывает в О с первого по п-й триггеры 2i- 2|, с первого по четвертый триггеры 29-32 микрокоманд, счетчик 11 и записывает 1 в триггер 6 пуска. На первый вход 18, поступает запускающий импульс, взводит первый триггер 2, и сбрасьгаает триггер 6 пуска. При этом на первый вход первого элемента И-НЕ 1, через элемент ИЛИ-НЕ 3 блокировки приходит низкий уровень сигнала и блокирует повторное проновременно высокий уровень на выходе первого триггера 2 разрешает (подготавливает) прием запускающего импульса с входа 181 через второй элемент И-НЕ 1, во второй триггер 2, При этом на остальных первых входах с третьего по п-й элементов 1, низкий уровень (блокировка приема

запускающих импульсов). Высокий уровень сигнала на выходе триггера 6 пуска после его сброса разрешает про- хождениа высокой частоты (относительно частот на входах 20 частот с второго по к-й) на формирователь 8 микрокоманд.

Формирователь 8 микрокоманд работает в режиме сдвига. По первому импульсу на входе 23 запуска формиро- ватепя 8 микрокоманд взводится первый триггер 29 микрокоманд, по второму импульсу взводится второй триггер 30 микрокоманд и сбрасьшается первый триггер 29 микрокоманд и т.д. Микрокоманда на выходе 24 формирователя 8 микрокоманд взводит триггер 11 подключения частоты, который блокирует прохождение частоты из второго коммутатора 16 на вход счета счет- чика 13 и сбрасывает п-й триггер 2. Микрокоманда на выходе 25-й формирователя 8 Iикpoкoмaнд поступает на син- хровходы с первого по (п-1)-й регистров запоминающего блока 14, но первый раз (обработка запускающего импульса по первому входу 18 информащ я с выхода счетчика 13 не заносится в регистры 14,-14,. Микрокоманда на выходе 26 формирователя 8 микрокоманд сбрасывает счетчик 13 в О, а микрокоманда на выходе 27 сбрасывает триггер 11 подключения частоты и взводит триггер 6 пуска, который блокирует импульсы на вход 23 запуска формирователя 8 микрокоманд. Частота с выхода второго коммутатора 16 поступает на вход счета счетчика 13. Второй коммутатор 16 настроен на частоту по входу 19 ком- мутации частоты и регистров устройства, которое значительно выше частоты поступления запускающих импульсов на входах 18 ,-18 .

Таким образом, счетчик 13 с мо- мента сброса триггера 6 пуска начинает отсчет временного интервала до прихода запускающего импульса на второй вход 181. С приходом его взводится второй триггер 2г и триггер 6 пуска микрокоманд, на выходе 24 формирователя В микрокоманд взводит триггер 11 подключения частоты и блокирует частоту, поступающую на вход

счета счетчика 13, и сбрасывает через второй злемент И 5 и второй зле- мент ИЛН-НЕ 17 первый триггер 2,, Микрокоманда на выходе 25 формирователя микрокоманд записывает во второй регистр 14, запоминающего блока 14 содержимое счетчика 13. Запись во второй регистр 14 разрешается сигналом по входу разрешения записи второго регистра 14, поступающим с выхода второго триггера 2 . Микрокоманда на выходе 26 формирователя 8 микрокоманд сбрасывает счетчик 13, а микрокоманда на выходе 27 формирователя микрокоманд сбрасывает триггер 11 подключения частоты, счетчик 13 начинает подсчет следующего интервала времени и взводит триггер 6 пуска, которьй блокирует прохождение импульсов на вход 23 запуска формирователя 8 микрокоманд.

С приходом последующих запускающих импульсов по входам 18-18 устройство работает аналогично. Взводятся соответствующие триггеры 18j- 18, и содержимое счетчика 13 записывается в соответствующие регистры . При обработке запускающего импульса, поступающего на п-й вход 18, микрокоманда на выходе 27 формирователя 8 микрокоманд блокируется на элементе И-НЕ 10 пуска частоты низким уровнем сигнала, который поступает с инверсного выхода взведенного п-го триггера 2. Триггер 11 подключения частоты не сбрасьшается.

Устройство в результате зтой блокировки подготавливается к следующему циклу работы.

Таким образом, в регистрах запоминающего блока 14 за один 1щкл работы устройства запоминается п-1 временных интервалов. Содержимое регистров 14,-14, поступает на выход 22 устройства при управлении первого коммутатора 15 по входу 19 коммутации частоты и выходам регистров устройства и далее на индикацию.

У предлагаемого устройства достоверность измерения временных интервалов выше при наличии помех в линия связи с внешними датчиками (по входам запускающих импульсов) за счет последовательного разрешения триггерми 2 -2 приема запускающих импульсов через элементы 1 ,-1 по сравнению с известным устройством расширены функциональные возможности за

счет настройки устройства с помощью коммутатора 16 частот на измерение временных интервалов для объектов с широким диапазоном скоростей движения.

Формула изобретения

запуска, с первого по п-й элементы И, триггер пуска, элемент И-НЕ nycka, формирователь микрокоманд, элемент останова, элемент И-НЕ-пуска25

частоты, триггер подключения частоты, элемент И блокировки частоты, второй коммутатор, с первого по п-й элементы ИЛИ-НЕ, причем с первого по п-й входы запускающих импульсов уст- 30 ройства соединены соответственно с вторыми входами с первого по п-й элементов И-НЕ, первые входы которых, за исключением первого входа первого элемента И-НЕ, соединены соответст- 55 венно с выходами с первого по (п-1)-й триггеров, соответственно с первыми входами с первого по (п-1)-й элементов И и соответственно с первым - (п-1)-м входами элемента ИЛИ-НЕ бло- 40 кировки, выход которого соединен с первым входом первого элемента И-НЕ, прямой выход п-го триггера соединен с первым входом п-го элемента И и

динен с выходом элемента И-НЕ пуска, первый вход которого соединен с выходом триггера пуска, тактирующий вход которого соединен с выходом элемента ИЛИ-НЕ останова, а выход эл ента И-НЕ пуска частоты соединен с входом сброса триггера подключения частоты, а выход элемента И блокиров ки частоты соединен с входом счета счетчика, группа выходов которого со динена с группами входов первого коммутатора, группа выходов которого является выходом устройства, а вход сброса триггера пуска соединен с FM- ходом элемента И пуска, с первого по п-й входы которого соединены с выхо дами соответственно с первого по п-й элементов И-НЕ и с тактирую1цими входами с первого по п-й триггеров, а вход сброса п-го триггера соединен с выходом первого элемента ИЛИ-НЕ, а выходы с второго по п-й элементов ИЛИ-НЕ соединены соответственно с

(п-1)-м входом разрешения записи за- дЗ входам г сброса с первого по (п-1)-й

поминающего блока, а выход с второго по (К-1)-й триггеров соединены соответственно с первым - (п-2)-м входами разрешения записи запоминающего блока, а вторые входы с первого по п-й элементов И соединены между собой, с первым выходом формирователя микрокоманд и с тактирующим входом триггера подключения частоты, выход которого соединен с первым входом элемента И блокировки частоты, второй вход которого соединен с выходом второго комм тгатора, п.ервая группа входов которо о является с второго по

входом сброса устройства, а вход за- пуска формирователя микрокоманд соек-й входами частот устройства,первый вход частоты устройства соединен с вторым входом элемента И-НЕ пуска, вторая группа входов второго коммутатора соединена с группой управляющих входов первого коммутатора и является входом коммутации частоты и регистров, второй, третий, четвертый выходы формирователя микрокоманд соединены соответственно с синхровхода- ми с первого по (п-1)-й регистров, входом сброса счетчика, с первым входом элемента И-НЕ пуска частоты и с вторым входом элемента ИЛИ-НЕ останова, первый вход которого соединен с вторыми входами с первого по п-й элементов ИЛИ-НЕ, входом сброса формирователя микрокоманд и является

динен с выходом элемента И-НЕ пуска, первый вход которого соединен с выходом триггера пуска, тактирующий вход которого соединен с выходом элемента ИЛИ-НЕ останова, а выход эле ента И-НЕ пуска частоты соединен с входом сброса триггера подключения частоты, а выход элемента И блокировки частоты соединен с входом счета счетчика, группа выходов которого содинена с группами входов первого коммутатора, группа выходов которого является выходом устройства, а вход сброса триггера пуска соединен с FM- ходом элемента И пуска, с первого по п-й входы которого соединены с выхо дами соответственно с первого по п-й элементов И-НЕ и с тактирую1цими входами с первого по п-й триггеров, а вход сброса п-го триггера соединен с выходом первого элемента ИЛИ-НЕ, а выходы с второго по п-й элементов ИЛИ-НЕ соединены соответственно с

0

5

триггеров, а первые входы с первого по п-й элементов ИЛИ-НЕ соединены соответственно с выходаг-я с первого по п-й элементов И, инверсный выход п-го триггера соединен с вторым входом элемента И-НЕ пуска частоты.

информационным входом второго триггера микрокоманд прямой выход которого соединен с информационным входом третьего триггера микрокоманд, а инверсньМ выход соединен с вторым входом элемента И и является третьим выходом формирователя микрокоманд, а прямой выход третьего триггера микрокоманд соединен с информационным входом четвертого триггера микрокоманд и является вторым выходом формирователя микрокомацц, прямой выход четвертого триггера к«крокоманд является четвертым выходом формирователя микрокоманд, а инверсньй выход четвертого триггера соединен с четвертым входом элемента И,третий вход которого соединен с инверсным выходом третьего триггера микрокоманд, тактирующий вход которого соединен с тактирующими входами первого, второго и четвертого триггеров микрокоманд и является входом запуска формирователя микрокоманд, и инверсный выход первого триггера микрокоманд соединен с первым входом элемента И, выход которого соединен с информационным входом первого триггера микрокоманд, вход сброса которого соединен с входами сброса второго, третьего, четвертого триггеров микрокоманд и с выходом инвертора, вход которого является входом сброса формироватепя микрокоманд.

Ц) и г. г

| Многоканальный измеритель временных интервалов | 1981 |

|

SU970306A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-09-07—Публикация

1987-12-03—Подача