Изобретение относится к технике связи, может использоваться при построении пря- мопередатчиков широтноимпульсной манипуляции, и является усовершенствованием изобретения по авт. св. № 1665529.

Цель изобретения - увеличение скорости передачи при обмене информацией.

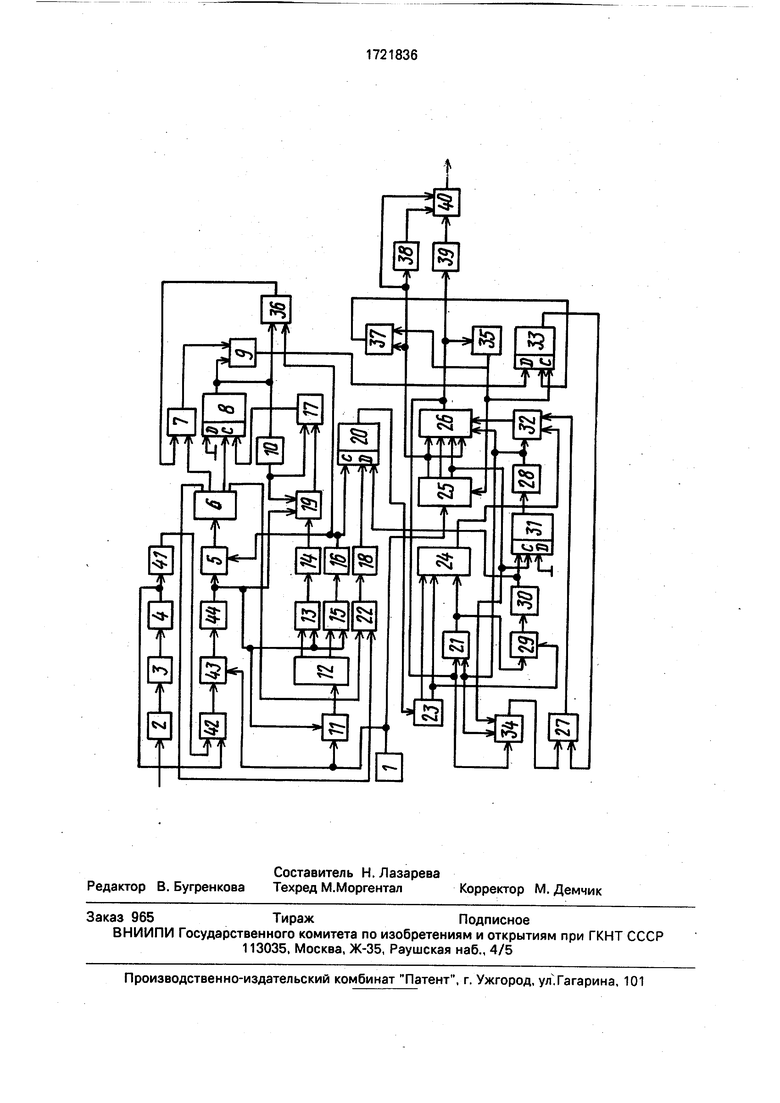

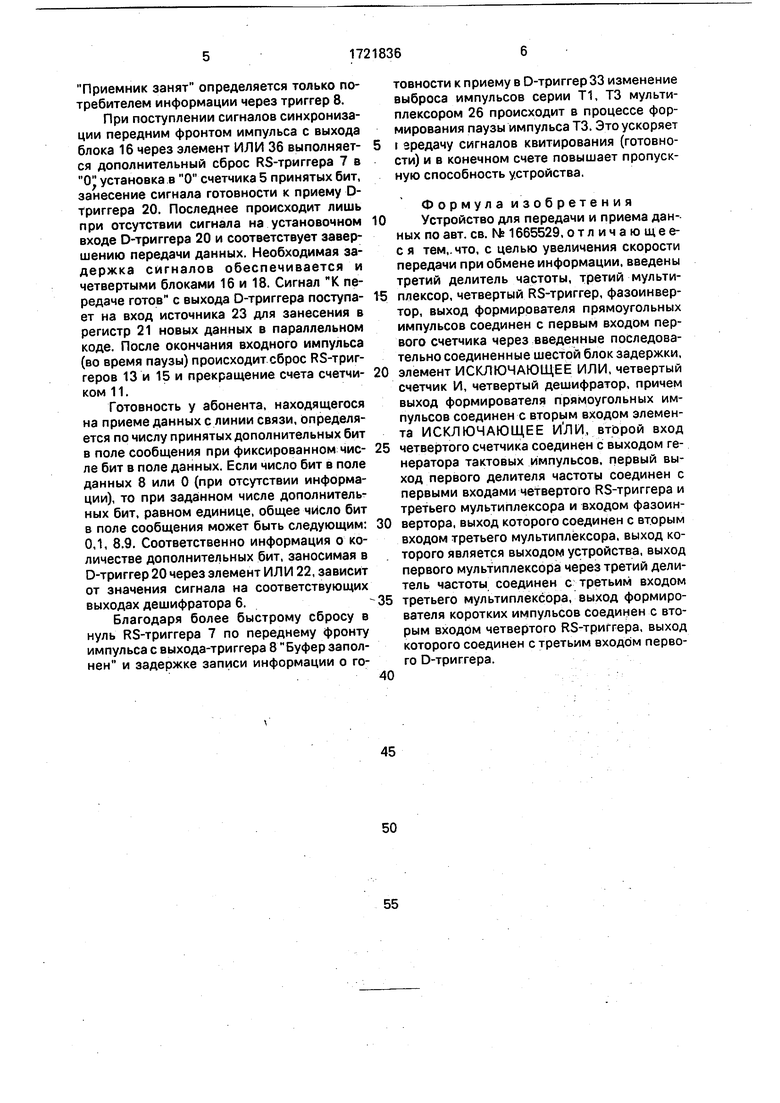

На чертеже изображена структурная электрическая схема устройства.

Устройство содержит генератор 1 тактовых импульсов, усилитель 2, фильтр 3 нижних частот, формирователь 4 прямоугольных импульсов, первый счетчик 5, первый дешифратор 6, первый RS-триггер 7, триггер 8 Буфер заполнен, первый элемент ИЛИ 9, второй блок 10 задержки, второй счетчик 11, второй дешифратор 12, второй RS-триггер 13, первый блок 14 задержки, третий RS-триггер 15, третий блок 16 задержки, блок 17 потребителя информации, четвертый блок 18 задержки, первый регистр 19 сдвига, второй D-триггер 20, второй элемент И 21, второй элемент ИЛИ 22, источник 23 информации, второй регистр 24

сдвига, первый делитель 25 частоты, первый мультиплексор 26, первый элемент И 27, пятый блок 28 задержки, третий счетчик 29, третий дешифратор 30, третий D-триггер 31, второй мультиплексор 32, первый D-триггер 33, второй делитель 34 частоты, формирователь 35 коротких импульсов, третий элемент ИЛИ 36, четвертый RS-триггер 37, фазоинвертор 38, третий делитель 39 частоты, третий мультиплексор 40, шестой блок 41 задержки, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 42, четвертый счетчик 43, четвертый дешифратор 44.

Устройство работает следующим образом.

Делитель 25 частоты, работающий от генератора 1, формирует три последовательности импульсов разной длительности Т1 Т2 ТЗ, поступающие на вторые входы мультиплексора 26. Выходной сигнал последнего зависит от значения управляющих сигналов, действующих на его первом и третьем входах,

(Л

С

vi

го

00 OJ

о

JO

Формирователь 35 коротких импульсов вырабатывает последовательность импульсов, совпадающих по времени с отрицательными перепадами выходного сигнала. Этой последовательностью производится синхронизация счетчиков делителя 25 частоты для получения импульсов со скважностью 0,5, сброс RS-триггера 37 и установка D- триггера 33 в состояние, обеспечивающее формирование импульсов ТЗ.

Данные от источника 23 информации в параллельном коде записываются в регистр 24. Строб сопровождения данных устанавливает в О счетчик 29. Очередным перепадом (отрицательным) с соответствующего выхода делителя 25 частоты D-триггер 31 устанавливается в состояние, при котором сигнал с выхода блока 28 задержки разрешает через элемент И 21 выполнение сдвига регистра 24 и счет числа переданных бит счетчиком 29. Кроме этого, на управляющих входах мультиплексоров 26 и 32 устанавливается значение сигналов, обеспечивающих формирование импульсов длительностью Т1 и Т2. Далее происходит сдвиг по каждому заднему фронту импульсов с выхода мультиплексора 26 в регистре 24 сдвига. В зависимости от значения очередного бита на выходе мультиплексора 26 формируется импульс длительностью Т1 и Т2. По окончании передачи происходит изменение значения сигнала на выходе дешифратора 30 и установка D-триггера 31 в состояние, обеспечивающее передачу комбинации импульсов длительностью Т1 и ТЗ или только импульсов синхронизации длительностью ТЗ, прекращение сдвига информации в регистре 24 и счета числа импульсов счетчиком 29. Состав комбинации импульсов синхронизации (если дополнительно передают только один бит) длительностью Т1 и ТЗ или ТЗ зависит от состояния D-триггера 33. Длительность импульсов при этом (Т1 и ТЗ) определяется значением сигналов на выходе дешифратора 30 и на выходе D-триггера 33, соединенного с элементом И 27.

Для продолжения передачи записываются новые данные из источника 23 информации в регистр 24 сдвига. От состояния D-триггера 33 и значения сигнала на выходе делителя 34 частоты на два через элемент И 27 зависит формирование дополнительного бита в виде импульса длительностью Т1 или импульса синхронизации ТЗ. Для увеличения пропускной способности устройства при формировании импульса синхронизации ТЗ от делителя 25 частоты синхронизируется делитель 34. В нем устанавливается состояние, обеспечивающее формирование импульса ТЗ независимо от состояния Dтриггера 33. Благодаря этому группа импульсов синхронизации может состоять из одного импульса.

Сигнал с выхода мультиплексора 26 делится делителем 39, образуя на выходе импульсы, фронт которых совпадает с задним фронтом импульсов на выходе мультиплексора 26. Этим сигналом управляется мультиплексор 40, на входы которого поданы

0 импульсы с частотой Т1, сдвинутые по фазе. В результате на выходе устройства получается сигнал с фазовой манипуляцией, содержащий составляющие с частотами Т1 и Т2. Входной аналоговый сигнал из линии

5 связи через усилитель 2, фильтр 3 и формирователь 4 поступает на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 42, на выходе которого благодаря наличию блока 41 задержки, образуются короткие импульсы по фронту

0 каждого импульса на входе устройства, выполняющие сброс в О счетчика 33. С помощью счетчика 43 и дешифратора 44 выделяются импульсы с длительностью между фронтами Т2 путем подсчета такто5 вых импульсов генератора 1.

Импульсы с выхода дешифратора 44 поступают на блоки 5,11 и 19. С помощью счетчика 11 измеряется длительность паузы между импульсами путем подсчета импуль0 сов с выхода генератора 1. В зависимости от длительности паузы входных импульсов с помощью дешифратора 12 устанавливаются в 1 триггеры 13 и 15. Если длительность паузы ТЗ, то оба триггера устанавливаются

5 в 1, а если Т2, то только триггер 13. По фронту входного импульса происходит сдвиг данных в регистре 19. Необходимая задержка обеспечивается блоком 14. Одновременно происходит счет числа принятых

0 бит счетчиков 5. Если принять хотя бы два бита, то сигналом с второго выхода дешифратора 6 устанавливается в 1 триггер 7, что означает Приемник занят. После приема всего поля данных с известным фиксирован5 ным числом бит устанавливается в 1 триггер 8. С помощью элемента ИЛИ 9 формируется сигнал К приему не готов, поступающий на D-вход D-триггера 33. Он запоминается по фронту импульса, поступа0 ющего на тактовый вход D-триггера 33 с выхода RS-триггера 37, который устанавливается в 1 по фронту импульса Т1. Сигнал Буфер заполнен с выхода триггера 8 через блок 10 поступает на вход регистра 19, за5 прещая сдвиг в нем. Одновременно он поступает в блок 21, а также через элемент ИЛИ 36 сбрасывает в нуль RS-триггер 7. После считывания данных из регистра 19 блок 21 устанавливает триггер 8 в исходное состояние. После этого состояние сигнала

Приемник занят определяется только потребителем информации через триггер 8.

При поступлении сигналов синхронизации передним фронтом импульса с выхода блока 16 через элемент ИЛИ 36 выполняется дополнительный сброс RS-триггера 7 в 0 установка в О счетчика 5 принятых бит, занесение сигнала готовности к приему D- триггера 20. Последнее происходит лишь при отсутствии сигнала на установочном входе D-триггера 20 и соответствует завершению передачи данных. Необходимая задержка сигналов обеспечивается и четвертыми блоками 16 и 18. Сигнал К передаче готов с выхода D-триггера поступает на вход источника 23 для занесения в регистр 21 новых данных в параллельном коде. После окончания входного импульса (во время паузы) происходит сброс RS-триг- геров 13 и 15 и прекращение счета счетчиком 11.

Готовность у абонента, находящегося на приеме данных с линии связи, определяется по числу принятых дополнительных бит в поле сообщения при фиксированном числе бит в поле данных. Если число бит в поле данных 8 или 0 (при отсутствии информации), то при заданном числе дополнительных бит, равном единице, общее число бит в поле сообщения может быть следующим: 0,1, 8.9. Соответственно информация о количестве дополнительных бит, заносимая в 0-триггер 20 через элемент ИЛИ 22, зависит от значения сигнала на соответствующих выходах дешифратора 6.

Благодаря более быстрому сбросу в нуль RS-триггера 7 по переднему фронту импульса с выхода-триггера 8 Буфер заполнен и задержке записи информации о готовности к приему в D-триггерЗЗ изменение выброса импульсов серии Т1, ТЗ мультиплексором 26 происходит в процессе формирования паузы импульса ТЗ. Это ускоряет i эредачу сигналов квитирования (готовности) и в конечном счете повышает пропускную способность устройства.

Ф о р м у л а и з о б р ет е н и я

Устройство для передачи и приема данных по авт. св. № 1665529, отличающееся тем,, что, с целью увеличения скорости передачи при обмене информации, введены третий делитель частоты, третий мультиплексор, четвертый RS-триггер, фазоинвер- тор, выход формирователя прямоугольных импульсов соединен с первым входом первого счетчика через введенные последовательно соединенные шестой блок задержки,

элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, четвертый счетчик И, четвертый дешифратор, причем выход формирователя прямоугольных импульсов соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход

четвертого счетчика соединен с выходом генератора тактовых импульсов, первый выход первого делителя частоты соединен с первыми входами четвертого RS-триггера и третьего мультиплексора и входом фазоинвертора, выход которого соединен с вторым входом третьего мультиплексора, выход которого является выходом устройства, выход первого мультиплексора через третий делитель частоты соединен с третьим входом

третьего мультиплексора, выход формирователя коротких импульсов соединен с вторым входом четвертого RS-триггера, выход которого соединен с третьим входом первого D-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и передачи двоичной информации | 1984 |

|

SU1748275A1 |

| Устройство для передачи и приема данных | 1989 |

|

SU1665529A1 |

| Устройство для приема и передачи цифровой двоичной информации | 1989 |

|

SU1693734A1 |

| Устройство для последовательного обмена данными с квитированием | 1989 |

|

SU1720164A1 |

| Устройство для передачи информации | 1990 |

|

SU1753615A1 |

| Устройство для приема и передачи данных | 1989 |

|

SU1688438A1 |

| Устройство для передачи и приема данных в полудуплексном режиме | 1990 |

|

SU1732485A1 |

| Устройство для передачи и приема информации | 1990 |

|

SU1748276A1 |

| Устройство для приема и передачи данных в дуплексном режиме | 1987 |

|

SU1506576A1 |

| Устройство для передачи и приема данных | 1990 |

|

SU1786678A1 |

Изобретение относится к технике связи. Целью изобретения является увеличение скорости передачи при обмене информации. Для достижения поставленной цели устройство содержит передатчик и приемник данных, передаваемых методом широтно- импульсной манипуляции. Дополнительно введены делитель частоты, мультиплексор, RS-триггер и фазоинвертор, которые обеспечивают преобразования широтно-им- пульсной манипуляции в фазовую и наоборот. 1 ил.

| Устройство для передачи и приема данных | 1989 |

|

SU1665529A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-03-23—Публикация

1989-09-07—Подача