СП

оо

СР 4

5

10

Изобретение относится к электро- С1ВЯЗИ и может использоваться в приемопередатчиках с широтно-импульсной манипуляцией.

I Цель изобретения - повышение ско- Р;ости обмена информацией.

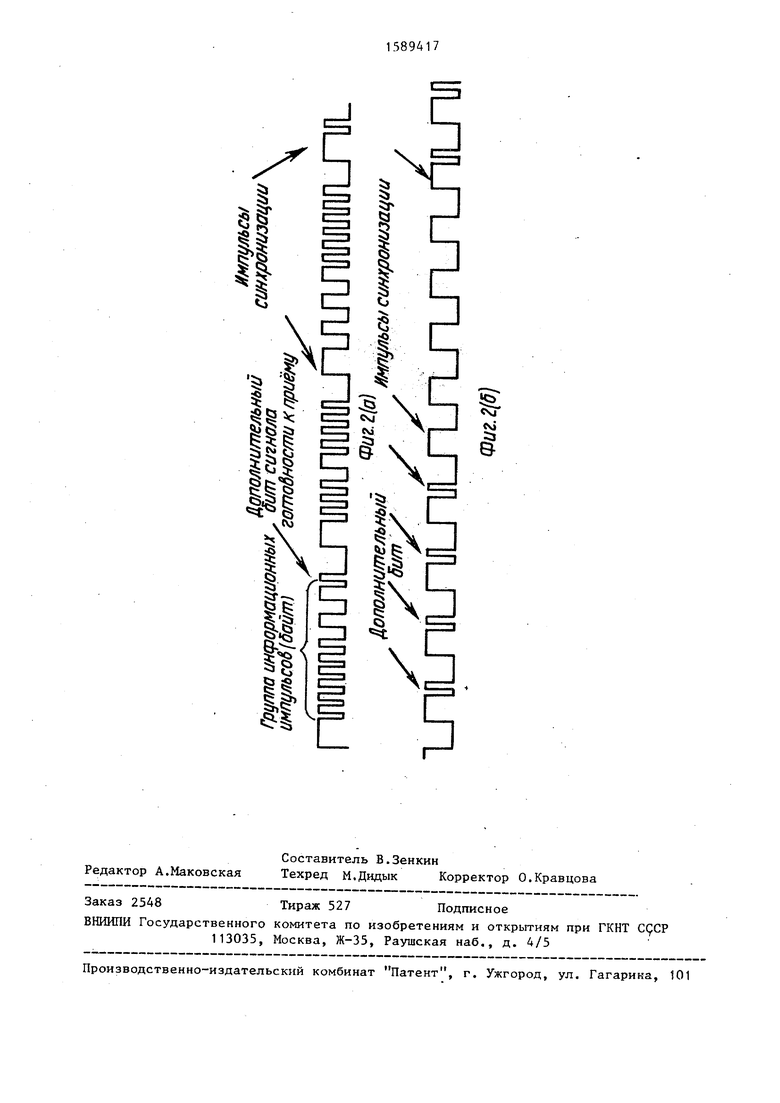

На фиг. 1 представлена структурная электрическая схема устройства для пе- р едачи и приема данныхj на фиг. 2 - временные диаграммы, поясняющие его р|аботу.

I Устройство для передачи и приема данных содержит тактовый Генератор 1, усилитель 2, фильтр 3 нижних частот, формирователь 4 прямоугольных импуль- сов, первый счетчик 5, первый де:ши- фратор 6, первый и второй RS-тригге- ры 7 и 8, первый элемент ИЛИ 9, пер- Вэ1й блок 10 задержки, второй счет- 20 чик 11, второй дешифратор 12, третий RS-триггер 13, второй блок 14 задержки, четвертый RS-триггер 15, третий 16 задержки, формирователь 17 К10РОТКИХ импульсов, четвертый блок 18 25 з;адержки, первый регистр 19 сдвига, первый D-триггер 20, потребитель 21 И|нформации, первый элемент И 22, ис- тЬчник 23 информации, второй регистр 2|4 сдвига, первый делитель 25 часто- , первый мультиплексор 26, второй э пемент И 27, пятый блок 28 задерж- Ци, третий счетчик 29, третий дешифра- 30, второй D-тригге р 31, второй ityльтиплeкcop 32 и тр.етий D-триггер 33, а также второй элемент ИШ1 34, 1 ретий элемент И 35 и второй делитель 36 частоты.

Устройство для передачи и приема Данных работает следующим образом.

Первый делитель 25 частоты, работающий от тактового генератора 1, формирует три последовательности им- шульсов разной длительности Т, Т II Т, поступающие на вторые входы пер-д5 13ОГО мультиплексора ,26. Выходной сигнал последнего зависит от значения уп- Эавляющих сигналов, действующих на его первом и третьем входах. На фиг.2 (а) показана форма сигнала на выходе устройства при наличии передаваемой информации; на фиг. 2 (б) - при ее отсутствии.

Формирователь 17 коротких импульсов вырабатьгаает последовательность импульсов, совпадающих по времени с отрицательными перепадами выходного Сигнала. Этой последовательностью проводится сброс первого делителя 25 час30

35

40

50

55

5

0

0 5

д5

0

5

40

50

55

.тоты для получения импул1 сов со скважностью 0,5.

Данные от источника 23 информации в параллельном коде записываются во второй регистр 24 сдвига. Строб сопровождения данных устанавливает в нуль третий счетчик 29. Очередным перепадом (отрицательным) с соответствующего выхода первого делителя 25 частоты второй D-триггер 31 устанавливается в состояние, при котором сигнал с выхода пятого блока 28 задержки разрешает (через второй элемент И 27) выполнение сдвига во втором регистре 24 сдвига и счет числа переданных бит третьим счетчиком 29. Кроме того, на управляющих входах первого и второго мультиплексоров 26 и 32 устанавливаются значения сигналов, обеспечивающих формирование импульсов длительностью Т и Т.., Далее происходит сдвиг по каждому заднему фронту импульсов с выхода, первого мультиплексора 26 во втором регистре 24 сдвига. В зависимости от значения очередного бита формируется импульс длительностью Т или Т . По окончании передачи происходит изменение значения .сигнала на выходе третьего дешифратора 30 и установка второго D-триггера 31 в состояние, обеспечивающее передачу комбинации импульсов длительностью Т и Т.. или только импульсов синхронизации длительностью Т, прекращение сдвига информации во втором регистре 24 сдвига и счет числа импульсов третьим счетчиком 29. Состав комбинации импульсов синхронизации (если дополнительно передают только один бит) длительностью Т, Т или Т,, зависит от состояния третьего D-триггера 33. Л1лительность импульсов при этом (Т., и Т ) определяется значением сигналов на выходе третьего дешифратора 30 и на выходе третьего D- триггера 33, соединенного с третьим элементом И 35.

Информация в третий D-триггер 33 записывается по каждому заднему фронту импульсов с выхода первого мультиплексора 26 и зависит от готовности удаленного абонента к приему. Для продолжения передачи записываются новые данные из источника 23 информации во второй регистр 24 сдвига. От состояния D-триггера 33 и значения сигнала на выходе второго делителя 36 частоты на два (через третий элемент

„ . 15

И Jb зависит формирование дополнительного бита в виде импульса длительностью Т

L, ИЛИ «мпульса синхронизаирии Т. Для увеличения пропускной способности устройства при формировании им- пульса синхронизации T.j от первого делителя 25 частоты синхронизируется второй делитель 36 частоты. В нем устанавливается состояние, обеспечи- вающее формирование импульса Тз независимо от состояния триггера 33. Благодаря этому группа импульсов синхронизации может состоять из одного импульса.

Входной аналоговый сигнал из лини связи через усилитель 2, фильтр 3 ниних частот и формирователь 4 прямоугольных импульсов поступает на блоки 5,11,19. Импульс, поступающий на установочный вход второго счетчика И разрешает начать измерение его длительности путём подсчета импульсов с выхода тактового генератора 1, В зависимости от длительности входных импульсов с помощью второго дешифратор

12устанавливаются в 1 RS-триггеры

13или 15. Если длительность импульса T,j, то оба упомянутых триггера ус Г , а если Т - то

танавливаются в

только D-триггер 13. По задне гу фронту входного импульса происходит сдви данных в первом регистре 19 сдвига. Необходимая задержка обеспечивается вторым блоком 14 задержки. Одновременно происходит счет числа принятых бит первым счетчиком 5. Ьсли приняты хотя бы два бита, то сигналом с второго выход-а первого дешифратора 6 устанавливается в 1 первый RS-триг- гер 7, что означает Приемник занят. После приема всего поля данных с из- вестным фиксированным числом бит устанавливается в 1 второй RS-триг- гер 8. С помощью первого элемента ИЛИ 9 формируется сигнал К приему не готов, поступающий на D-вход триггера 33. Он записьшается задним фронтом импульса, поступающего на С- вход D-триггера 33. Сигнал Буфер заполнен с выхода второго RS-триггера 8 через первый блок 10 задержки поступает на вход первого регистра 19 сдвига, запрещая сдвиг в нем. Одновременно он поступает и к потребителю 21 информации. После считывания данных из регистра 19 второй RS-триг- гер 8 устанавливается в О.

8941

10

535

76

При поступлении импульсов синхронизации выполняются сброс первого КЗ- Триггера 7 в нуль, установка в нуль первого счетчика 5, занесение сигнала готовности к приему в первый D-триг- ,гер 20. Последнее происходит лишь при отсутствии сигнала на его установочном входе и соответствует завершению передачи данных. Необходимая задержка сигналов синхронизации обеспечивается третьим и четвертым блоками 16 и 18 задержки. С помощью первого элемента И 22 формируется сигнал К переда-. , че готов,поступающий затем на вход источника 23 информащш для занесения во второй регистр 24 сдвига новых данных в параллельном коде. После окончания входного импульса (во время 20 паузы) происходит сброс RS-триггеров 13 и 15 и прекращение счета вторым счетчиком 11. В результате источник 23 информации осуществля ет занесение данных во второй регистр 24 для пере- 25 дачи при одновременном наличии сигнала завершения передачи с выхода третьего дешифратора 30 и сигнала К приему готов с выхода первого D-триггера 20.

Готовность абонента, осуществляющего прием данных с линии связи, определяется по числу принятых дополнительных бит в поле сообщения при фиксированном числе бит в поле данных. Если число бит в поле данных 8 или О (при отсутствии информащш), .то при- заданном числе дополнительных бит, равном единице, общее число бит в поле сообщения может быть следующим: 0,1,8,9. Соответственно информация о количестве дополнительных бит заносимая в D-триггер 20 через второй элемент РШИ 34, зависит от значения сигнала на соответствующ11х выходах первого дешифратора 6.

Благодаря отсутствию в полученном сигнале импульсов длительностью Т уменьшаются требования к необходимой полосе пропускания каналов связи, что Q позволяет .повысить скорость обмена информацией.

Формула изобретения

Устройство для передачи и приема данных, содержащее тактовый генератор, последовательно соединенные усилитель фильтр нижних частот и формирователь прямоугольных импульсов, последова30

тел|ьно соединенные первый счетчик и пейвый дешифратор, первый и второй К8-|триггеры, первый элемент ИЛИ, пер- вы1 блок задержки, последовательно сое|диненные второй счетчик и второй де11|ифратор, последовательно соединенные третий RS-триггер и второй блок эалержки, последовательно соединенные четвертый RS-триггер и третий блок задержки, формирователь коротких пульсов, четвертый блок задержки, первый регистр сдвига, первый D-триггер, потребитель информации, последовательно соединенные первьш элемент И и ис- информации, второй регистр сдЕига, первый делитель частоты, первый мультиплексор, второй элемент И, пятый блок задержки, последовательно соединенные третий счётчик и третий дешифратор, второй D-триггер, второй Myj ьтиплексор .и третий D-триггер, ин- фо ;мационный вход которого подключен к выходу первого элемента ИЛИ, входы которого соединены с выходами первого и второго RS-триггеров, первые входы которых подключены соответственно к выходу третьего блока задержки и к выходу потребителя информации neij)BbEft и второй входы которого со- с выходом, и первым входом первого регистра сдвига, второй вход Kofoporo соединен с выходом формиро- прямоугольных импульсов, ne;p- вы1|ш входами первого счетчика, тр€;ть eri и четвертого RS-триггеров и вто- ро:|: о счетчика, второй вход которого подключен к выходу тактового генера- Tojjja и первому входу первого делителя частоты, второй вход которого че- реЬ формирователь коротких импульсов соединен с тактовым входом третьего D-Триггера и выходом первого мультиплексора, первый и вторые входы которого подключены соответственно к выходам второго мультиплексора и первого делителя частоты, причем выходы третьего и четвертого блоков задержки подключены соответственно к так- тойому и информационному входам пер- Boiro D-триггера, вход первого блока задержки соединен с выходом второго RS-триггера, выход третьего дешифратора подключен к установочным входам пе|рвого и второго D-триггеров и пер- во1му входу первого элемента И, выход

второго элемента И соединен с входом третьего счетчика и первым входом второго регистра сдвига, вторые входы третьего и четвертого RS-триггеров подключены к соответствующим выходам второго дешифратора, выход первого D-триггера соединен с вторым входном первого элемента И, выход пятого блока задержки подключен к первому входу второго элемента И, информационный вход второго D-триггера соединен с общей шиной, а выходы источника информации подключены к вторым входам второго регистра сдвига, выход которого соединен с первым входом второго мультиплексора, при этом вьпсод второго блока задержки подключен к третьему входу первого регистра сдвига, первый и второй выходы первого дешифратора соединены с вторыми входами соответственно первого и второго RS-триггеров, выход третьего блока задержки подключен к второму входу первого счетчика, выход первого блока задержки соединен с первым входом первого регистра сдвига, а вход усилителя является входом устройства, выходом которого является выход первого мультиплексора, отличающееся тем, что, с целью повышения скорости обмена информацией введены второй элемент ИЛИ, третий элемент Ни второй делитель частоты, выход которого соединен с первым входом третьего элемента И, второй вход и выход которого подключены соответственно к выходу третьего D-триггера и второму входу второго мультиплексора, третий вход которого соединен с третьим входом первого мультиплексора и выходом пятого блока задержки, вход которого подключён к выходу второго D-триггера, тактовый вход которого соединен с соответствующим выходом первого делителя частоты и первым входом второго делителя частоты, второй вход которого подключен к выходу первого мультиплексора и второму входу второго элемента И, первый вход которого соединен с третьим входом второго делителя частоты, причем первый и второй входы и выход второго элемента ИЛИ подключены соответственно к третьему и четвертому выходам первого дешифратора и входу четвертого блока задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и передачи данных в дуплексном режиме | 1987 |

|

SU1506576A1 |

| Устройство для передачи и приема информации | 1990 |

|

SU1748276A1 |

| Устройство для приема и передачи цифровой двоичной информации | 1989 |

|

SU1693734A1 |

| Устройство для передачи и приема двоичной информации | 1989 |

|

SU1688439A1 |

| Устройство для последовательного обмена данными с квитированием | 1989 |

|

SU1720164A1 |

| Устройство для приема и передачи двоичной информации | 1984 |

|

SU1748275A1 |

| Устройство для передачи и приема данных | 1989 |

|

SU1665529A1 |

| Устройство для передачи и приема данных в полудуплексном режиме | 1990 |

|

SU1732485A1 |

| Устройство для передачи и приема данных | 1989 |

|

SU1721836A2 |

| Устройство для передачи информации | 1990 |

|

SU1753615A1 |

Изобретение относится к электросвязи и может быть использовано в приемопередатчиках с широтно-импульсной манипуляцией. Цель изобретения - повышение скорости обмена информацией. Для достижения цели в устройство введены второй элемент ИЛИ 34, третий элемент И 35 и второй делитель 36 частоты. Число переданных и принятых бит передаваемого сигнала определяется мультиплексором 26, переключающим на свой выход импульсы трех возможных длительностей. Анализ принятого сигнала осуществляется дешифратором 12. Готовность абонента к приему информации определяется по числу дополнительных бит в поле данных с помощью D -триггера 20 и дешифратора 6. 2 ил.

| Устройство для приема и передачи данных в дуплексном режиме | 1987 |

|

SU1506576A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-08-30—Публикация

1988-11-09—Подача