Изобретение относится к технике приема и передачи цифровой информа- ции.

Цель изобретения - увеличение пропускной способности при обмене цифровой информации.

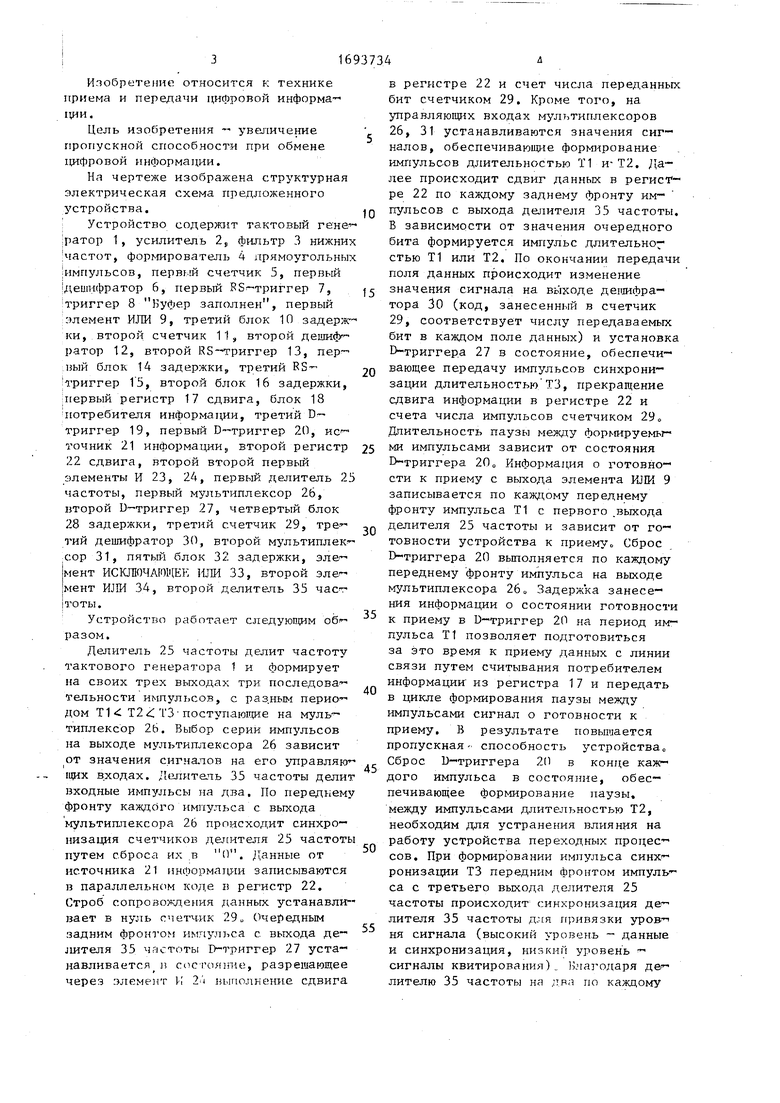

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство содержит тактовый ге не- ратор 1, усилитель 2, фильтр 3 нижних частот, формирователь 4 лрямоугольных импульсов, первый счетчик 5, первый дешифратор 6, первый FS-триггер 7, триггер 8 Буфер заполнен, первый элемент ИЛИ 9, третий блок 10 задержи ки, второй счетчик 11, второй дешиф- ратор 12, второй RS-триггер 13, пер- вый блок 14 задержки, третий RS триггер 15, второй блок 16 задержки, первый регистр 17 сдвига, блок 18 потребителя информации, третий D- триггер 19, первый D-триггер 20, точник 21 информации, второй регистр 22 сдвига, второй второй первый элементы И 23, 24, первый делитель 25 частоты, первый мультиплексор 26, второй U-триггер 27, четвертый блок 28 задержки, третий счетчик 29, тре- тий дешифратор 30, второй мультиплек- сор 31, пятый блок 32 задержки, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 33, второй элемент ИЛИ 34, второй делитепь 35 час- тоты.

Устройство работает следующим образом.

Делитель 25 частоты делит частоту тактового генератора 1 и формирует на своих трех выходах три последовательности импульсов, с разным периодом ТК поступающие на мультиплексор 2b. Выбор серии импульсов на выходе мультиплексора 26 зависит от значения сигналов на его управляющих входах. Делитель 35 частоты делит входные импульсы на два. По переднему фронту каждого импульса с выхода мультиплексора 26 происходит синхронизация счетчиков делителя 25 частоты путем сброса их в (V. Данные от источника 21 информации записываются в параллельном коде в регистр 22. Строб сопровождения данных устанавливает в нуль счетчик 29„ Очередным задним фронтом импульса с выхода делителя 35 частоты D-триггер 27 устанавливается п состояние, разрешающее через элемент И 24 выполнение сдвига

5

0

5

0

5

0

5

0

5

в регистре 22 и счет числа переданных бит счетчиком 29. Кроме того, на управляющих входах мультиплексоров 26, 31 устанавливаются значения сигналов, обеспечивающие формирование импульсов длительностью Т1 и- Т2. Далее происходит сдвиг данных в регистре 22 по каждому заднему фронту импульсов с выхода делителя 35 частоты. В зависимости от значения очередного бита формируется импульс длительно стью Т1 или Т2. По окончании передачи поля данных происходит изменение значения сигнала на выходе дешифратора 30 (код, занесенный в счетчик 29, соответствует числу передаваемых бит в каждом поле данных) и установка D-триггера 27 в состояние, обеспечивающее передачу импульсов синхронизации длительностью ТЗ, прекращение сдвига информации в регистре 22 и счета числа импульсов счетчиком 29 Длительность паузы между формируемыми импульсами зависит от состояния D-триггера 200 Информация о готовности к приему с выхода элемента ИЛИ 9 записывается по каждому переднему фронту импульса Т1 с первого .выхода делителя 25 частоты и зависит от готовности устройства к приему Сброс 1 -триггера 20 выполняется по каждому переднему фронту импульса на выходе мультиплексора 26„ Задержка занесения информации о состоянии готовности к приему в D-триггер 20 на период импульса Т1 позволяет подготовиться за это время к приему данных с линии связи путем считывания потребителем информации из регистра 17 и передать в цикле формирования паузы между импульсами сигнал о готовности к приему. В результате повышается пропускная- способность устройства Сброс 1)-триггера 20 в конце каждого импульса в состояние, обеспечивающее формирование паузы, между импульсами длительностью Т2, необходим для устранения влияния на работу устройства переходных процессов. При формировании импульса синхронизации ТЗ передним фронтом импульса с третьего выхода делителя 25 частоты происходит синхронизация делителя 35 частоты для привязки уров-- ня сигнала (высокий уровень - данные и синхронизация, низкий уровень - сигналы квитирования)„ Благодаря делителю 35 частоты на два по каждому

импульсу, сформированному на выходе мультиплексора 26, происходит изменение уровня сигнала на выходе устройства на противоположное.

Выбор длительностей формируемых на выходе делителя 35 частоты уровней сигналов осуществляется с помощью мультиплексоров 31 и элемента И 23. При первом (высоком) уровне сигнала на выходе делителя 35 частоты мультиплексор 31 и элемент И 23 обеспечивают формирование пауз на выходе мультиплексора 26 длительностью Т1, Т2, ТЗ. При втором (низком) уровне сигнала на выходе делителя 35 частоты с помощью элемента И 23 обеспечивается формирование пауз длительностью Т1 и Т2. Причем мультиплексор 31 определяет источник информации (сдви- говый регистр 22 или D-триггер 20), а элемент И 23 блокирует формирование пауз с длительностью ТЗ при втором (низком) уровне сигнала на выходе устройства.

Входной аналоговый сигнал из линии связи через усилитель 2, фильтр 3 нижних частот и формирователь 4 пря- моугольных импульсов поступает на блоки 5,17,19,32,33 С помощью блоков 32,33 по каждому фронту импульса с выхода формирователя 4 формируются короткие импульсы, длительность кото- рых определяется задержкой сигнала в блоке 32„ Эти импульсы поступающие на установочный входы счетчика 11 и триггеров 13,15, выполняют их сброс О. В промежутке времени между им- пульсами происходит измерение длительности паузы с помощью счетчика 11 путем подсчета импульсов с выхода тактового генератора 1. В зависимости от длительности паузы между импульса- ми с помощью дешифраторов 12 устанав ливаются в 1 триггеры 13, 15. Если пауза между импульсами на выходе эле мента ИСКЛЮЧАЮЩЕЕ ИЛИ 33-ТЗ, то оба триггера устанавливаются в 1, при Т2 - триггер 13. По заднему фронту входного импульса происходит сдвиг данных в регистре 17 Необходимая за- держка обеспечивается блоком 14 задержки. Одновременно происходит счет числа принятых бит счетчиком 5. Если принят хотя бы один бит, то сигналом с выхода дешифратора 6 устанавливает ся в 1 RS-триггер 7, что означает Приемник занят. После приема всего поля данных с известным фиксированным

числом бит изменяется состояние триггера 8, что через элемент ИЛИ 34 приводит к установке в исходное состояние RS-триггера 7. С помощью элемента ИЛИ 9 формируется сигнал К приему не готов, поступающий на информационный вход U-триггера 20. Он запоминается по фронту импульса Т1, поступающего на тактовый вход D- триггера 20„ Сигнал Буфер заполнен с выхода триггера 8 через блок 10 задержки поступает на вход регистра 17, запрещая сдвиг в нем„ Одновременно -он поступает в блок 18 потребителя информации. После считывания данных из регистра 17 блок 18 устанавливает триггер 8 в исходное состояние. При поступлении импульсов синхронизации длительностью ТЗ выполняется установ - ка в исходное состояние RS-триггера 7 и счетчика 5 числа принятых бит Необходимая задержка сигналов синхронизации обеспечивается блоком 16 задержки. По переднему фронту входных импульсов происходит занесение сигна- ла готовности к приему из RS-триггера 13 в D-триггер 19. .Последнее выполня- ется лишь при отсутствии сигнала на установочном входе 1)-триггера 19 и соответствует завершению передачи данньЕХ. В результате, если источник 21 информации осуществил занесение данных для передачи в регистр 22, то происходит сброс второго I)-триггера 19 и продолжается передача данных

При рассмотрении работы устройства необходимо учитывать естественные за1 держки сигнала в каждом блоке.

Таким образом, предлагаемое устрой ство благодаря передаче сигналов кви- тированием во время паузы между пульсами и изменению длительности па- узы в процессе ее формирования право 4 ляет увеличить пропускную способность.

Формула изобретения

Устройство для приема и передачи цифровой двоичной информации, содер - жащее последовательно соединенные усилитель, фильтр нижних частот, формирователь прямоугольных импульсов, первый счетчик, первый дешифратор, первый RS-триггер, первый элемент ИЛИ, первый D-триггер, последовательно соединенные тактовый генератор, рой счетчик и второй дешифратор, пер вый выход которого через последова-

тельно соединенные второй RS-триггер и первый блок задержки соединен с первым входом первого регистра сдвига, выход которого соединен с первым входом блока потребителя информации, выход которого соединен с первым вхо- дом триггера Буфер заполнен, второй вход и выход которого соединены ветственно с вторым выходом первого дешифратора и вторым входом первого элемента ИЛИ, второй выход второго дешифратора через последовательно соединенные третий RS-триггер и вто- рой блок задержки соединен с вторым входом первого счетчика и первым вхо- дом второго элемента KJIK, второй вход второго счетчика соединен с вторыми входами второго и третьего RS-тригге- ров, выход формирователя прямоуголь- ных импульсов соединен с вторым вхо- дом первого регистра сдвига, третий вход которого соединен с выходом третьего блока задержки, подключенным к второму входу блока потребителя ин- формации, вход третьего блока задерж- ки соединен с выходом триггера Буфер заполнен, последовательно соединен- ные первый элемент И, третий счетчик, третий дешифратор, второй D-триггер и четвертый блок задержки, первый выход источника информации соединен с первым входом второго регистра сдвига, второй вход которого и вто - рой вход третьего счетчика соединены с вторым выходом источника информации, выход тактового генератора соединен с первым входом первого делителя час- тоты, первый, второй, третий выходы которого соединены соответственно с первым, вторым, третьим входами пер- вого мультиплексора, первый вход первого элемента И соединен с выходом, четвертого блока задержки, выход третьего дешифратора соединен с вым входом третьего D-триггера, выход первого элемента И соединен с третьим входом второго регистра сдви- га, выход которого соединен с первым

20

25

вход и выход которо ветственно с выходо гера и четвертым вх типлексора, второй мента ИЛИ соединен Буфер заполнен вы мента ИЛИ соединен первого RS-триггера

... Элемент И, пятый бл чем вход усилителя устройства, отли тем, что, с целью у ной способности при

15 информации, введены частоты и элемент И первый и второй вхо ключены соответстве мирователя прямоуго и пятого блока заде соединен с вторым в счетчика, вход пято соединен с вторым в D-триггера и подклю мирователя прямоуго выход первого мульт нен с первым входом частоты, выход кото первым входом второ

30 первым входом второ вторым входом второ вторым входом перво второй вход второго ключен к выходу чет держки, а выход под входу первого мульт выход первого делит ключен к второму вх теля частоты, выход гера подключен к вх информации, выход п сора соединен с вто делителя частоты и первого D-триггера

Af рого соединен с пер го делителя частоты третьего D-триггера ду первого блока за второго делителя ча

35

40

входом второго мультиплексора, второй выходом устройства .

Редактор С.Патрушева

I

Составитель Н.Лазарева Техред М.Моргентал

Корректор А.О

0

5

вход и выход которого соединены COOT- ветственно с выходом первого D-триг- гера и четвертым входом первого мультиплексора, второй вход второго элемента ИЛИ соединен с выходом триггера Буфер заполнен выход второго элемента ИЛИ соединен с вторым входом первого RS-триггера, а также второй

.. Элемент И, пятый блок задержки, при чем вход усилителя является входом устройства, отличающееся тем, что, с целью увеличения пропуск ной способности при обмене цифровой

5 информации, введены второй делитель частоты и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого подключены соответственно к выходу формирователя прямоугольных импульсов и пятого блока задержки, а выход соединен с вторым входом второго счетчика, вход пятого блока задержки соединен с вторым входом третьего D-триггера и подключен к выходу формирователя прямоугольных импульсов, выход первого мультиплексора соединен с первым входом второго делителя частоты, выход которого соединен с первым входом второго мультиплексора,

0 первым входом второго элемента И, вторым входом второго D-триггера и вторым входом первого элемента И, второй вход второго элемента И подключен к выходу четвертого блока задержки, а выход подключен к пятому входу первого мультиплексора, третий выход первого делителя частоты подключен к второму входу второго делителя частоты, выход третьего D-триг; гера подключен к входу источника информации, выход первого мультиплексора соединен с вторым входом первого делителя частоты и вторым входом первого D-триггера, третий вход котоf рого соединен с первым выходом первого делителя частоты, третий вход третьего D-триггера подключен к выходу первого блока задержки, а выход второго делителя частоты является

5

0

Корректор А.Осауленко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема данных | 1989 |

|

SU1721836A2 |

| Устройство для передачи и приема данных | 1989 |

|

SU1665529A1 |

| Устройство для последовательного обмена данными с квитированием | 1989 |

|

SU1720164A1 |

| Устройство для передачи информации | 1990 |

|

SU1753615A1 |

| Устройство для приема и передачи двоичной информации | 1984 |

|

SU1748275A1 |

| Устройство для приема и передачи данных | 1989 |

|

SU1688438A1 |

| Устройство для передачи и приема данных в полудуплексном режиме | 1990 |

|

SU1732485A1 |

| Устройство для приема и передачи данных в дуплексном режиме | 1987 |

|

SU1506576A1 |

| Устройство для передачи и приема информации | 1990 |

|

SU1748276A1 |

| Устройство для приема данных | 1990 |

|

SU1837347A1 |

Изобретение относится к радио- технике. Цель изобретения - увели-1 чение пропускной способности при мене цифровой информации„ Устройство содержит- тактовый генератор 1, усили - тель 2, фильтр 3 нижних частот, фор- мирователь 4 прямоугольных импульсов, счетчики 5, 11, 29, дешифраторы 6, 12, 30, RS-триггеры 7 13, 15, триггер 8$ Буфер заполнен, элементы ИЛИ 9, 34, блоки задержки 14, 16, 10, 28, 32, регистры 17,22 сдвига, блок 18 потребителя информации D-триггеры 20, 27, 19, источник 21 информации, элементы И 23, 24, делители 25, 35, частоты, мультиплексоры 26, 31, эле мент ИСКЛЮЧАЮЩЕЕ ИЛИ 33. Изобретение благодаря передаче сигналов квитиро ванием во время паузы между импульса - ми и изменению длительности паузы в процессе ее формирования позволяет увеличить пропускную способность. 1 ил. о Ј (Л с о о 00 4J 00

| Авторское свидетельство СССР № 1608817, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-11-23—Публикация

1989-10-25—Подача