Изобретение относится к области последовательной передачи цифровых данных в полудуплексном режиме методом широт- ноимпульсной манипуляции.

Известно устройство для последовательной передачи и приема данных в стандарте RS-232C, в котором входной параллельный код преобразовывают в последовательные импульсы одинаковой длительности. Количество импульсов и их величина определяется числом и значением передаваемых бит информации. Для синхронизации приемника с передатчиком передают дополнительные импульсы синхронизации - стартовый и стоповый. Устройство содержит первый и второй сдвиго- вые регистры, счетчики принятых и переданных бит, тактовый генератор, логику управления.

Недостатком известного устройства является то, что при работе в полудуплексном режиме передачу информации выполняют только после завершения приема сообщения, иначе из-за одновременной работы

двух передатчиков возможно искажение принимаемой информации.

Наиболее близким по технической сущности является устройство для передачи и приема данных, содержащее последовательно соединенные усилитель, фильтрат, формирователь прямоугольных импульсов, последовательно соединенные первый счетчик, первый дешифратор, первый блок задержки, последовательно соединенные тактовый генератор, второй счетчик, второй дешифратор, последовательно соединенные первый RS-триггер, второй блок задержки и первый регистр сдвига, последовательно соединенные второй Р- триггер, третий блок задержки и первый де- литель частоты, последовательно соединенные источник информации и второй регистр сдвига, последовательно соединенные второй элемент И, третий счетчик, третий дешифратор, D-триггер и четвертый блок задержки, последовательно соединенные второй формирователь коротких импульсов, второй делитель частоты,

СО

С

vj

со

hO 4 СО

ел

мультиплексор и коммутатор, первый элемент И, первый вход и выход которого сое- динены соответственно с выходом тактового генератора и вторым входом второго делителя частоты, первый и второй входы блока потребителя информации соединены соответственно к выходам первого блока задержки и первого регистра сдвига, вторые входы второго счетчика, первого и второго RS-триггеров, первого регистра сдвига соединены с первым входом первого счетчика, второй вход которого соединен с выходом первого делителя частоты, выход коммутатора и вход усилителя соединены с линией связи, первый и второй выходы второго дешифратора соединены соответственное первыми входами первого и второго RS-триггеров, выходы строба сопровождения данных источника информации соединен с вторыми входоми третьего счетчика и второго регистра сдвига, выход которого соединен с первым управляющим входом мультиплексора, выход второго элемента И соединен с третьим входом второго регистра сдвига, выход четвертого блока задержки соединен с вторыми входами мультиплексора и второго элемента И, первый вход которого соединен с выходом мультиплексора, третий вход D-триггера соединен с общей шиной, выход третьего дешифратора соединен с входом источника информации, а выход первого делителя частоты соединен с вторыми входами коммутатора и первого элемента И.

Недостатком известного устройства является сложность, низкая пропускная способность и низкая достоверность приема. Сложность устройства вызвана использованием блока контроля на базе счетчика, разрядность которого значительно превышает разрядность счетчика, используемого для измерения длительности импульсов. Низкая пропускная способность связана с боль- шим временем ожидания появления импульсов синхронизации при перерыве в связи. Низкая достоверность приема связана с передачей информации еще до установления связи с удаленным абонентом при периодической передаче импульсов синхронизации по сигналу блока контроля связи.

Целью изобретения является повышение пропускной способности и достоверности приема.

Поставленная цель достигается тем, что в устройство для передачи и приема данных в полудуплексном режиме, содержащее последовательно соединенные усилитель, фильтр, формирователь прямоугольных импульсов, последовательно соединенные

первый счетчик, первый дешифратор, первый блок задержки, последовательно соединенные тактовый генератор, второй счетчик, второй дешифратор, последовательно соединенные первый RS-триггер, второй блок задержки и первый регистр сдвига, последовательно соединенные второй RS-триггер, третий блок задержки и первый делитель частоты, последовательно соеди0 ненные источник информации и второй регистр сдвига, последовательно соединенные второй элемент И, третий счетчик, третий дешифратор, D-триггер и четвертый блок задержки, последовательно

5 соединенные второй формирователь коротких импульсов, второй делитель частоты, мультиплексор и коммутатор, первый элемент И, первый вход и выход которого соединены соответственно с выходом

0 тактового генератора и вторым входом второго делителя частоты, первый и второй входы потребителя информации соединены соответственно к выходам первого блока задержки и первого регистра сдвига, вторые

5 входы второго счетчика, первого и второго RS-триггеров, первого регистра сдвига соединены с первым входом первого счетчика, второй вход которого соединен с выходом первого делителя частоты, выход коммута0 тора и вход усилителя соединены с линией связи, первый и второй выходы второго дешифратора соединены соответственно с первыми входами первого и второго RS5 триггеров, выход строба сопровождения данных источника информации соединен с вторыми входами третьего счетчика и второго регистра сдвига, выход которого соединен с первым управляющим входом

0 мультиплексора, выход второго элемента И соединен с третьим входом второго регистра сдвига, выход четвертого блока задержки соединен с вторыми входами мультиплексора и второго элемента И, первый вход кото5 рого соединен с выходом мультиплексора, третий вход D-триггера соединен с общей шиной, выход третьего дешифратора соединен с входом источника информации, а выход первого делителя частоты соединен с

0 вторыми входами коммутатора и первого элемента И, введены последовательно соединенные третий элемент И, третий RS- триггер и четвертый элемент И, выход которого соединен с вторым входом D-триг5 гера, выход формирователя прямоугольных импульсов соединен с входом первого формирователя короткого импульса, Bt ход которого соединен с первым входом первого счетчика, третий выход второго дешифратора соединен с установочным входом перво- го делителя частоты и вторым входом

третьего RS-триггера, выход третьего блока задержки соединен с вторым входом третьего элемента И, выход мультиплексора соединен с вторым входом четвертого элемента И.

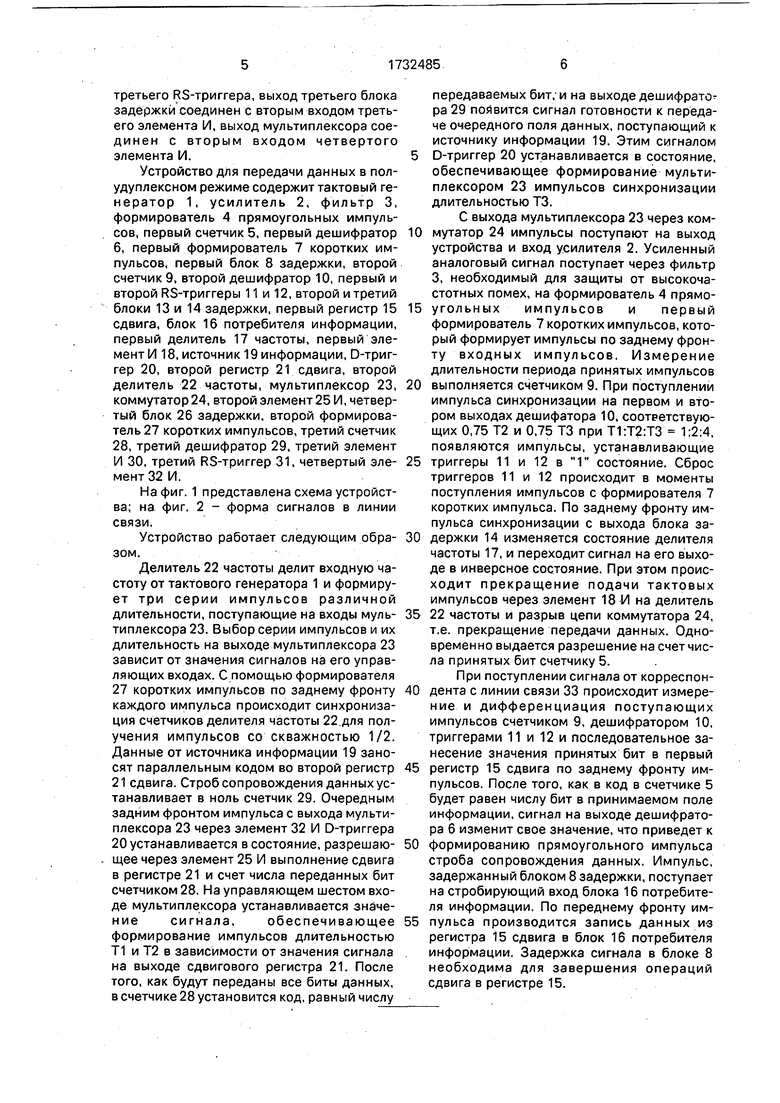

Устройство для передачи данных в полудуплексном режиме содержит тактовый ге- нератор 1. усилитель 2, фильтр 3, формирователь 4 прямоугольных импульсов, первый счетчик 5, первый дешифратор 6, первый формирователь 7 коротких импульсов, первый блок 8 задержки, второй счетчик 9, второй дешифратор 10, первый и второй RS-триггеры 11 и 12, второй и третий блоки 13 и 14 задержки, первый регистр 15 сдвига, блок 16 потребителя информации, первый делитель 17 частоты, первый элемент И 18, источник 19 информации, D-триг- гер 20, второй регистр 21 сдвига, второй делитель 22 частоты, мультиплексор 23, коммутатор 24, второй элемент 25 И, четвертый блок 26 задержки, второй формирователь 27 коротких импульсов, третий счетчик 28, третий дешифратор 29, третий элемент И 30, третий RS-триггер 31, четвертый элемент 32 И.

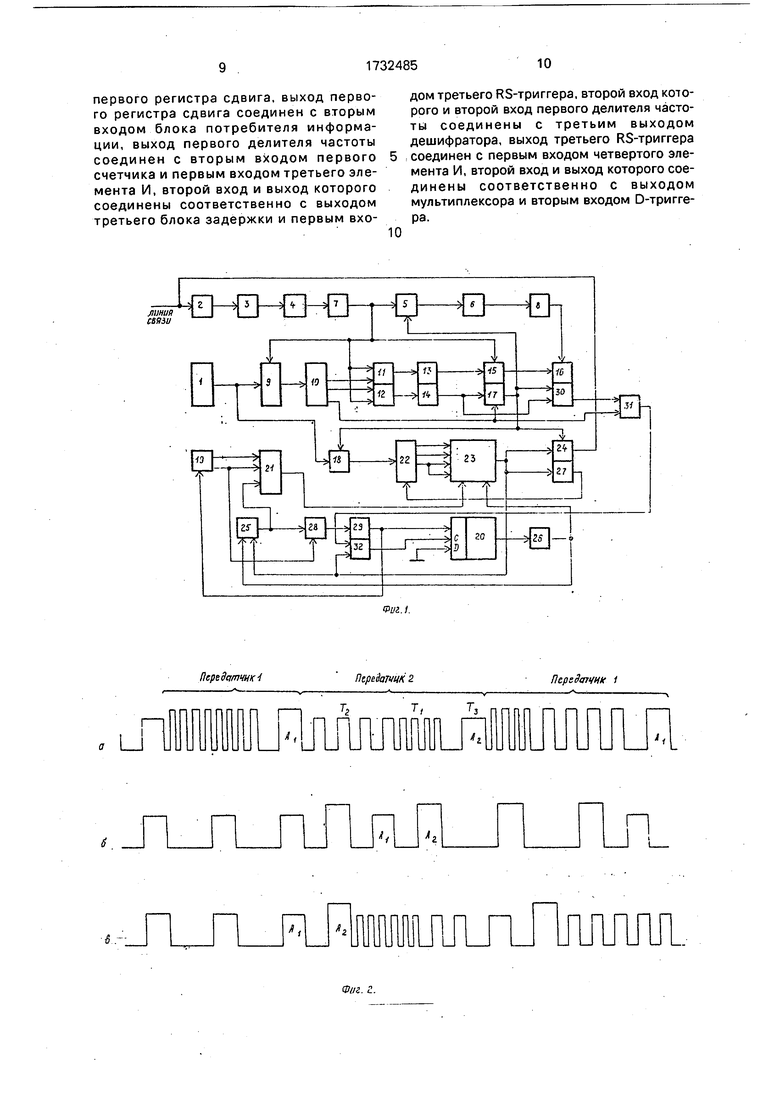

На фиг. 1 представлена схема устройства; на фиг. 2 - форма сигналов в линии связи.

Устройство работает следующим образом.

Делитель 22 частоты делит входную частоту от тактового генератора 1 и формирует три серии импульсов различной длительности, поступающие на входы мультиплексора 23. Выбор серии импульсов и их длительность на выходе мультиплексора 23 зависит от значения сигналов на его управляющих входах. С помощью формирователя 27 коротких импульсов по заднему фронту каждого импульса происходит синхронизация счетчиков делителя частоты 22 для получения импульсов со скважностью 1/2. Данные от источника информации 19 заносят параллельным кодом во второй регистр 21 сдвига. Строб сопровождения данных устанавливает в ноль счетчик 29. Очередным задним фронтом импульса с выхода мультиплексора 23 через элемент 32 И D-триггера 2 0 уста на вливается в состояние, разрешающее через элемент 25 И выполнение сдвига в регистре 21 и счет числа переданных бит счетчиком 28. На управляющем шестом входе мультиплексора устанавливается значение сигнала, обеспечивающее формирование импульсов длительностью Т1 и Т2 в зависимости от значения сигнала на выходе сдвигового регистра 21. После того, как будут переданы все биты данных, в счетчике 28 установится код, равный числу

передаваемых бит, и на выходе дешифратора 29 появится сигнал готовности к передаче очередного поля данных, поступающий к источнику информации 19. Этим сигналом

D-триггер 20 устанавливается в состояние, обеспечивающее формирование мультиплексором 23 импульсов синхронизации длительностью ТЗ.

С выхода мультиплексора 23 через коммутатор 24 импульсы поступают на выход устройства и вход усилителя 2. Усиленный аналоговый сигнал поступает через фильтр 3, необходимый для защиты от высокочастотных помех, на формирователь 4 прямоугольных импульсов и первый формирователь 7 коротких импульсов, который формирует импульсы по заднему фронту входных импульсов. Измерение длительности периода принятых импульсов

выполняется счетчиком 9. При поступлении импульса синхронизации на первом и втором выходах дешифатора 10, соответствующих 0,75 Т2 и 0,75 ТЗ при Т1:Т2:ТЗ 1:2:4, появляются импульсы, устанавливающие

триггеры 11 и 12 в 1 состояние. Сброс триггеров 11 и 12 происходит в моменты поступления импульсов с формирователя 7 коротких импульса. По заднему фронту импульса синхронизации с выхода блока задержки 14 изменяется состояние делителя частоты 17, и переходит сигнал на его выходе в инверсное состояние. При этом происходит прекращение подачи тактовых импульсов через элемент 18 И на делитель

22 частоты и разрыв цепи коммутатора 24, т.е. прекращение передачи данных. Одновременно выдается разрешение на счет числа принятых бит счетчику 5.

При поступлении сигнала от корреспондента с линии связи 33 происходит измерение и дифференциация поступающих импульсов счетчиком 9, дешифратором 10, триггерами 11 и 12 и последовательное занесение значения принятых бит в первый

регистр 15 сдвига по заднему фронту импульсов. После того, как в код в счетчике 5 будет равен числу бит в принимаемом поле информации, сигнал на выходе дешифратора 6 изменит свое значение, что приведет к

формированию прямоугольного импульса строба сопровождения данных. Импульс, задержанный блоком 8 задержки, поступает на стробирующий вход блока 16 потребителя информации. По переднему фронту импульса производится запись данных и-з регистра 15 сдвига в блок 16 потребителя информации. Задержка сигнала в блоке 8 необходима для завершения операций сдвига в регистре 15.

Далее прием ведется до поступления импульса синхронизации от корреспондента с линии связи 32. По этому импульсу происходит очередное изменение состояния делителя частоты 17, приводящее к запрещению счета числа принятых бит счетчиком 5 и установке в ноль счетчика 5, подаче тактовых импульсов на делитель 22 частоты и к замыканию цепей в коммутаторе 24, т.е. к продолжению передачи данных.

При отсутствии сигналов от корреспондента при начальном вхождении в связь или при нарушении связи сигнал с третьего выхода второго дешифратора 10 через время большее, чем необходимо для передачи импульса синхронизации с паузой (ЗТЗ), поступает на установочный вход делителя частоты 17 и переводит устройство в режим передачи. Одновременно он устанавливает в О RS-триггер 31. В этом случае в режиме передачи и при наличии данных к передаче в регистре 21 не происходит изменение состояния D-триггера 20 по заднему фронту импульса с выхода мультиплексора 23 до получения импульса синхронизации от корреспондента. В режиме приема импульсом синхронизации через элемент 30 и RS-триггер 31 устанавливается в 1 состояние. Благодаря наличию элемента 30 И это выполняется только в режиме приема. Поэтому данные не могут быть переданы устройством до получения импульсов синхронизации от корреспондента, свидетельствующих об установлении связи, что повышает достоверность приема.

На фиг. 2а показана форма сигналов в линии связи при передаче информации байт за байтом. Импульсы с амплитудой А1 относятся к первому устройству для передачи данных, А2 - к второму. Разница амплитуд связана с затуханием сигнала в линии связи.

На фиг. 26 показана форма сигналов при отсутствии информации у обоих источников и при вхождении в связь, на фиг. 2в - при передаче информации после вхождения в связь. В этом случае устройство передает только импульсы синхронизации с длительностью ТЗ с амплитудой А1 до получения ответного импульса с длительностью ТЗ и амплитудой А2, после чего начинает передавать данные.

Таким образом, предлагаемое устройство для передачи и приема данных в полудуплексном режиме обладает более высокой пропускной способностью, а также повышенной достоверностью приема в условиях частых перерывов в связи.

Формула изобретения Устройство для передачи и приема данных в полудуплексном режиме, содержащее первый формирователь коротких импульсов,

последовательно соединенные усилитель, фильтр и формирователь прямоугольных импульсов, первый счетчик, выход которого соединен с входом первого дешифратора, выход первого блока задержки соединен с первым

0 входом блока потребителя информации, по следовательно соединенные тактовый генераотр, второй счетчик, второй дешифратор,

первый RS-триггер, второй блок задержки и

первый регистр сдвига, второй выход дешиф5 ратора через последовательно соединенные второй RS-триггер, третий блок задержки и первый делитель частоты соединен с первым входом первого элемента И, второй вход которого соединен с выходом тактового ге0 нератора, выход первого элемента И соединен с первым входом второго делителя частоты, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами мультиплек5 сора, четвертый вход которого соединен с третьим выходом второго делителя частоты, второй вход которого соединен с выходом второго формирователя коротких импульсов, вход которого, первый вход коммутато0 ра и первый вход второго элемента И соединены с выходом мультиплексора, первый и второй выходы источника информации соединены соответственно с первым и вторым входами второго регистра сдвига,

5 третий вход и выход которого соединены соответственно с выходом второго элемента И и пятым входом мультиплексора, шестой вход которого и второй вход второго элемента И соединены с выходом четверто0 го блока задержки, вход которого соединен с выходом D-триггера, выход второго элемента И через последовательно соединенные третий счетчик и третий дешифратор соединен с первым входом D-триггера, вы5 ход третьего дешифратора соединен с входом источника информации, выход первого делителя частоты соединен с вторым входом коммутатора, выход которого соединен с входом усилителя, второй выход источника

0 информации соединен с вторым входом третьего счетчика, отличающееся тем, что, с целью повышения пропускной способности и достоверности приема, введены третий и четвертый элементы И и третий RS

5 триггер, причем выход формирователя пря- моугольных импульсов через первый формирователь коротких импульсов соединен с первым входом первого счетчика, вторым входом второго счетчика, вторыми входами первого,, второго RS-триггеров и

первого регистра сдвига, выход первого регистра сдвига соединен с вторым входом блока потребителя информации, выход первого делителя частоты соединен с вторым входом первого счетчика и первым входом третьего элемента I/I, второй вход и выход которого соединены соответственно с выходом третьего блока задержки и первым вхо0

дом третьего RS-триггера, второй вход которого и второй вход первого делителя частоты соединены с третьим выходом дешифратора, выход третьего RS-триггера соединен с первым входом четвертого элемента И, второй вход и выход которого соединены соответственно с выходом мультиплексора и вторым входом D-тригге- ра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема данных | 1987 |

|

SU1510105A1 |

| Устройство для передачи и приема информации | 1990 |

|

SU1748276A1 |

| Устройство для последовательного обмена данными с квитированием | 1989 |

|

SU1720164A1 |

| Устройство для передачи информации | 1990 |

|

SU1753615A1 |

| Устройство для передачи и приема данных | 1989 |

|

SU1665529A1 |

| Устройство для приема и передачи данных в дуплексном режиме | 1987 |

|

SU1506576A1 |

| Устройство для приема и передачи данных | 1989 |

|

SU1688438A1 |

| Устройство для приема и передачи двоичной информации | 1984 |

|

SU1748275A1 |

| Устройство для передачи и приема двоичной информации | 1989 |

|

SU1688439A1 |

| Устройство для передачи и приема данных | 1989 |

|

SU1721836A2 |

Изобретение относится к технике связи и может использоваться при построении приемо-передатчиков широтно-импульсной манипуляции. Целью изобретения является повышение пропускной способности и достоверности приема. Для этого устройство содержит приемник и передатчик широтно- импульсной манипуляции и делитель частоты, управляющий режимом работы. В устройство введены два элемента И и RS- триггер, которые задерживают передачу данных до установления связи. 2 ил.

41}

ю

Передатчик-I

LJ

н

JU

и

т

к

ft

п

Передатчик 2

Передспчик i

Г,

| Устройство для передачи и приема данных | 1987 |

|

SU1510105A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-05-07—Публикация

1990-04-02—Подача