Изобретение относится к технике связи и может использоваться при построении приемопередатчиков широтно-импульсной манипуляции.

Известно устройство для приема и пере- дачи данных в дуплексном режиме, состоящее из тактового генератора, последовательно включенных входного усилителя, фильтра нижних частот и. формирователя прямоугольных имп у Ль ов, счетчика принятых бит, дешифратора числа принятых бит, D- триггера Буфёр зап Ы йе« С первым элементом задержки, сч15тч и ка тактовых импульсов, дешифратора длительности входных импульсов, RS-триггеров значения бита и синхронизации второго и третьего элементов задержки, первого и второго сдвиговых регистров, пеового элемента И, делителя частоты, мультиплексора на четыре направления, формирователя короткого импульса, счетчика числа переданных бит, дешифратора числа переданных бит, D- триггера формирования импульса синхронизации, четвертого элемента задержки. .

Недостатком известного устройства яв- ляется пропорциональное увеличение сложности и числа линий связи при увеличении числа связанных между собой в одном направлении источников и потребителей информации.

Наиболее близким по технической сущности является устройство для передачи и приема данных, содержащее последовательно соединенные тактовый генератор, первый делитель частоты, первый мульти- плексор и формирователь короткого импульса, N блоков управления, N блоков потребителей информации, последовательно соединенные второй делитель частоты и первый элемент И, последовательно соеди- ненные усилитель, фильтр нижних частот, пороговый элемент, первый счетчик, первый-дешифратор и первый блок задержки, последовательно соединенные второй счетчик, второй дешифратор, первый триггер, второй блок задержки, регистр сдвига, последовательно соединенный элемент ИЛИ, четвертый блок задержки и второй элемент И, последовательно соединенные второй триггер и третий блок задеужки, выход ко- торого подключен к второму входу первого счетчика и второму входу второго элемента И, второй выход второго дешифратора соединен с первым входом второго триггера, выход порогового элементу соединен с пер- вым входом второго счетчика, с вторыми входами первого, второго триггеров и регистра сдвига, второй и третий выходы первого дешифратора соединены соответственно с первым и вторым входами элемента ИЛИ,

выход тактового генератора соединен с вторым входом второго счетчика, выход формирователя короткого импульса - с вторым входом первого делителя частоты. Вход усилителя является входом устройства, а выход первого мультиплексора - выходом устройства. Выход первого элемента И соединен с третьим управляющим входом первого мультиплексора, первый вход второго делителя частоты соединен с выходом первого мультиплексора.

В указанном устройстве блок управления содержит последовательно соединенные элемент И, счетчик, дешифратор, D-триггер и блок задержки, последовательно соединенные блок-источник информации и регистр сдвига, второй выход блока-источника информации соединен с вторыми входами регистра сдвига и счетчика, первый вход элемента И соединен с тактовым входом D-триггера и является входом блока управления, выход элемента И соеди- нен-с третьим входом регистра сдвига, выход которого является первым выходом .блока управления, а выход блока задержки соединен с вторым входом элемента И и является вторым Е ЫХОДОМ блока управления, информационный вход D-триггера соединен с общей шиной.

Недостатком известного устройства является пропорционс)льное увеличение сложности и числа линий связи при увеличении числа связанных между собой в одном направлении источников и потребителей информации.

Цель изобретения - увеличение пропускной способности.

Поставленная цель достигается тем, что в устройство для передачи и приема данных, содержащее последовательно соединенные усилитель, фильтр нижних частот, формирователь прямоугольных импульсов, первый счетчик и первый дешифратор, последовательно соединенные тактовый генератор, второй счетчик, второй дешифратор, первый триггер и первый блок задержки, выход которого соединен с вторым входом первого счетчика, второй выход второго дешифратора через последовательно соединенные второй триггер и второй блок задержки соединен с.первым входом регистра сдвига, выход тактового генератора соединен с первым входом первого делителя частоты, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами первого мультиплексора, выход которого является выходом устройства и через формирователь коротких импульсов соединен с вторым входом первого делителя частоты, выход второго делителя частоты соединен с первым входом первого элемента И, а также элемент ИЛИ, третий, четвертый блоки задержки, второй элемент И, первый блок управления, второй мультиплексор, введены, третий и четвертый счетчики, первый, второй коммутаторы, третий дешифратор и второй блок управления, причем первый выход первого дешифратора соединен с первым входом элемента ИЛИ, а второй и третий выходы - соответственно с входом третьего блока задержки и вторым входом элемента ИЛИ, выход которого через четвертый блок задержки соединен с первым входом второго элемента И, выход которого соединен с первым входом третьего счетчика, второй вход которого и второй вход второго элемента И соединены с выходом первого блока задержки, выход формирователя прямоугольных импульсов соединен с вторыми входами второго счетчика, первого и второго триггеров и регистра сдвига, выход третьего блока задержки - с первым входом коммутатора, второй вход которого соединен с выходом регистра сдвига, выход третьего счетчика - с третьим входом первого коммутатора, выходы которого соединены с входами блоков потребителей информации, третий выход первого делителя частоты через четвертый счетчик соединен с первыми входами второго мультиплексора и второго коммутатора и входом третьего дешифратора, выход которого соединен с вторым входом первого элемента И, выход которого соединен с четвертым входом первого мультиплексора, выход которого соединен с первым входом второго делителя частоты и вторым входом второго коммутатора, выходы которого соединены с входами блоков управления, выходы которых соединены с соответствующими входами второго мультиплексора, первый и второй выходы которого соединены соответственно с пятым и шестым входами первого мультиплексора, второй выход второго мультиплексора соединен с вторым входом второго делителя частоты.

Блок управления содержит последовательно соединенные элемент И, счетчик, дешифратор, D-триггер и блок задержки, последовательно соединенные блок источник информации и регистр сдвига, второй выход блока источника информации соединен с вторыми входами регистра сдвига и счетчика, первый вход элемента И соединен с тактовым входом D-триггера и является входом блока управления, выход элемента И соединен с третьим входом регистра сдвига, выход которого является первым выходом блока управления, а выход блока задержки соединен с вторым входом

элемента И и является вторым выходом блока управления, информационный вход D- триггера соединен с общей шиной,

Решение обладает новизной и существенными отличиями, так как в известных источниках не обнаружено устройство, которое содержало бы третий и четвертый счетчики, первый, второй коммутаторы, третий дешифратор и второй блок управления,

0 причем первый выход первого дешифратора соединен с первым входом элемента ИЛИ, а второй и третий выходы - соответственно с входом третьего блока задержки и вторым входом элемента ИЛИ, выход кото5 рого через четвертый блок задержки соединен с первым входом второго элемента И, выход которого соединен с первым входом третьего счетчика, второй вход которого и второй вход второго элемента И соединены

0 с выходом первого блока задержки, выход формирователя прямоугольных импульсов соединен с вторыми входами второго счетчика,первого и второго триггеров и регистра сдвига, выход третьего блока задержки сое5 динен с первым входом коммутатора, второй вход которого соединен с выходом регистра сдвига, выход третьего счетчика соединен с третьим входом первого коммутатора, выходы которого соединены с входа0 ми блоков потребителей информации, третий выход первого делителя частоты через четвертый счетчик соединен с первыми входами второго мультиплексора и второго коммутатора и входом третьего дешифрато5 ра, выход которого соединен с вторым входом первого элемента И, выход которого соединен с четвертым входом первого мультиплексора, выход которого.соединен с первым входом второго делителя частоты и

0 вторым входом второго коммутатора, выходы которого соединены с входами блоков управления, выходы которых соединены с соответствующими входами второго мультиплексора, первый и второй выходы кото5 рого соединены соответственно с пятым и шестым входами первого мультиплексора, второй выход второго мультиплексора соединен с вторым входом второго делителя частоты.

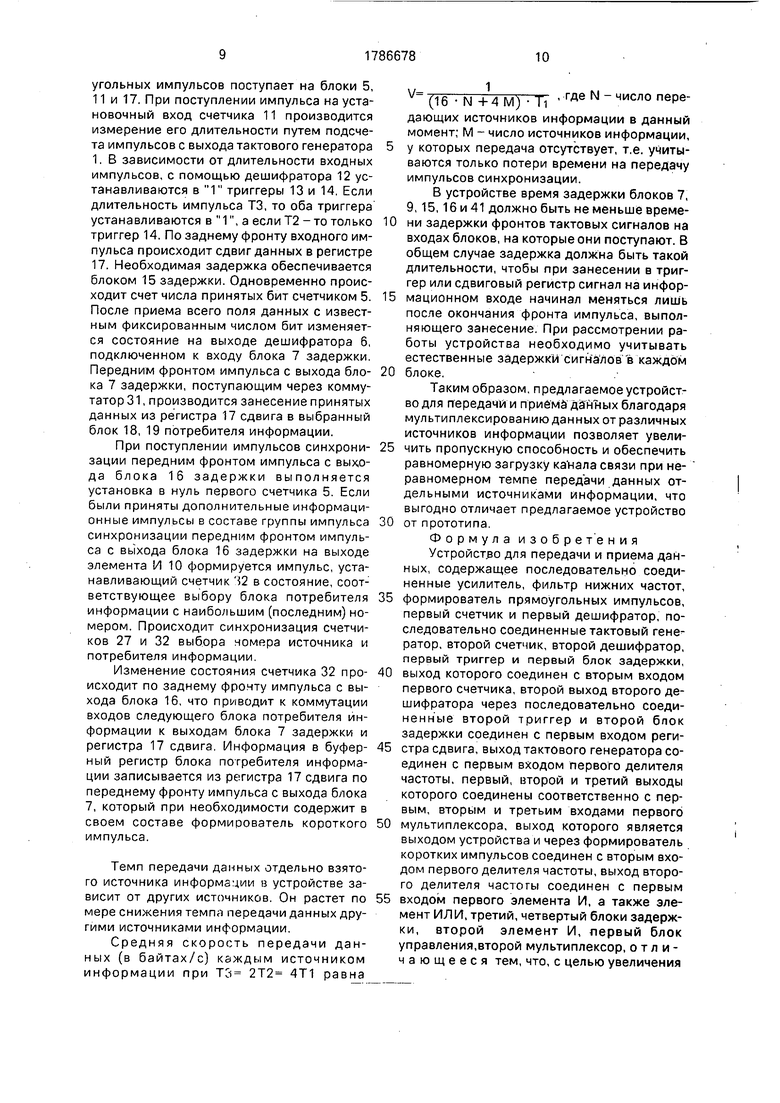

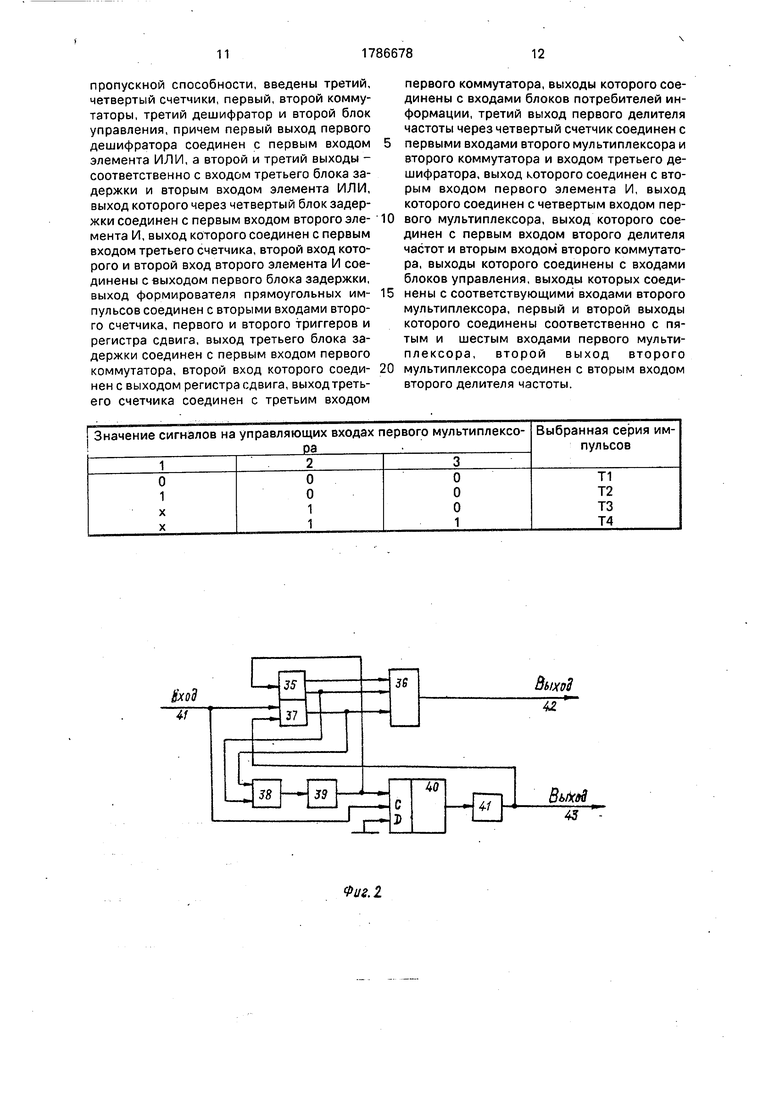

0На фиг. 1 дана структурная электрическая схема устройства; на фиг. 2 - структурная электрическая схема блока управления; на фиг. 3 - временные диаграммы на выходе устройства.

5Устройство для передачи и приема данных содержит тактовый генератор 1, входной усилитель 2, фильтр 3 нижних частот, формирователь 4 прямоугольных импульсов, первый счетчик 5, первый дешифратор 6, третий блок 7 задержки, элемент 8 ИЛИ,

четвертый блок 9 задержки, второй элемент И 10, второй счетчик 11, второй дешифратор 12, первый 13 и второй 14 триггеры, первый 15 и второй 16 блоки задержки, регистр 17 сдвига, первый 18 и второй 19 блоки потре- бители информации, первый делитель 20 частоты, первый мультиплексор 21, формирователь 22 короткого импульса, второй делитель 23 частоты, первый элемент И 24, первый блок 25 управления, а также вто- рой блок 26 управления, третий счетчик 27, второй мультиплексор 28, третий дешифратор 29, первый коммутатор 30, второй коммутатор 31, четвертый счетчик 32, вход 33 устройства и выход 34 устройства.

Блок управления содержит блок 35 источника данных, регистр 36 сдвига, элемент И 37, счетчик 38, дешифратор 39, D-триггер 40, блок 41 задержки, вход 41, первый 42 и второй 43 выходы блока управления.

Устройство для передачи и приема данных работает следующим образом.

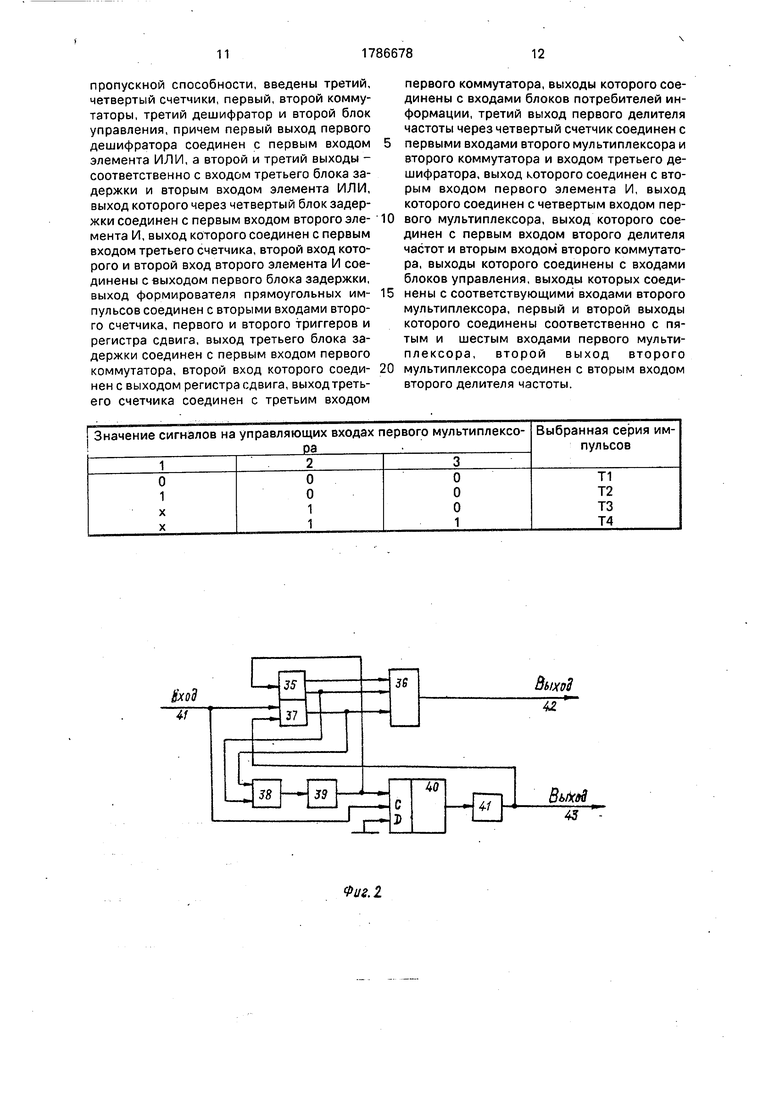

Делитель 20 частоты делит частоту тактового генератора 1 и формирует на своих трех выходах три последовательности импуль- сов разной длительности Т1.Т2, ТЗ, поступающие на соответствующие информационные входы первого мультиплексора 21. Выбор.серии импульсов и их длительность на выходе мультиплексора 21 зависит от значения сиг- налов на трех его управляющих входах. Форма импульсов на выходе мультиплексора 21 при наличии и отсутствии передаваемой информации приведена на фиг. 3 (а, б).

Блок управления (фиг. 2) работает еле- дующим образом.

С выхода блока 35 источника информации данные, сопровождаемые стробирую- щим импульсом, заносятся в регистр 36 сдвига. Одновременно устанавливается в О счетчик 38 и прекращает действовать сигнал на установочном входе D-триггера 40. При выборе соответствующего блока управления сигнал с выхода первого мультиплексора 21 через коммутатор 30 поступает на вход 41 блока. Очередным задним фронтом импульса с входа 41 происходит установка D-триггера 40 в состояние, обеспечивающее сдвиг данных в регистре 36, и счет числа переданных бит счетчиком 38. После передачи всего поля данных (код в счетчике 38 соотве ствует числу бит поля данных) изменяется сигнал на выходе дешифратора 39, подключенном к D-триггеру 40. Происходит установка последнего в со- стояние, запрещающее выполнение сдвига в регистре 36 и счета счетчиком 38. При этом на вход блока 35 источника информации с выхода дешифратора 39 поступает сигнал о готовности к передаче следующего поля

данных. Сигналы с выходов регистра 36 и блока входа 41 задержки поступают на соответствующие входы мультиплексора 21 через мультиплексор 28.

Сигналы с выходов выбранного блока 25 или 26 управления поступают через мультиплексор 28 на первый и второй управляющие входы мультиплексора 21. Одновременно сигнал, соответствующий второму выходу блока управления, поступает на установочный вход второго делителя 23 частоты, запрещая в нем режим деления до завершения передачи поля данных. После завершения передачи поля данных и прекращения поступления сигнала на установочный вход делитель 23 частоты начинает работать в режиме деления импульсов, поступающих с выхода мультиплексора 21. Сигнал с выхода делителя 23 поступает через элемент И 23 на третий управляющий вход мультиплексора 21 лишь в том случае, если выбран последний блок управления.и произошло изменение значения сигнала .на выходе дешифратора 3.

На выходе мультиплексора 21 формируются серии импульсов.показанные в таблице.

Это приводит к тому, что сигналы синхронизации от всех блоков управления, кроме последнего, состоят из одного импульса ТЗ. Сигнал синхронизации от последнего блока управления состоит из комбинации информационного импульса Т1 и синхронизирующего ТЗ.

При формировании импульса синхронизации ТЗ задним фронтом импульса с третьего выхода делителя 20 частоты происходит изменение кода в счетчике 27 и выбор следующего блока управления. Формирование последовательности группы импульсов синхронизации в составе Т1 и ТЗ происходит лишь при выборе заданного (с наибольшим номером) блока управления. Если код в счетчике 27 соответствует выходу дешифратора 29, подключенному к элементу И 24, то происходит формирование группы импульсов синхронизации, состоящей из Т1 и ТЗ. Задним фронтом этого импульса счетчик 27 устанавливается в О из-за переполнения, что обеспечивается выбором типа счетчика с соответствующими характеристиками или его установкой в О по заднему фронту импульса с выхода дешифратора 29.

Для получения на выходе мультиплексора 21 импульсов со скважностью 1 /2 задним фронтом импульса через формирователь 22 происходит синхронизация счетчиков делителя 20 частоты,

Входной аналоговый сигнал из линии связи через входной усилитель 2, фильтр 3 нижних частот и формирователь 4 прямоугольных импульсов поступает на блоки 5, 11 и 17. При поступлении импульса на установочный вход счетчика 11 производится измерение его длительности путем подсчета импульсов с выхода тактового генератора 1. В зависимости от длительности входных импульсов, с помощью дешифратора 12 устанавливаются в 1 триггеры 13 и 14, Если длительность импульса ТЗ, то оба триггера устанавливаются в 1, а еслиТ2 -то только триггер 14. По заднему фронту входного импульса происходит сдвиг данных в регистре 17. Необходимая задержка обеспечивается блоком 15 задержки. Одновременно происходит счет числа принятых бит счетчиком 5. После приема всего поля данных с известным фиксированным числом бит изменяется состояние на выходе дешифратора 6, подключенном к входу блока 7 задержки. Передним фронтом импульса с выхода блока 7 задержки, поступающим через коммутатор 31, производится занесение принятых данных из регистра 17 сдвига в выбранный блок 18, 19 потребителя информации.

При поступлении импульсов синхронизации передним фронтом импульса с вых,о- да блока 16 задержки выполняется установка в нуль первого счетчика 5. Если были приняты дополнительные информационные импульсы в составе группы импульса синхронизации передним фронтом импульса с выхода блока 16 задержки на выходе элемента И 10 формируется импульс, устанавливающий счетчик 42 в состояние, соответствующее выбору блока потребителя информации с наибольшим (последним) номером. Происходит синхронизация счетчиков 27 и 32 выбора номера источника и потребителя информации.

Изменение состояния счетчика 32 происходит по заднему фронту импульса с выхода блока 16, что приводит к коммутации входов следующего блока потребителя информации к выходам блока 7 задержки и регистра 17 сдвига. Информация в буферный регистр блока потребителя информации записывается из регистра 17 сдвига по переднему фронту импульса с выхода блока 7, который при необходимости содержит в своем составе формирователь короткого импульса.

Темп передачи данных отдельно взятого источника информации в устройстве зависит от других источников. Он растет по мере снижения темпа передачи данных другими источниками информации.

Средняя скорость передачи данных (в байтах/с) каждым источником информации при Т3 2Т2 4Т1 равна

V (16 -N+4M)-Ti ГДе N ЧИСЛО пере дающих источников информации в данный момент; М - число источников информации,

у которых передача отсутствует, т.е. учитываются только потери времени на передачу импульсов синхронизации.

В устройстве время задержки блоков 7, 9,15,16 и 41 должно быть не меньше времени задержки фронтов тактовых сигналов на входах блоков, на которые они поступают. В общем случае задержка должна быть такой длительности, чтобы при занесении в триггер или сдвиговый регистр сигнал на информационном входе начинал меняться лишь после окончания фронта импульса, выполняющего занесение. При рассмотрении работы устройства необходимо учитывать естественные задержки сигналов в каждом

блоке.

Таким образом, предлагаемое устройство для передачи и приема дойных благодаря мультиплексированию данных от различных источников информации позволяет увеличить пропускную способность и обеспечить равномерную загрузку ка нала связи при неравномерном темпе передачи данных отдельными источниками информации, что выгодно отличает предлагаемое устройство

от прототипа.

Формула изобрет ения Устройство для передачи и приема данных, содержащее последовательно соединенные усилитель, фильтр нижних частот,

формирователь прямоугольных импульсов, первый счетчик и первый дешифратор, последовательно соединенные тактовый гене ратор, второй счетчик, второй дешифратор, первый триггер и первый блок задержки,

выход которого соединен с вторым входом первого счетчика, второй выход второго дешифратора через последовательно соединенные второй триггер и второй блок задержки соединен с первым входом регистра сдвига, выход тактового генератора соединен с первым входом первого делителя частоты, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами первого

мультиплексора, выход которого является выходом устройства и через формирователь коротких импульсов соединен с вторым входом первого делителя частоты, выход второго делителя частоты соединен с первым

входом первого элемента И, а также элемент ИЛИ, третий, четвертый блоки задержки, второй элемент И, первый блок управления,второй мультиплексор, отличающееся тем, что, с целью увеличения

пропускной способности, введены третий, четвертый счетчики, первый, второй коммутаторы, третий дешифратор и второй блок управления, причем первый выход первого дешифратора соединен с первым входом элемента ИЛИ, а второй и третий выходы - соответственно с входом третьего блока задержки и вторым входом элемента ИЛИ, выход которого через четвертый блок задержки соединен с первым входом второго элемента И, выход которого соединен с первым входом третьего счетчика, второй вход которого и второй вход второго элемента И соединены с выходом первого блока задержки, выход формирователя прямоугольных импульсов соединен с вторыми входами второго счетчика, первого и второго триггеров и регистра сдвига, выход третьего блока задержки соединен с первым входом первого коммутатора, второй вход которого соединен с выходом регистра сдвига, выход третьего счетчика соединен с третьим входом

первого коммутатора, выходы которого соединены с входами блоков потребителей информации, третий выход первого делителя частоты через четвертый счетчик соединен с

первыми входами второго мультиплексора и второго коммутатора и входом третьего дешифратора, выход которого соединен с вторым входом первого элемента И, выход которого соединен с четвертым входом пер0 вого мультиплексора, выход которого соединен с первым входом второго делителя частот и вторым входом второго коммутатора, выходы которого соединены с входами блоков управления, выходы которых соеди5 нены с соответствующими входами второго мультиплексора, первый и второй выходы которого соединены соответственно с пятым и шестым входами первого мультиплексора, второй выход второго

0 мультиплексора соединен с вторым входом второго делителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема данных в полудуплексном режиме | 1990 |

|

SU1732485A1 |

| Устройство для передачи и приема данных | 1987 |

|

SU1510105A1 |

| Устройство для передачи и приема информации | 1990 |

|

SU1748276A1 |

| Устройство для приема и передачи двоичной информации | 1984 |

|

SU1748275A1 |

| Устройство для последовательного обмена данными с квитированием | 1989 |

|

SU1720164A1 |

| Система управления многоканальнымэлЕКТРОпРиВОдОМ РОбОТА | 1979 |

|

SU805246A1 |

| Устройство для приема и передачи данных | 1989 |

|

SU1688438A1 |

| Устройство для приема и передачи цифровой двоичной информации | 1989 |

|

SU1693734A1 |

| Устройство для передачи и приема двоичной информации | 1989 |

|

SU1688439A1 |

| Устройство для передачи и приема данных | 1989 |

|

SU1665529A1 |

Устройство содержит тактовый генератор 1,усилитель 2, фильтр 3 нижних частот,формирователь 4 прямоугольных импульсов,счетчики5,11,27и32,дешифраторы6, 12 и 29, блоки 7,9,15 и 16 задержки, элементы И 10 и 24, триггеры 13 и 14, регистр 17 сдвига, блоки 18 и 19 потребителя информации, элемент 8 ИЛИ, делители 20 и 23 частоты, мультиплексоры 21 и 28, формирователь 22 короткого импульса, блоки 25 и 26 управления, коммутаторы 30 и 31. Предлагаемое устройство благо/заря мультиплексирование данных от различных.источников информации позволяет увеличить пропускную способность и обеспечить равномерную загрузку канала связи при неравномерном темпе передачи данных отдельными источниками информации. 3 ил., 1 табл.

| Устройство для передачи и приема данных | 1988 |

|

SU1589417A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-01-07—Публикация

1990-01-23—Подача