« 2О

а

СЛ

00

Щ(

ft 22 Фи.1

3151

Изобретение относится к вычислительной технике и может быть использовано в системах приема и передачи дискретной информации, а также в бу- ферных запоминающих устройствах систем ввода информа ии многоканальных измерительных комплексов.

Цель изобретения - расширение области применения устройства за счет возможности приоритетного считывания из накопителя асинхронно поступившей приоритетной и обычной информации.

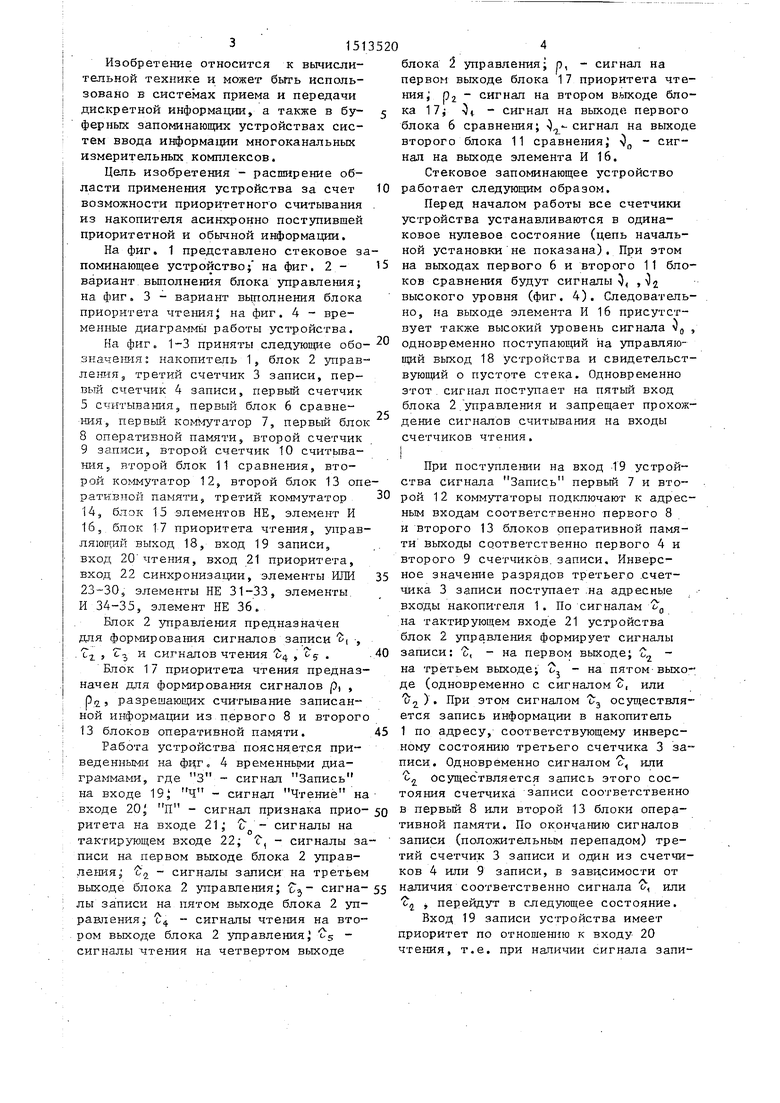

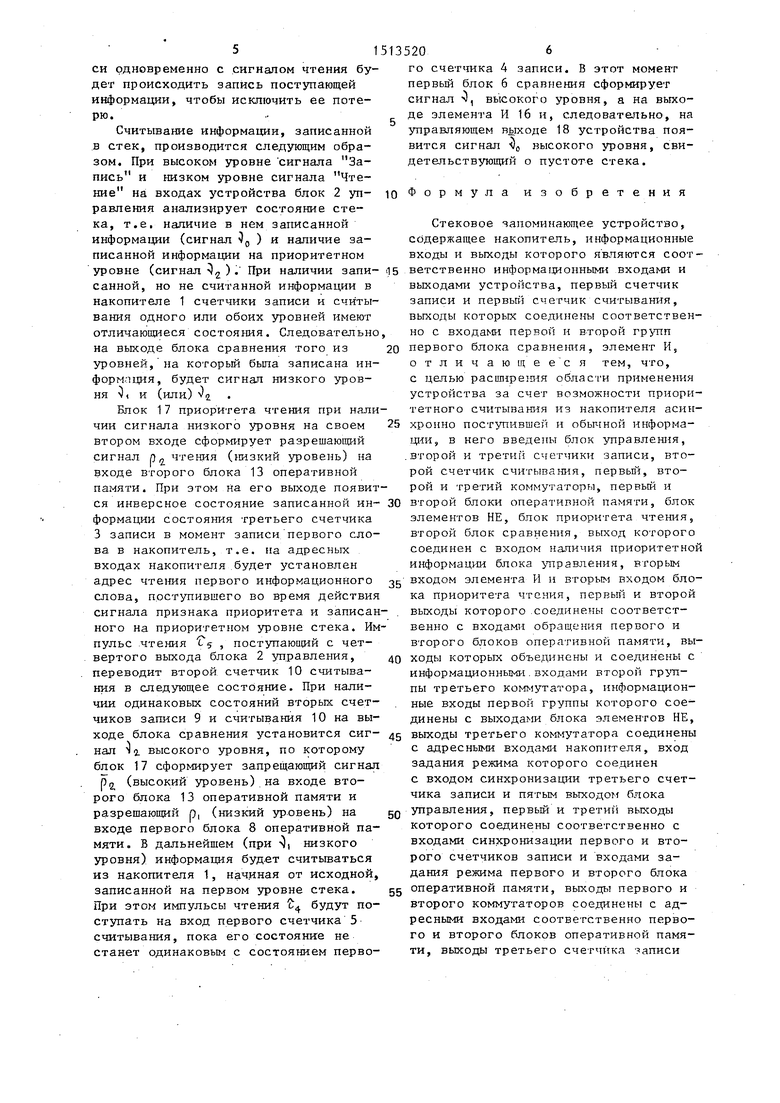

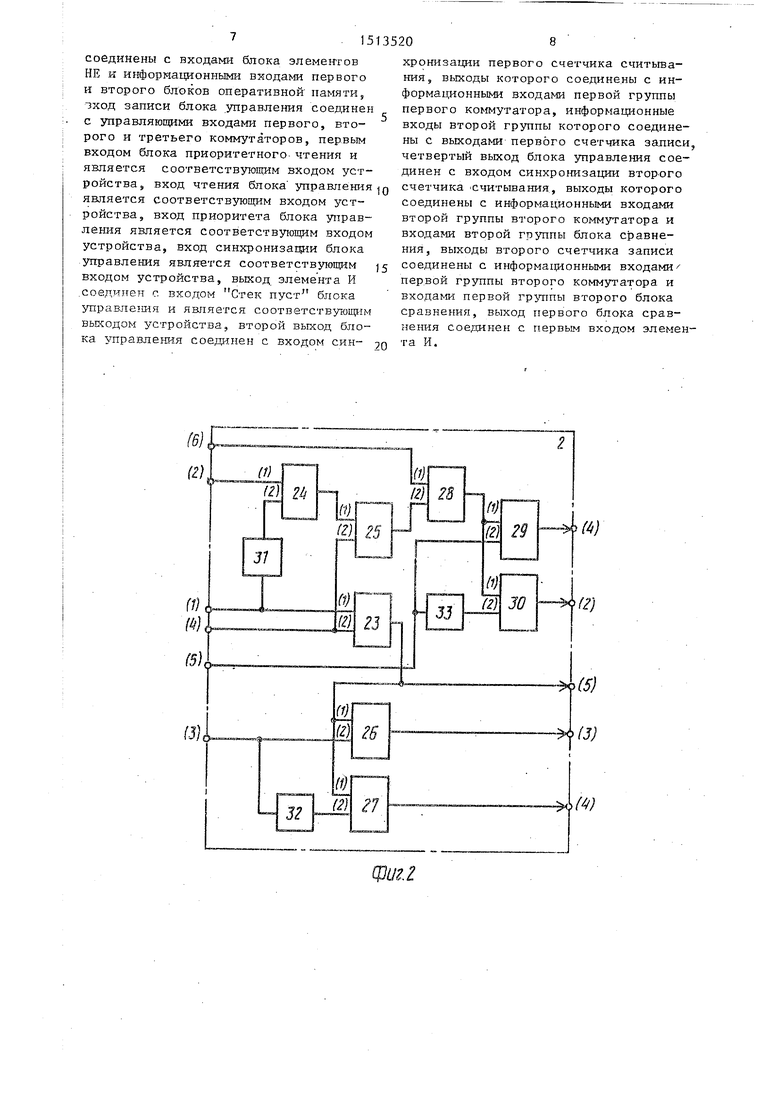

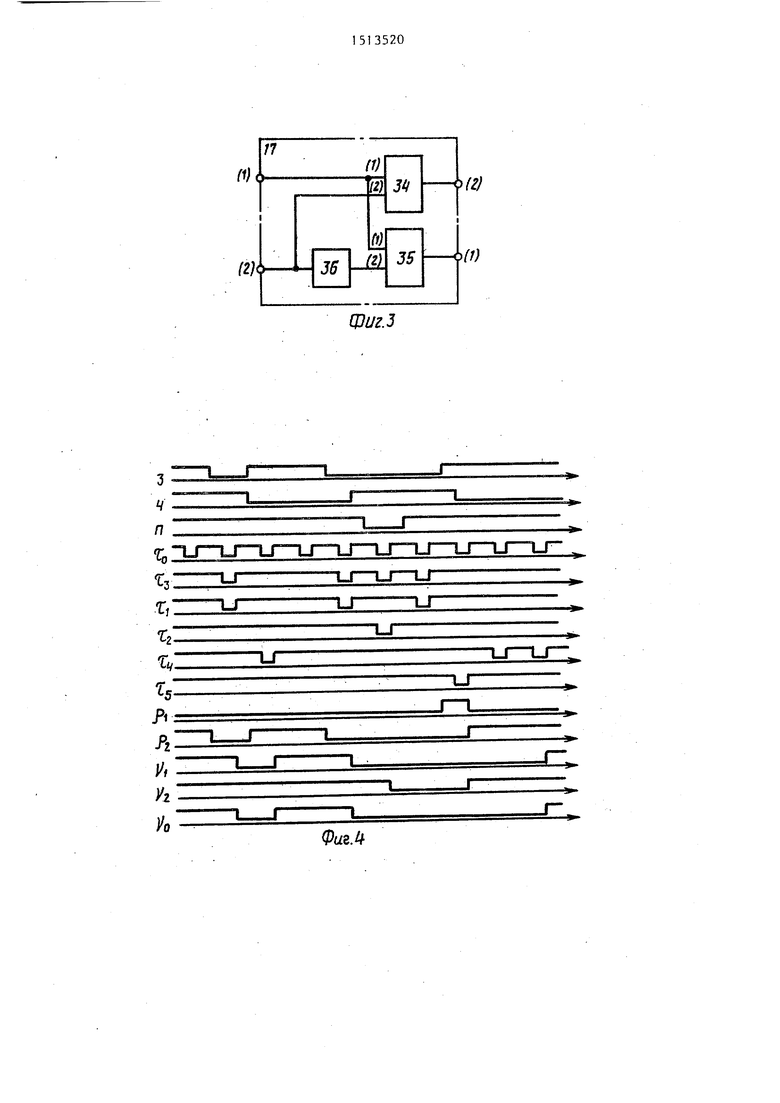

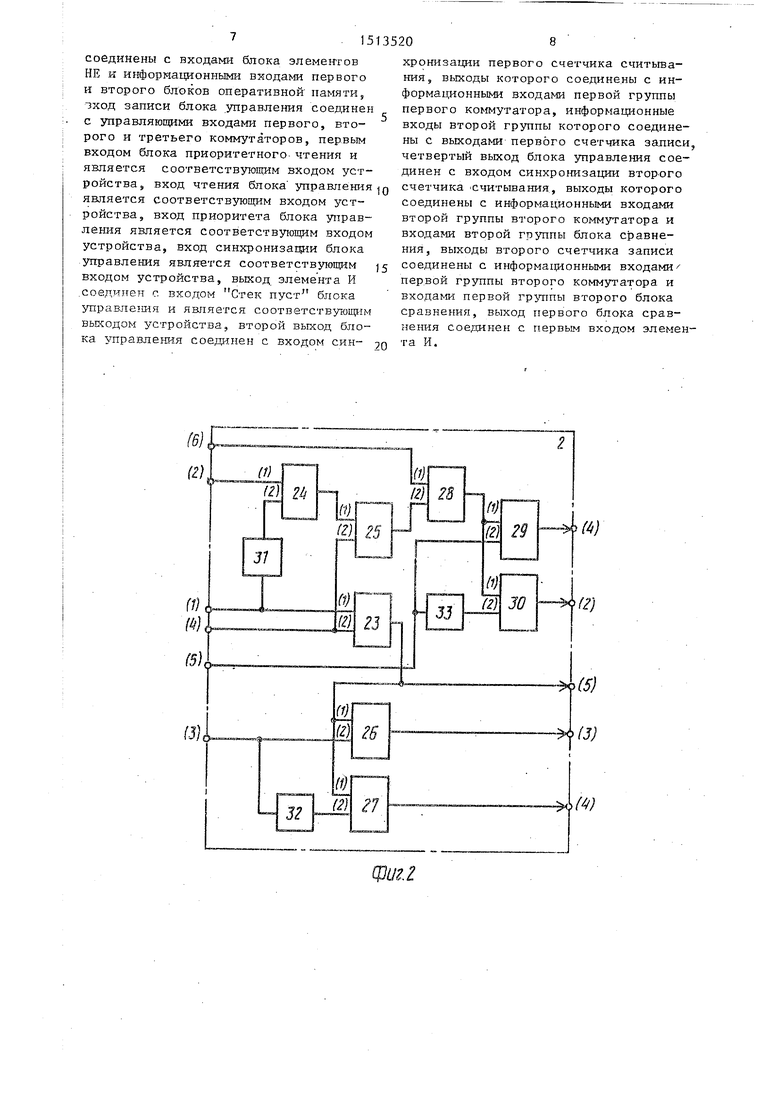

На фиг. 1 представлено стековое зпоминающее устройство; на фиг. 2 - вариант вьшолнения блока управления; на фиг, 3 - вариант вь1полнения блока приоритета чтения на фиг. 4 - временные диаграммь работы устройства.

На фиг. 1-3 приняты следующие обо значения: накопитель 1, блок 2 управ третий счетчик 3 записи, первый счетчик 4 записи, первый счетчик 5 cчитывa шЯз первый блок 6 сравнения, первый коммутатор 7, первый бло

8оперативной памяти, второй счетчик

9записи, второй счетчик 10 считывания, второй блок 11 сравнения, второй коммутатор 12, второй блок 13 опративной памяти, третий коммутатор 14, блок 15 элементов НЕ, элемент И

16, блок 17 приоритета чтения, управляющий выход 18, вход 19 записи, вход 20 чтения, вход 21 приоритета, вход 22 синхронизации, элементы ИШИ 23-305 элементы НЕ 31-33, элементы, И 34-35, элемент НЕ 36.

Блок 2 управления предназначен для формирования сигналов записи

i-j , с и сигналов чтения о ,

Блок 17 приоритета чтения предназначен для формирования сигналов р, , р2, разрешающих считывание записанной информации из первого 8 и второго 13 блоков оперативной памяти.

Работа устройства поясняется при- веденньс/н на фиг, 4 временньгми диаграммами, где 3 сигнал Запись на входе 19 Ч - сигнал Чтение на входе 20 П - сигнал признака прио- ритета на входе 21; о - сигналы на тактирующем входе 22; с , - сигналы записи на первом выходе блока 2 управ- легшя - сигналы записи на третьем выходе блока 2 управления; oj сигналы записи на пятом выходе блока 2 управления j 4 сигналы чтегмя на втором выходе блока 2 управления S s - сигналы чтения на четвертом выходе

5

0

5

30

5

5

0

5

0 5

блока 3 управления; р, - сигнал на первом выходе блока 17 приоритета чтения j р2 - сигнал на втором выходе блока 17j -5 - сигнал на выходе первого блока 6 сравнения; - сигнал на вькоде второго блока 11 сравнения, - сигнал на выходе элемента И 16.

Стековое запоминающее устройство работает следующим образом.

Перед началом работы все счетчики устройства устанавливаются в одинаковое нулевое состояние (цепь начальной установки не показана). При этом на выходах первого 6 и второго 11 блоков сравнения будут сигналы , ,vj высокого зфовня (фиг. 4). Следовательно, на выходе элемента И 16 присутствует также высокий уровень сигнала v , одновременно поступающий на управляющий выход 18 устройства и свидетельствующий о пустоте стека. Одновременно этот сигнал поступает на пятый вход блока 2/управления и запрещает прохождение сигналов считывания на входы счетчиков чтения.

При поступлении на вход 19 устройства сигнала Запись первый 7 и второй 12 коммутаторы подключают к адресным входам соответственно первого 8 и второго 13 блоков оперативной памяти выходы соответственно первого 4 и второго 9 счетчиков.записи. Инверсное значение разрядов третьего .счетчика 3 записи поступает .на адресные входы накопителя 1 . Но сигналам (, на тактирующем входе 21 устройства блок 2 управления формирует сигналы записи: о, - на первом выходе; С - на третьем выходе; о - на пятом-выходе (одновременно с сигналом с, или &2 ) При этом сигнапом 03 осуществляется запись информации в накопитель 1 по адресу, соответствующему инверсному состоянию третьего счетчика 3 записи. Одновременно сигналом , или Осуществляется запись этого состояния счетчика записи соответственно в первьш 8 или второй 13 блоки оперативной памяти. По окончанию сигналов записи (положительным перепадом) третий счетчи.к 3 записи и один из счетчиков 4 или 9 записи, в зависимости от наличия соответственно сигнала или Cj j перейдут в следующее состояние.

Вход 19 записи устройства имеет приоритет по отношению к входу 20 чтения, т.е. при наличии сигнала записи одновременно с сигналом чтения будет происходить запись поступающей информации, чтобы исключить ее потерю.

Считывание информации, записанной в стек, производится следующим образом. При высоком уровне сигнала Запись и низком уровне сигнала Чтение на входах устройства блок 2 управления анализирует состояние стека, т.е. наличие в нем записанной

го счетчика 4 записи. В этот момент первый блок 6 сраниения сформирует сигнал , высокого уровня, а на выходе элемента И 16 и, следовательно, на управляющем выходе 18 устройства появится сигнал )|5 высокого уровня, свидетельствующий о пустоте стека.

10 Формула изобретения

Стековое запоминающее устройство, содержащее накопитель, информационные входы и выходы которого являются соотинформации (сигнал Q, ) и наличие записанной информации на приоритетном

уровне (сигнал 2 ) Р наличии запи- 15 ветственно информац {онными входами и санной, но не считанной информации в выходами устройства, первый счетчик накопителе 1 счетчики записи и считывания одного или обоих уровней имеют отличающиеся состояния. Следовательно,

на выходе блока сравнения того из 20 первого блока сравнегагя, элемент И, уровней, на который быпа записана ин- о т л и ч а ю щ е е с я тем, что, формпция, будет сигнал низкого уровня v, и (или) v,

Блок 17 приоритета чтения при наличии сигнала низкого уровня на своем втором входе сформирует разрешающий сигнал почтения (низкий уровень) на входе второго блока 13 оперативной памяти. При этом на его выходе появится инверсное состояние записанной ин- 30 второй блоки оперативной памяти, блок формации состояния третьего счетчика элементов НЕ, блок приоритета чтения, 3 записи в момент записи первого ело- второй блок сравнения, выход которого ва в накопитель, т.е. на адресных соединен с входом наличия приоритетной входах накопителя .будет установлен и 1формации блока отправления, вторым адрес чтения первого информационного 35 входом элемента И и вторым входом блока приоритета чтения, первый и второй

записи и первьп счетчик считывания, выходы которых соединены соответственно с входами первой и второй

с целью расширеш я области применения устройства за счет возможности приор - - тетного считывания из накопителя асин- 25 хронно поступившей и обычной информации, в него введены блок управления, .второй и третий счетчики записи, второй счетчик считывания, первьй, второй и третий коммутаторы, первый и

слова, поступившего во время действия сигнала признака приоритета и записанного на приоритетном уровне стека. Импульс .чтения 5 , поступающий с четвертого вькода блока 2 управления, переводит второй счетчик 10 считывания в следуюп;ее состояние. При наличии одинаковых состояний вторых счетчиков записи 9 и считывания 10 на вывыходы которого .соединены соответственно с входами обращения первого и второго блоков оперативной памяти, вы- 40 ходы которых объединены и соединены с информационными.входами второй группы третьего коммутатора, информационные входы первой группы которого соединены с выходами блока элементов НЕ,

го счетчика 4 записи. В этот момент первый блок 6 сраниения сформирует сигнал , высокого уровня, а на выходе элемента И 16 и, следовательно, на управляющем выходе 18 устройства появится сигнал )|5 высокого уровня, свидетельствующий о пустоте стека.

Формула изобретения

Стековое запоминающее устройство, содержащее накопитель, информационные входы и выходы которого являются соответственно информац {онными входами и выходами устройства, первый счетчик

записи и первьп счетчик считывания, выходы которых соединены соответственно с входами первой и второй

первого блока сравнегагя, элемент И, о т л и ч а ю щ е е с я тем, что,

второй блоки оперативной памяти, блок элементов НЕ, блок приоритета чтения, второй блок сравнения, выход которого соединен с входом наличия приоритетной и 1формации блока отправления, вторым входом элемента И и вторым входом блока приоритета чтения, первый и второй

с целью расширеш я области применения устройства за счет возможности приор - - тетного считывания из накопителя асин- хронно поступившей и обычной информации, в него введены блок управления, второй и третий счетчики записи, второй счетчик считывания, первьй, второй и третий коммутаторы, первый и

выходы которого .соединены соответственно с входами обращения первого и второго блоков оперативной памяти, вы- ходы которых объединены и соединены с информационными.входами второй группы третьего коммутатора, информационные входы первой группы которого соединены с выходами блока элементов НЕ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Стоковое запоминающее устройство | 1988 |

|

SU1520597A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1453440A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Устройство для сопряжения управляющей вычислительной машины с периферийными устройствами | 1983 |

|

SU1201841A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Логическое запоминающее устройство | 1987 |

|

SU1566411A1 |

| Устройство для контроля вычислительного процесса ЭВМ | 1988 |

|

SU1596332A1 |

| УСТРОЙСТВО ОБМЕНА ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1991 |

|

RU2020571C1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах приема и передачи дискретной информации, а также в буферных запоминающих устройствах систем вывода информации многоканальных измерительных комплексов. Цель изобретения - расширение области применения за счет возможности приоритетного считывания информации. Устройство содержит накопитель 1, блок 2 управления, третий счетчик 3 записи, первый счетчик 4 записи, первый счетчик 5 считывания, первый блок 6 сравнения, первый коммутатор 7, первый блок 8 оперативной памяти, второй счетчик 9 записи, второй счетчик 10 считывания, второй блок 11 сравнения, второй коммутатор 12, второй блок 13 оперативной памяти, третий коммутатор 14, блок 15 элементов НЕ, элемент И 16, блок 17 приоритета чтения. 4 ил.

ходе блока сравнения установится сиг- g выходы третьего коьмутатора соединены нал 1 высокого уровня, по которому с адресными вxoдaмIi накопителя, вход блок 17 сформирует запрещающий сигнал р (высокий уровень) . на входе второго блока 13 оперативной памяти и разрешающий р, (низкий ур.овень) на входе первого блока 8 оперативной памяти, В дальнейшем (при NI низкого уровня) информация будет считываться из накопителя 1, начиная от исходной, записанной на первом уровне стека. При этом импульсы чтения t будут поступать на вход первого счетчика 5 считывания, пока его состояние не станет одинаковым с состоянием первозадания режима которого соединен с входом синхронизации третьего счетчика записи и пятым выходом блока

gQ управления, первый и третий выходы которого соединены соответственно с входами синхронизации первого и второго счетчиков записи и входами задания режима первого и второго блока

gg оперативной памяти, выходы первого и второго коммутаторов соединены с адресными входами соответственно первого и второго блоков оперативной памяти, выходы третьего счетчика записи

выходы третьего коьмутатора соединены с адресными вxoдaмIi накопителя, вход

задания режима которого соединен с входом синхронизации третьего счетчика записи и пятым выходом блока

управления, первый и третий выходы которого соединены соответственно с входами синхронизации первого и второго счетчиков записи и входами задания режима первого и второго блока

оперативной памяти, выходы первого и второго коммутаторов соединены с адресными входами соответственно первого и второго блоков оперативной памяти, выходы третьего счетчика записи

I15

соединены с входами блока элеменгов НЕ и информационными входами первого и второго блоков оперативной памяти, зход записи блока зттравления соединен с управляющими входами первого, второго и третьего коммутаторов, первым входом блока приоритетного-чтения и является соответствующим входом уст

ройства, вход чтения блока управления д счетчика Считывания, выходы которого

является соответствующим входом устройства, вход приоритета блока управления является соответствующим входом устройства, Вход синхронизации блока управления является соответствующим 55 входом устройства, выход элемента И .соединен с входом Стек пуст блока управле1шя и является соответствуюищм вьЕсодом устройства, второй выход блока управления соединен с входом син- 20

хронизацин первого счетчика считьгеа- ния, выходы которого соединены с информационными входами первой группы первого коммутатора, информационные входы второй группы которого соединены с выходами первого счетчика залиси, четвертый выход блока управления соединен с входом синхронизации втор-ого

соединены с информационными входами второй группы второго коммутатора и входами второй группы блока сравнения, выходы второго счетчика записи соединены с информационными входами первой группы второго коммутатора и входами первой группы второго блока сравнения, выход первого блока сравнения соединен с первым входом элемета И.

п TO,

т/.

TV

V- i.

л Vf

Xi

ЦЗиг.З

Т-Г

| Стековое запоминающее устройство | 1979 |

|

SU881863A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1048515A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-10-07—Публикация

1986-12-30—Подача