В известных способах выполнения логических операций с .использованием ферритовых регистров сдвига операцию запрета производят либо логическими сигналами, либо тактовыми. Это приводит « тому, что, с одной стороны, сигналы логических ячеек и ячеек «памяти должны удовлетворять всем требованиям, предъявляемым « запрещающим сигналам, а с другой стороны, запрещающие сигналы в этом случае сильно меняются в зависимости от нагрузки ячеек и от способа запуска этих ячеек. Были попытки устранить эти недостатки введением двух типов ячеек «памяти, причем выходные сигналы .одной ячейки являются запрещающими для другой ячейки. Такое усложнение схемы не дает, однако, желаемого результата.

По предлагаемому .способу в качестве запрещающих сигналов используют специальные стандартные сигналы, параметры которых выбирают так, чтобы они могли запретить любой сигнал ячеек «памяти

и «или.

Покажем, что используя ячейки «памяти, «или и «запрет записи «1 в ячейку «памяти стандартным сигналом, можно выполнять логические операции вида:

7 Е ;rW Е 7 и II. Х

1(Х) ;1(п } т Л (К) J.

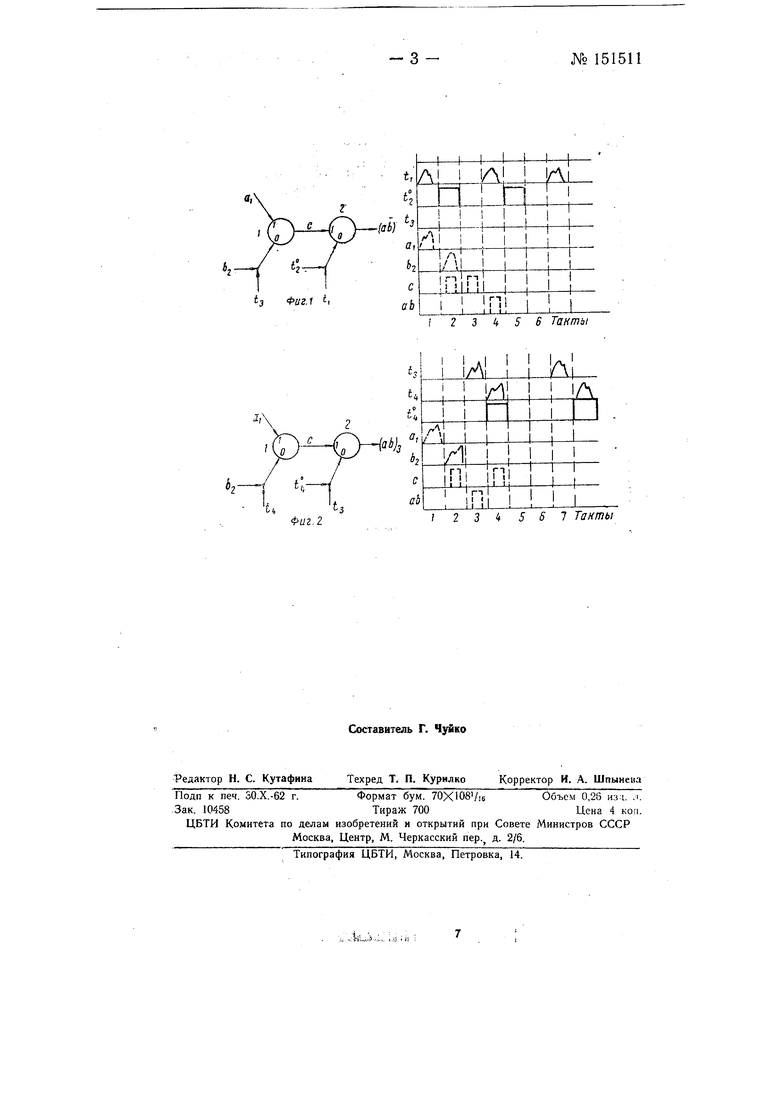

На фиг. 1 и 2 .приведены схемы, реализующие операции иида а-Ь (а . b сигналы) предложенным способом.

Сигналы а п Ь могут быть логическими суммами сигналов одинаковой тактности, т. е. приходящими во время одного и того же такта. ОбыЧНые тактовые (синхронизирующие) сигналы обозначим буквой t, стандартные-f. Цифры внизу справа у обозначений указывают, в какой последовательности (в какой такт) должны подаваться сигналы а, Ь, t и t°.

№151511-2

Синхронизирующие сигналы t и стандартные сигналы /° генерируются схемой, управляющей работой всего вычислительного устройства.

На выходе ячейки / «па1мяти сигнал с м-ожет появиться либо во время прихода сигнала Ь, либо сигнала з. «о при условии, что перед этим на вход ячейки 1 придет сигнал a. Сигнал на выходе, одновремеиный с U2, эквивалентен операции а. &, а одновременный с 4 эквивалентен операции а-ЬЕсли стандартный сигнал tz° совпадает с логическим сигналом Ь, то сигналом С2, соответствующим операции а.Ь, запрещается запись «1 в ячейку 2, и сигналом Сз, соответствующим операции а. Ь, разрешается запись «1 в ячейку 2. Таким образом, на выходе получают сигнал, соответствующий операции а. 6-или, в общем виде:

Если же стандартный сигнал 4°, совпадает по фазе с тактовым сигналом , то в ячейку 2 -записывается «1, соответствующая операция а. Ь или, в общем виде:

(SA-WSn

(Х) ) (Y) ).

Следует заметить, что стандартные сигналы служат лишь для запрета записи «1 в ячейку «памяти. Для списывания «1 используют тактовые сигналы и сипналы ячеек «памяти и «или. А так как при «запрете записи «1 в ячейку «памяти состояние последней ие ме«яется, то мощность стандартного сигнала может быть много меньше, чем мощность сигналов ячейки «ламяти или «или. Это позволяет создавать генераторы стандартных сигналов с большей нагрузочной способностью.

Предмет изобретения

Способ выполнения логических операций типа (i V Х VVXn) V

ACi.VF VVyj или (X,VX,VV X,) f(Y,V Y,,

где n и т-число логических входов, отличающийся тем, что, с целью повыщения надежности работы логических устройств, на их входы синхронно с тактовыми сигналами подают серию стандартных сипналоБ запрета, параметры которых перекрывают разброс параметров входных сигналов.

jS)(Sr

(Х) 1 (Y) )

23455 Танты

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ МНОГОТАКТНОГО ВЫПОЛНЕНИЯ ЛОГИЧЕСКИХОПЕРАЦИЙ | 1968 |

|

SU220620A1 |

| СИНХРОНИЗАТОР ДЛЯ МНОГОТАКТНЫХ ФЕРРОТРАНЗИСТОРНЫХ СИСТЕЛ1 С РАЗНОВРЕМЕННЫЛ1ЗАПРЕТОМ | 1970 |

|

SU273517A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1336011A2 |

| Ассоциативная ячейка памяти | 1989 |

|

SU1635216A1 |

| Устройство для обработки цифровых данных | 1986 |

|

SU1424008A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для дистанционного программного управления сигнализацией и электропроводными механизмами | 1990 |

|

SU1801223A3 |

t-

Фиг.2

1 234 567 Танты

Авторы

Даты

1962-01-01—Публикация

1962-01-31—Подача