ел

VI

о

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционное устройство процессора | 1979 |

|

SU809189A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство предварительной выборки команд | 1987 |

|

SU1561073A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2049347C1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042188C1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

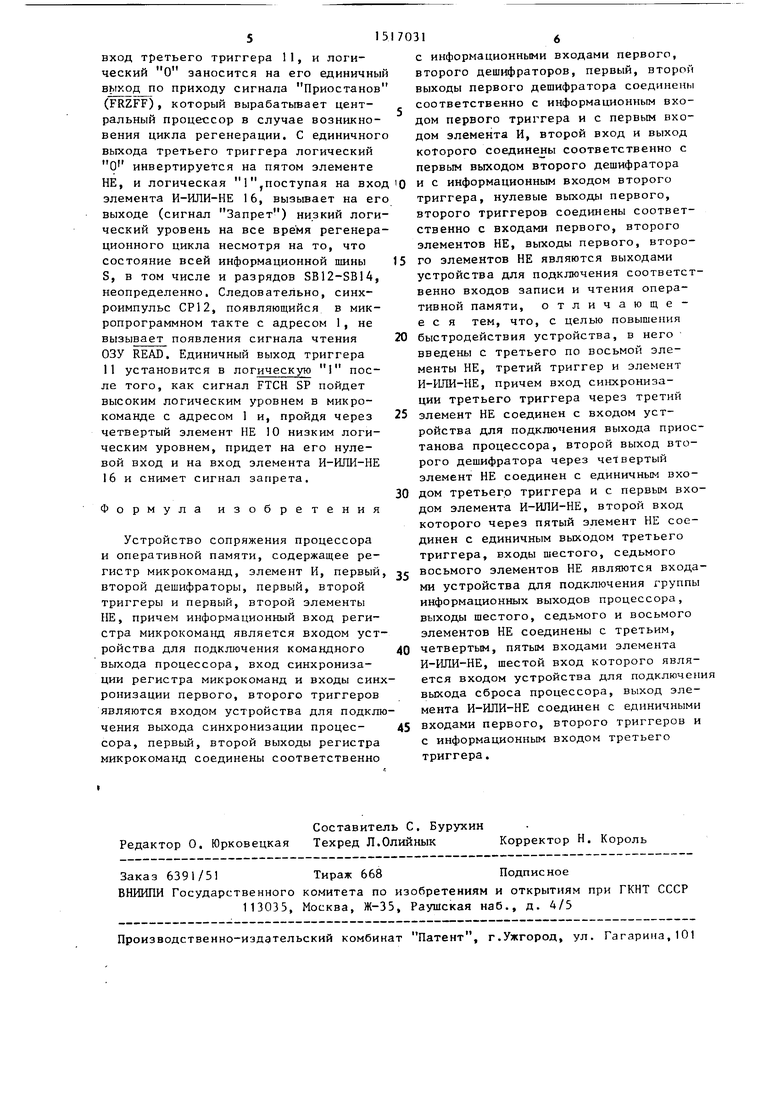

Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных машин повышенной производительности. Целью изобретения является повышение быстродействия устройства. Устройство содержит регистр 1 микрокоманд, первый 2 и второй 3 дешифраторы, элемент И 4, первый 5 и второй 6 триггеры, с первого по четвертый элементы НЕ 7-10, третий триггер 11, с пятого по восьмой элементы НЕ 12-15, элемент И-ИЛИ-НЕ 16. Устройство обеспечивает повышенное быстродействие при работе процессора с оперативной памятью путем исключения холостых циклов чтения при выборке операндов безадресных команд. 1 ил.

Запись ОЗУ Чтение ОЗУ

Изобретение относится к вычислительной технике и южет быть использовано при построении вычислительных машин повышенной производительности.

Целью изобретения является повышение быстродействия устройства.

На чертеже представлена блок-схема устройства.

Устройство содержит регистр 1 микрокоманд, первый и второй дешифраторы 2 и 3, элемент И 4, первый и второй триггеры 5 и 6,-С первого по четвертый элементы НЕ 7-10, третий триггер 1, с пятого ио восьмой элементы НЕ 12-15 и элемент И-ВДИ-НЕ 16.

Устройство работает в трех режимах: выборки операнда адресной команды, запрета чтения операнда при вы борке безадресной команды и запрета чтения операнда при возникновении цикла регенерации ОЗУ в момент выборки безадресной команды.

В реж1ше выборки операнда адресной команды в нулевой микрокоманде адресной команды по микроприказу READ на выходе дешифратора 2 поля онерации возникает сигнал READ OP длительностью в микропрограммный такт, который, проходя через элемент И 4, поступает на информационный вход второго триггера 6. В моменты Р и Рг этого микропрограм- IЮГo такта на основной процессорной li TiHe появляется код адресной команды, поскольку в этом случае в одном из разрядов шины SB12-SB14 обязательно присутствует логическая , которая, проходя через один из элементов НЕ J3

15 и племант И-ИЛИ-НЕ 16, вырабатыва-дд риодически проводить специальные циклы регенерации, при которых обращение к нему запрещено, так как можно получить неопределенную информацию. Поскольку ОЗУ и процессор работают в

гического уровня (находящегося на ин- 45 общем случае асинхронно, то такой

от сигнал Запрет высоким логическим уровнем, который, поступая на единич- Hbu i вход второго триггера 6, не пре- нятствует занесению в него низкого лоформанионном входе) по перепаду из 1НПКОГО в высокий синхроимпульса. Следовательно, в следующем микропрог- pat-;M OM такте вырабатывается сигнал READ (его перепад из низкого в высо- кий формируется синхросигналом сброса РА), который запускает цикл чтения операнда,

В режиме запрета чтения операнда при ныборке безадресной команды в нулевой микрокоманде микропрограммы безадресной команды по микроприказу READ на выходе дешифратора 2 поля операции возникает сигнал READ OP

0

5

5

0

0

5

длительнос ью в один микропрограммный такт, который, проходя через элемент И 4, поступает на информационный вход второго триггера 6. По микроприказу FTCH на выходе дешифратора 3 возникает сигнал FTCK SP длительностью в один микропрограммньш такт, который, проходя через четвертый элемент НЕ 10, поступает на вход элемента И-ИПИ-НЕ 16 высоким логическим уровнем. В моменты времени Р и Р этого микропрограммного такта на основной процессорной шине появляется код безадресной команды. Так как в этом случае на всех разрядах шины SB12-SB14 находятся логические О, то, проходя через элементы НЕ 13-15, они вы- зьшают на входах элемента И-ИЛИ-НЕ 16 логическую 1. При этом на выходе этого элемента возникает сигнал Запрет низким логическим уровнем, который поступает на вход второго триггера 6 и вызывает появление на его нулевом выходе постоянного уровня логического О. Так как у триггера нулевой вход имеет приоритет выше, чем С-вход, то независимо от того, что на него приходит синхроимпульс и на его информационном входе присутствует логический О, состояние его нулевого выхода не изменяется.и сигнал READ, инициализирующий цикл чтения ОЗУ, не возникает.

В режиме запрета чтения операнда при возникновении цикла регенерации ОЗУ в момент выборки безадресной команды для обеспечения сохранности информации в таком ОЗУ необходимо пеQ

5

цикл может возникнуть при вьшолнении любой микрокоманды, в том числе и в момент выполнения центральным процессором нулевой микрокоманды подпрограммы выборки безадресной команды.В этом режиме в начале микропрограммного такта вырабатывается сигнал READ OP, который через элемент И 4 проходит на информационный вход второго триггера 6, и формируется сигнал Запрет. Этот сигнал поступает на единичный вход триггера 6 и запрещает выработку сигнала READ, кроме того, он приходит на информационный

вход третьего триггера 11, и логический О заносится на его единичный выход по приходу сигнала Приостанов (FRZFF), который вырабатывает центральный процессор в случае возникновения цикла регенерации. С единичного выхода третьего триггера логический О инвертируется на пятом элементе НЕ, и логическая 1,поступая на вход элемента И-ИЛИ-НЕ 16, вызьшает на его выходе (сигнал Запрет) низкий логический уровень на все время регенера- ционного цикла несмотря на то, что состояние всей информационной шины S, в том числе и разрядов SB12-SB14, неопределенно. Следовательно, синхроимпульс СР12, появляющийся в микропрограммном такте с адресом 1, не вызывает появления сигнала чтения

ОЗУ READ, Единичный выход триггера 11 установится в логическую 1 после того, как сигнал FTCH SP пойдет высоким логическим уровнем в микрокоманде с адресом 1 и, пройдя через четвертый элемент НЕ 10 низким логическим уровнем, придет на его нулевой вход и на вход элемента И-ИЛИ-НЕ 16 и снимет сигнал запрета.

Формула изобретения

Устройство сопряжения процессора и оперативной памяти, содержащее регистр микрокоманд, элемент И, первый, второй дешифраторы, первый, второй триггеры и первый, второй элементы НЕ, причем информационный вход регистра микрокоманд является входом устройства для подключения командного выхода процессора, вход синхронизации регистра микрокоманд и входы синхронизации первого, второго триггеров являются входом устройства для подключения выхода синхронизации процес- сора, первый, второй выходы регистра микрокоманд соединены соответственно

й од iQ о -

15

20

, 45

5170316

с информационными входами первого, второго дешифраторов, первый, второй выходы первого дешифратора соединены соответственно с информационным входом первого триггера и с первым входом элемента И, второй вход и выход которого соединены соответственно с первым выходом второго дешифратора и с информационным входом второго триггера, нулевые выходы первого, второго триггеров соединены соответственно с входами первого, второго элементов НЕ, выходы первого, второго элементов НЕ являются выходами устройства для подключения соответственно входов записи и чтения оперативной памяти, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены с третьего по восьмой элементы НЕ, третий триггер и элемент И-ИЛИ-НЕ, причем вход синхронизации третьего триггера через третий элемент НЕ соединен с входом устройства для подключения выхода приос- танова процессора, второй выход второго дешифратора через четвертый элемент НЕ соединен с единичным входом третьего триггера и с первым входом элемента И-ИЛИ-НЕ, второй вход которого через пятый элемент НЕ соединен с единичным выходом третьего триггера, входы шестого, седьмого восьмого элементов НЕ являются входами устройства для подключения группы информационных выходов процессора, выходы шестого, седьмого и восьмого элементов НЕ соединены с третьим, четвертым, пятым входами элемента И-ИЛИ-НЕ, шестой вход которого является входом устройства для подключения выхода сброса процессора, выход элемента И-ИЛИ-НЕ соединен с единичными входами первого, второго триггеров и с информационным входом третьего триггера.

25

30

35

40

| Устройство для обмена данными между оперативной памятью и внешним устройством | 1984 |

|

SU1180908A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Computer design, 1978, June, p | |||

| Огнетушитель | 0 |

|

SU91A1 |

Авторы

Даты

1989-10-23—Публикация

1988-03-02—Подача