процессорное устройство Kl переходит jc ной программы, которая может вклю4

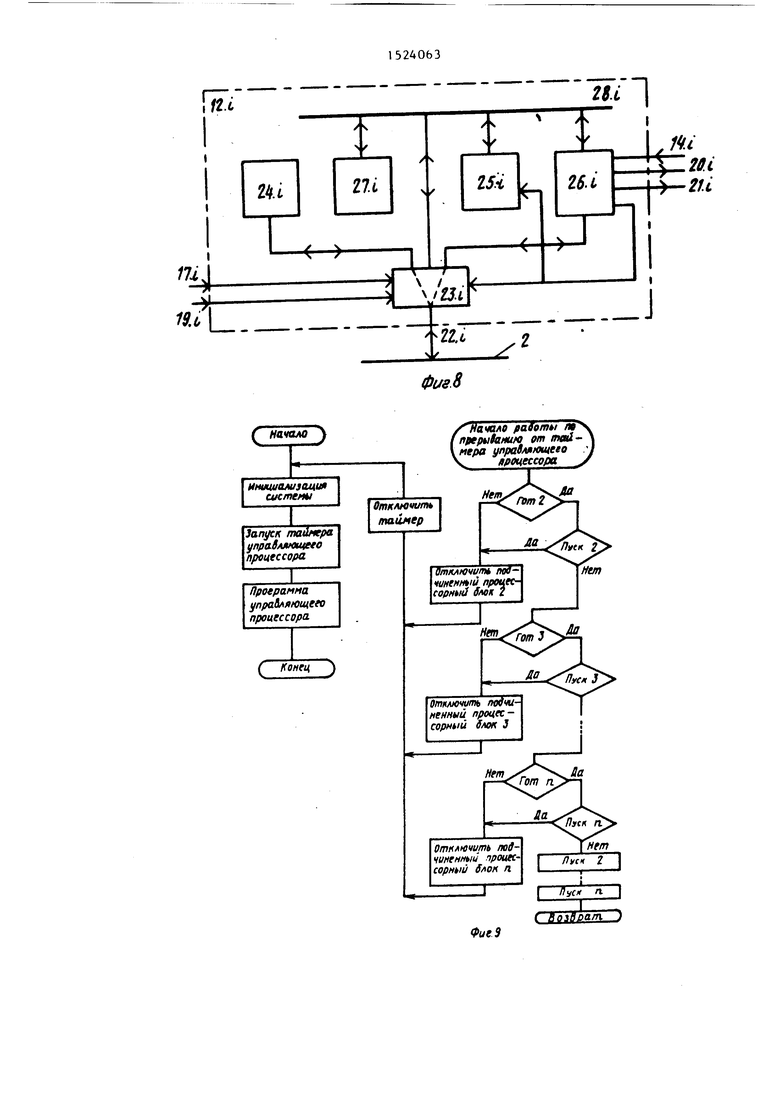

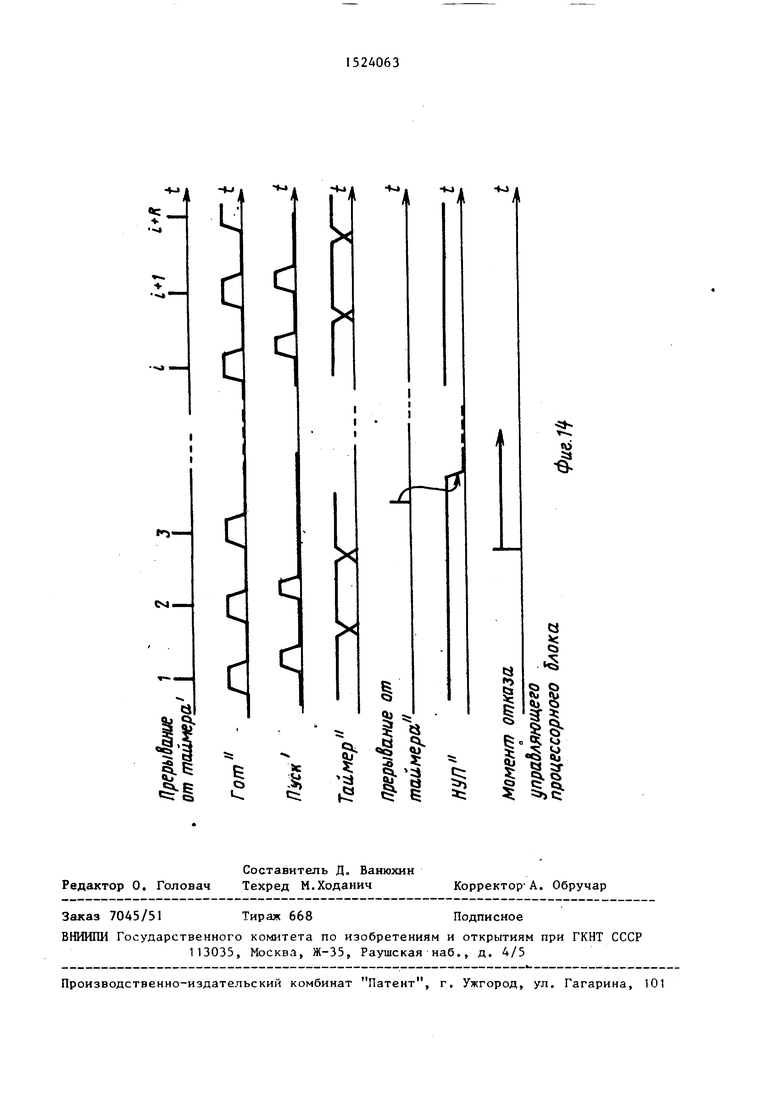

на подпрограмму проверки работоспособности и запуска подчиненных процессорных устройств 1,2,,,,,1,п, При этом поочередно читаются слова состояния каждого процессорного устройства 1.2,,о, , 1,п. Если в слове состояния очередного процессорного устрой- ства 1,1 (фиг,10) в разряде Гото записана единица ( i 1) а в разряде Пуск записан нуль (Пуск i 0), то управляющее устройство 4,1 переходит к анализу слова состояния следующего процессорного устройства 1,1 + 1, Если отсутствует сигнал Гот,-ИЛИ имеется единица в разряде Пуск, то подчиненное устройство считается отказавшим и отключается командой Отключить подчиненное процессорное устройство. После этого управляющее процессорное устройство

20

25

30

чать программу диагностики После заверщения своей программы оно устанавливает в единичное состояние разряд Гот в регистре 26oi(,

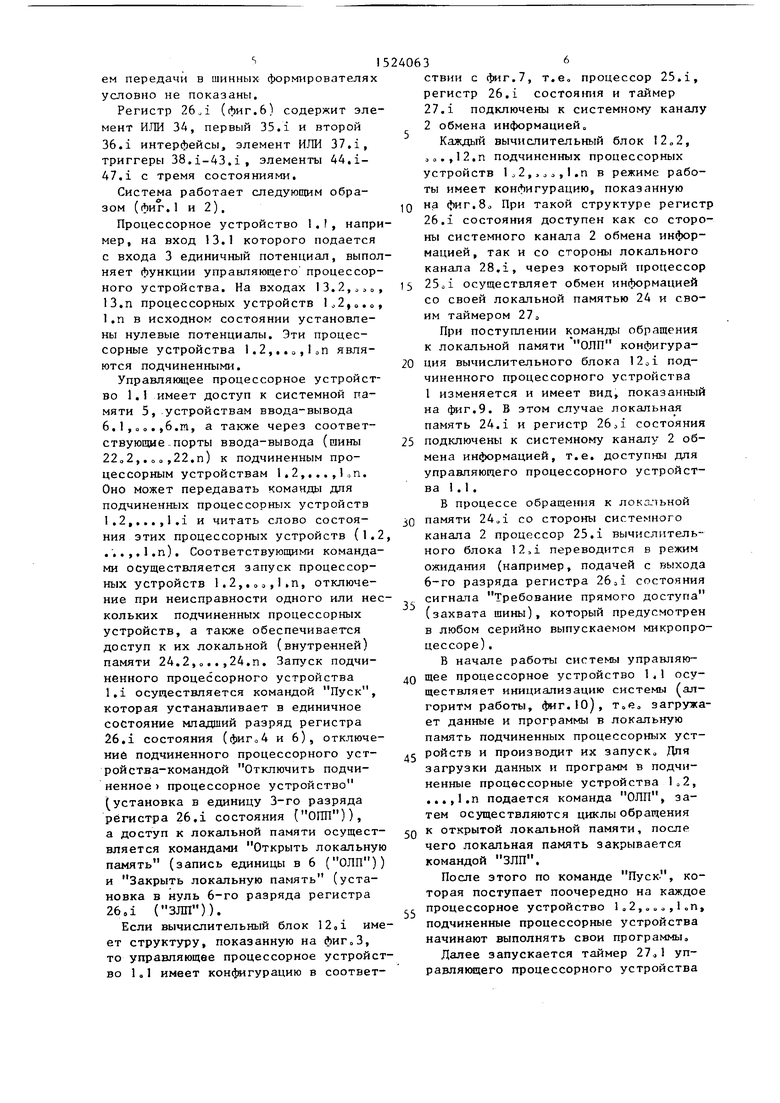

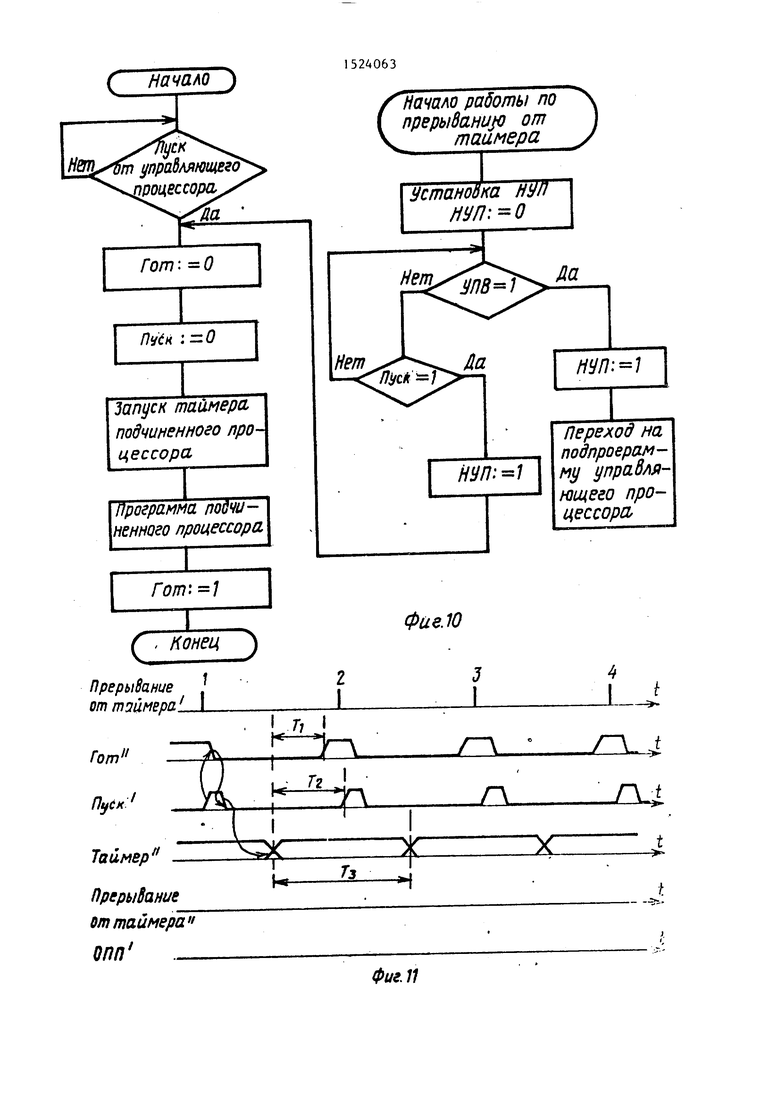

Если все процессорные устройства 1,2,,,о, в системе работают правильно, то временная диаграмма обмена сигналами между управляюпшм устройством 1,1 и каждым подчиненным процессорным устройством соответствует фиг,12,

На диаграмме сигналы, вырабатываемые в управляющем устройстве 1,1, отмечены одним штрихом, а в подчиненном - двумя щтрихами.

Период времени Т соответствует времени выполнения основной программы в подчиненном процессорном устройстве 1,1, а Т - промежуток времени от момента запуска таймера подчинен1,1 останавливает таймер 27о 1 и пере- ного процессорного устройства до поступления следующей команды Пуск от управляющего процессорного устройства 1,1,, Т - расчетное время работы таймера подчиненного процессорного устройства 1, Этот таймер должен выходит к программе инициализации системы При s-toM осуществляется перераспределение задач для оставшихся процессорных устройств, загрузка данных и программ в эти процессорные устройства, упорядочивания номеров и числа оставшихся процессорных устройств. Затем осуществляется их запуск и эапуск таймера управляющего процессорного устройства 1,1,, после чего последнее переходит на выполнение своей основной программы.

Если при выполнении подпрограммы по прерыванию от таймера управляющего устройства 1 отказавшие процессоры отсутствуют, то осуществляется поочередный запуск подчиненных процессорных устройств и возврат из подпрограммы,

Каждое подчиненное устройство 1,2, о..,1оП работает в соответствии с алгоритмом, представленным на фиГоП,

40

45

50

55

рабатывать запрос на прерывание через промежуток времени, больше чем

т -г

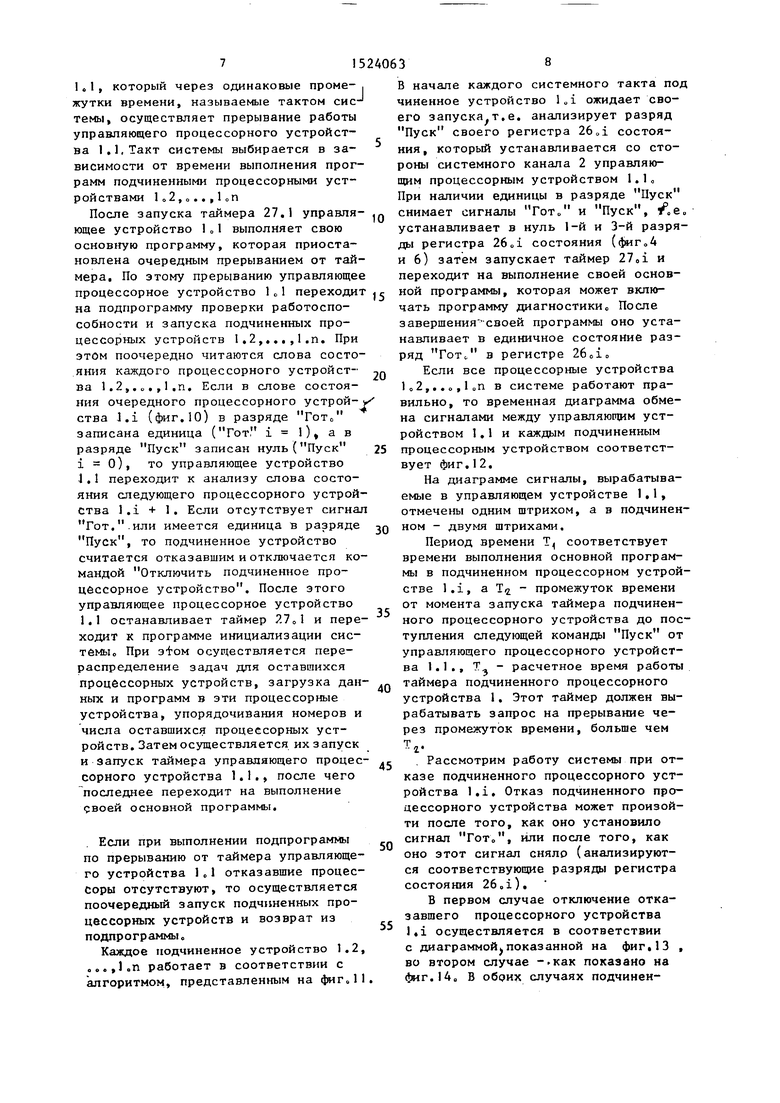

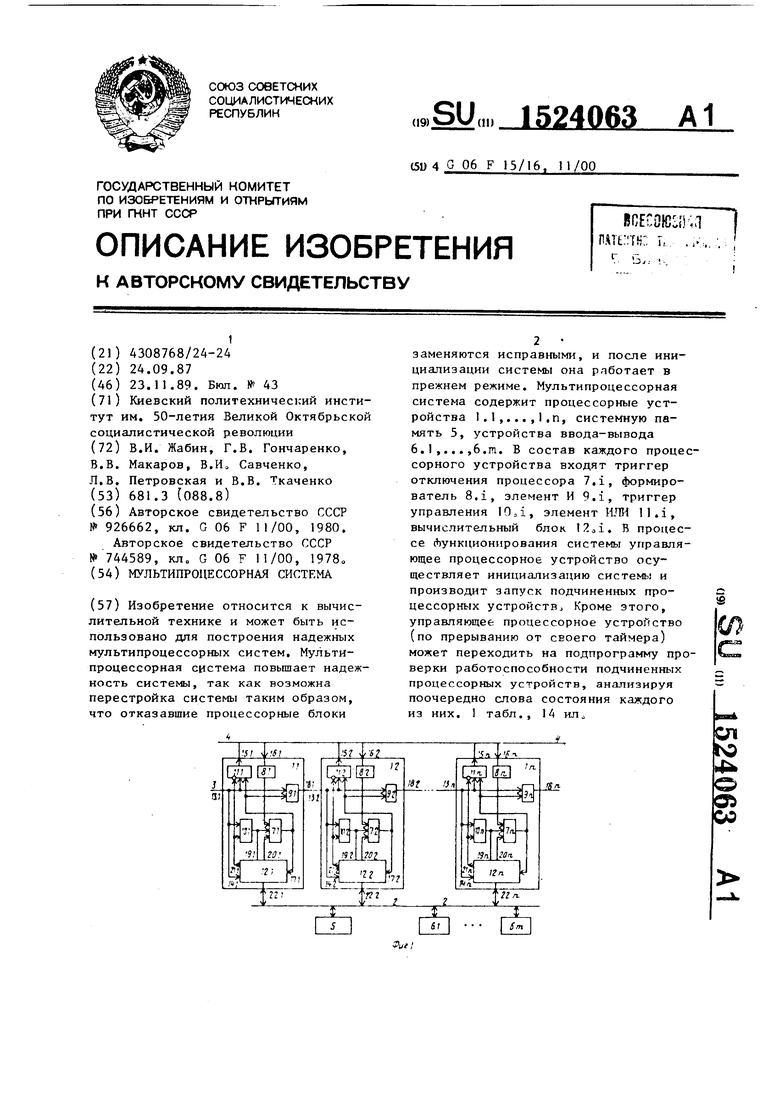

. Рассмотрим работу системы при отказе подчиненного процессорного устройства 1,1, Отказ подчиненного процессорного устройства может произойти после того, как оно установило сигнал ГоТо, или после того, как оно этот сигнал сняло (анализируются соответствующие разряды регистра состояния 26л).

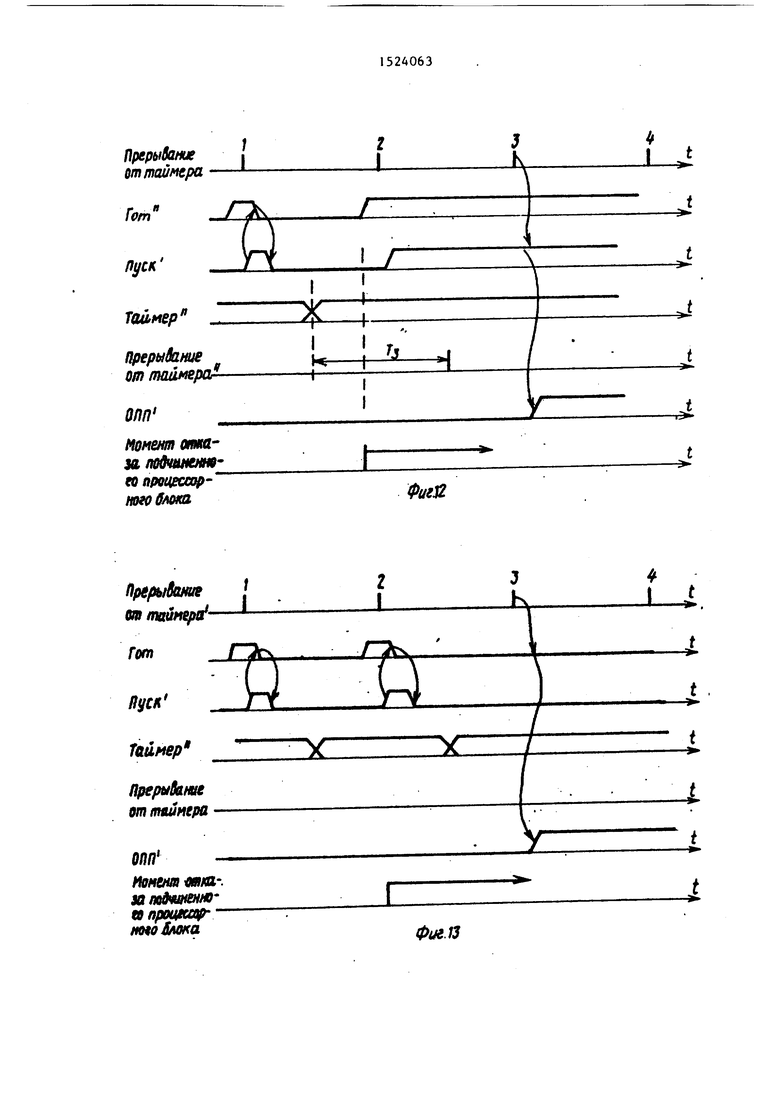

В первом случае отключение отказавшего процессорного устройства 1,1 осуществляется в соответствии с диаграммой показанной на фиг,13 , во втором случае показано на фиг,14о В обрих случаях подчинен

20

25

30

чать программу диагностики После заверщения своей программы оно устанавливает в единичное состояние разряд Гот в регистре 26oi(,

Если все процессорные устройства 1,2,,,о, в системе работают правильно, то временная диаграмма обмена сигналами между управляюпшм устройством 1,1 и каждым подчиненным процессорным устройством соответствует фиг,12,

На диаграмме сигналы, вырабатываемые в управляющем устройстве 1,1, отмечены одним штрихом, а в подчиненном - двумя щтрихами.

Период времени Т соответствует времени выполнения основной программы в подчиненном процессорном устройстве 1,1, а Т - промежуток времени от момента запуска таймера подчинен5

0

5

рабатывать запрос на прерывание через промежуток времени, больше чем

т -г

. Рассмотрим работу системы при отказе подчиненного процессорного устройства 1,1, Отказ подчиненного процессорного устройства может произойти после того, как оно установило сигнал ГоТо, или после того, как оно этот сигнал сняло (анализируются соответствующие разряды регистра состояния 26л).

В первом случае отключение отказавшего процессорного устройства 1,1 осуществляется в соответствии с диаграммой показанной на фиг,13 , во втором случае показано на фиг,14о В обрих случаях подчиненное устройство выходит из строя посл завершения nporpasjMbi в первом такте

Как видно из диаграмм, команда . Отключить подчиненное процессорное устройство вырабатывается в начале третьего такта, поскольку в первом случае не снят сигнал Пуск, а во втором елучае не выставлен сигнал Гот, в регистре 26oi состояния (алгоритм работы управляющего процессорного устройства, фиг.10)о В первом случае (фиг,13) таймер 27«i отказавшего подчиненного процессорного устройства l.i через промежУ ток времени Tj может выставить запрос на прерывание работы отказавшего устройства 1,1, Этот запрос не оказывает на работу всей системы влияния, так как отказавшее процессорное устройство l.i отключено в следующем системном такте управляющим процессорным устройством 1з1,

Таким образом, отключение отказавшего подчиненного процессорного устройства lai осуществляется программно путем анализа слова состояния этого процессора в начале каждого системного такта. В отключенном процессорном устройстве с помощью сигнала на выходе 20.1 (путем установки единицы в 3-й разряд регистра 26.1) обеспечивается единичный потенциал на выходе триггера 7.1 отключения процессора, который открывает по одному .из входов элемент 9.1, за счет чего обеспечивается передача сигнала с входа 13.1 на выход 18о1 от казав- шего процессорного устройства 1

Кроме того, сигнал с выхода триггера 7.1 отключает от системного канала 2 обмена информацией вычислительный блок 12.1, поступая на вход 17.1 этого блока, и осуществляет поступление единичного сигнала на один из входов элемента 11 Да За сче этого отказавшее подчиненное процессорное устройство lai не влияет на состояние сигнала на шине 4 отключения управляющего процессора.

Отказ и замена отказавшего управляющего процессорного устройства 1.1 осуществляются в системе программно- аппаратным способом следующим образом.

В исходном состоянии функцию управляющего процессорного устройства выполняет процессорное устройство 1.1, на входе 13о1 которого присутст5

0

вует логическая 1 (фиг,1,2). При включении системы производится начальная установка регистров 26,1 , оэ,,26,п состояний. Схемным образом все разряды этих регистров, кроме четвертого, устанавливаются в нулевое состояние, а четвертый разряд - в единичное состояние о Кроме этого, на выходах

Q триггеров отключения процессоров 7.1,..а,7.п устанавливается нулевой потенциал (цепи установки исходного состояния на фиг.1 и 2 условно не показаны).

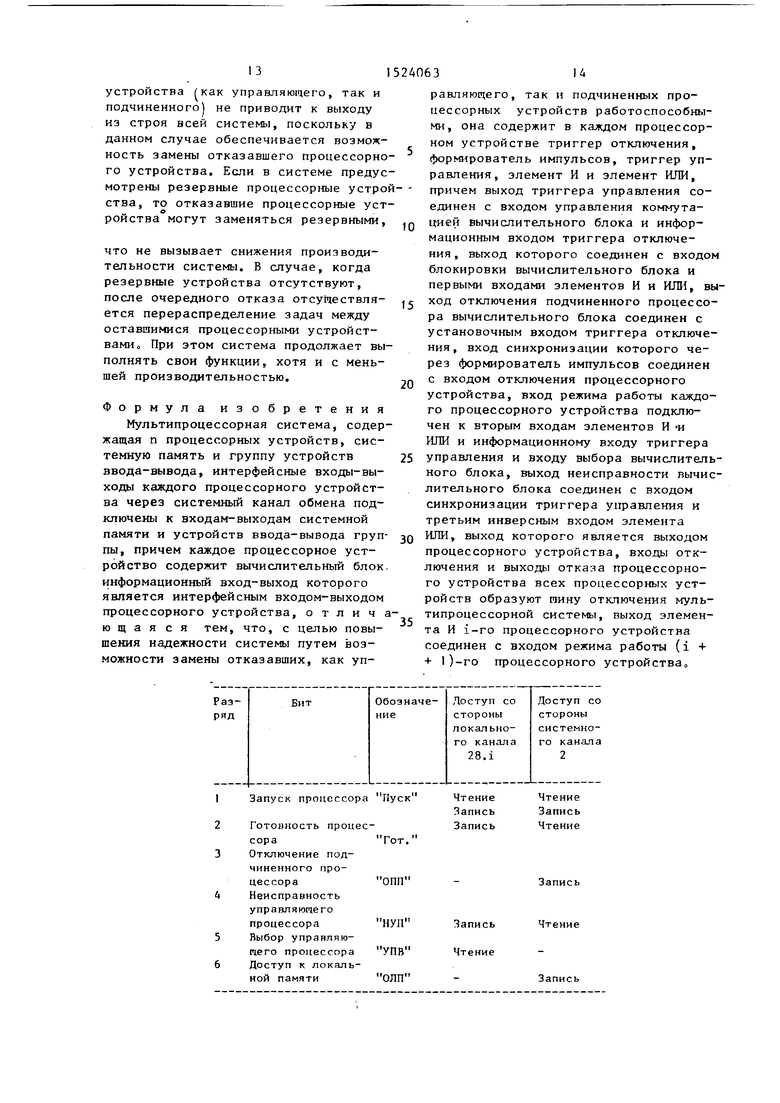

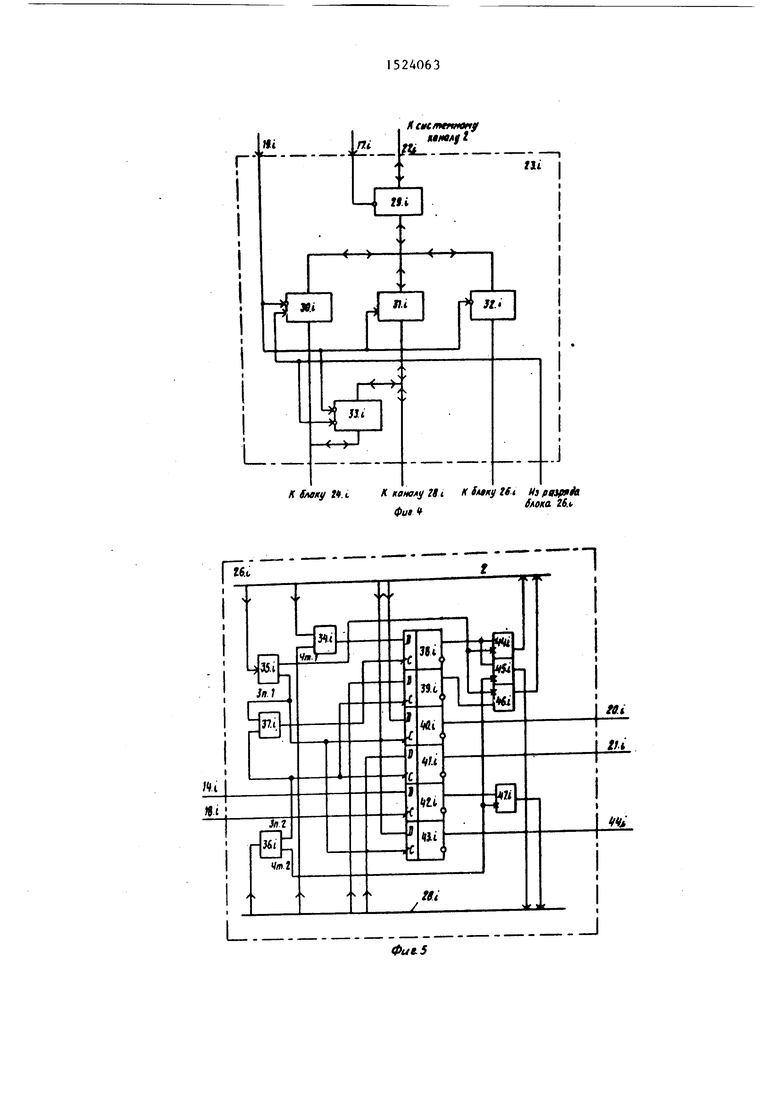

Затем 5-й разряд регистра 26,1 состояния фиг.6) процессорного устройства 1.1 устанавливается в единичное состояние сигналом на входе 13.4 процессорного устройства 1,1, который через вход 14il вычислительного блока 12о1 поступает на соответствующий разряд регистра 26,1 состояния (например, на вход D-триггера, тактирую- 1ЦИЙ вход которого соединен с генера5 тором синхросигналов). В остальных процессорных устройствах 1о2,.оо,1.п на входах 13.2,о..,13.п присутствуют нулевые потенциалы, так как все элементы 9.1,...,9.п закрыты, вследст0 вие чего 5-й разряд регистров состояний этих устройств остается в нуле. Только в процессорном устройстве 1,1 триггер lOol устанавливается н единицу, так как при единичном потенциале с выхода 2К1 вычислительного блока 12.1, поступающем на тактирующий вход триггера 10.1, последний пропускает единичный сигнал со своего информационного входа на выход (например, в качестве триггеров 10.1,.,., 10.П можно использовать D-триггеры, управляемые уровнем тактирующего сигнала, которые при единичном потенциале пропускают информацию с входа D

с на выход, а при переходе к нулевому уровню защелкивают в триггерах информацию, имеющуюся на входе непосредственно перед этим).

5

0

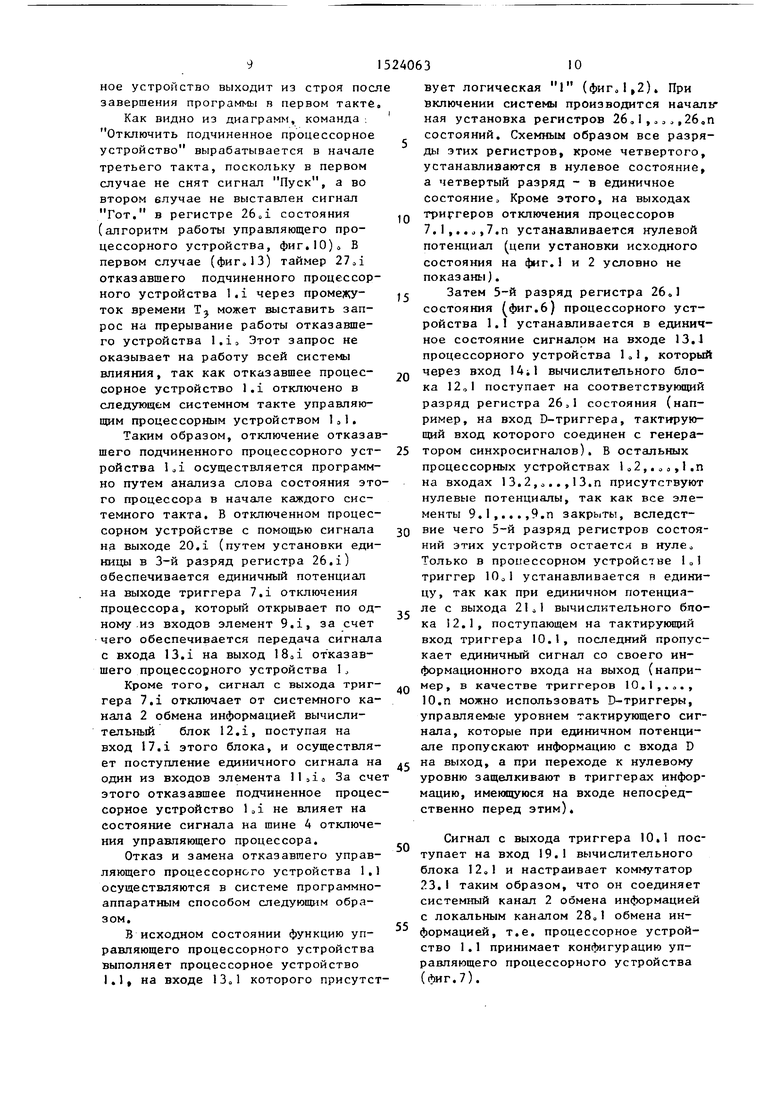

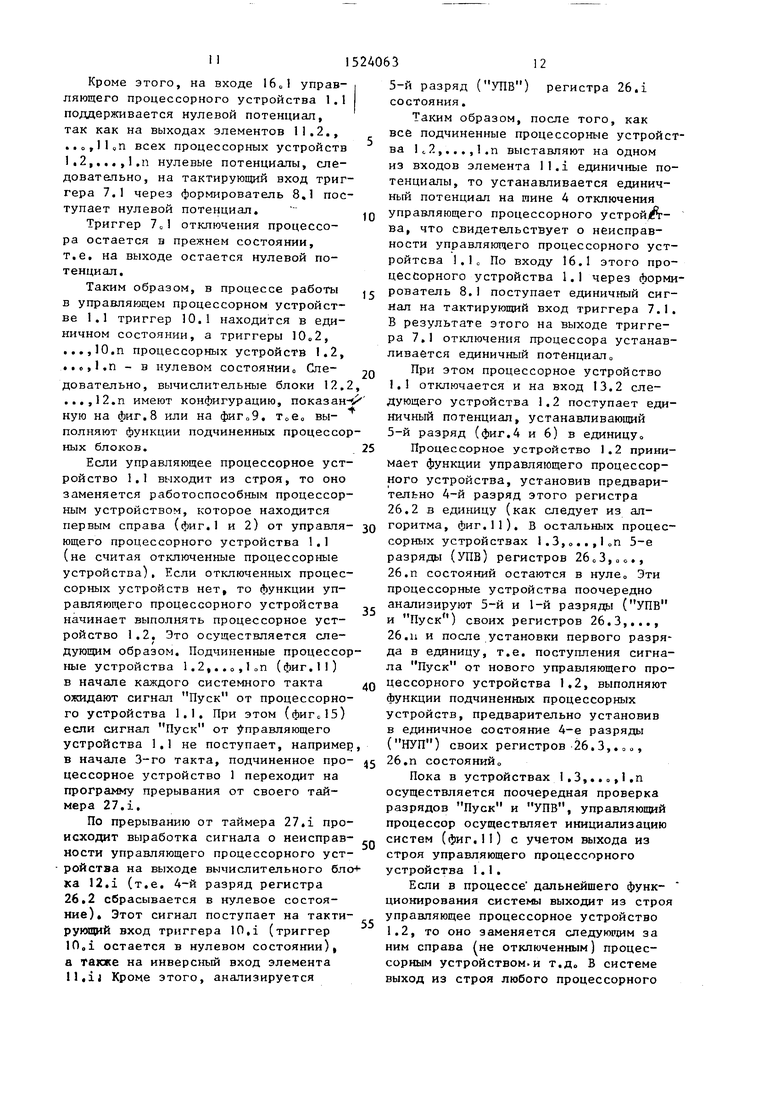

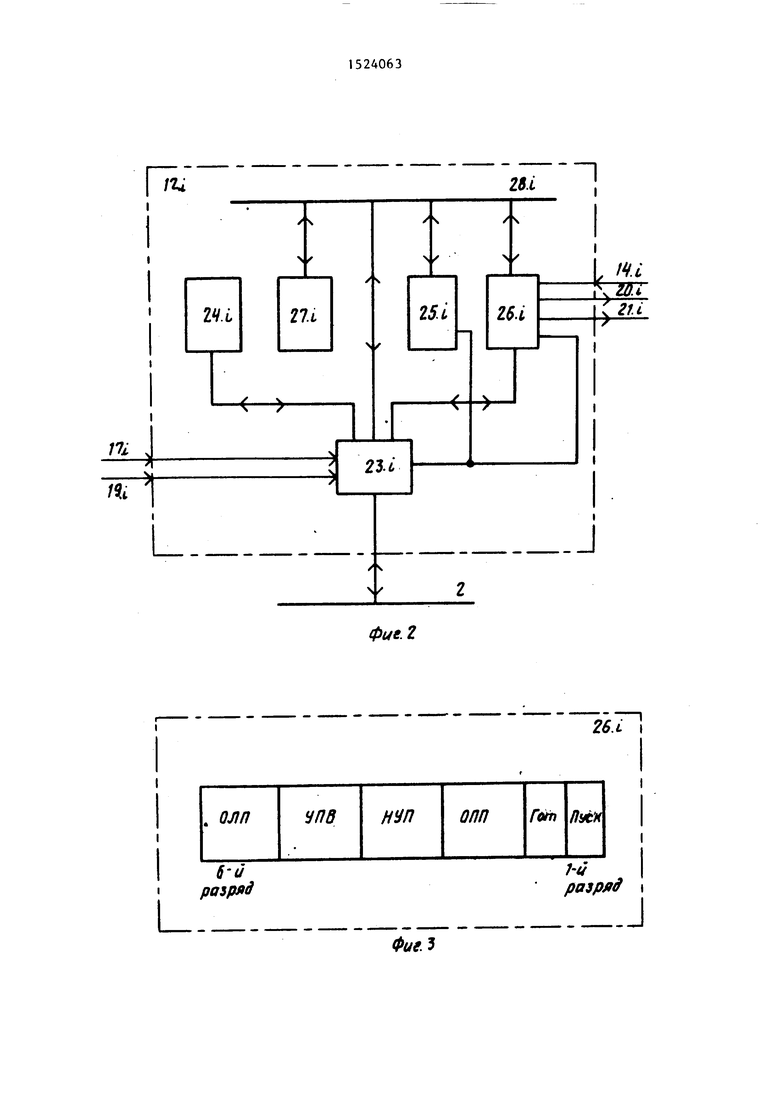

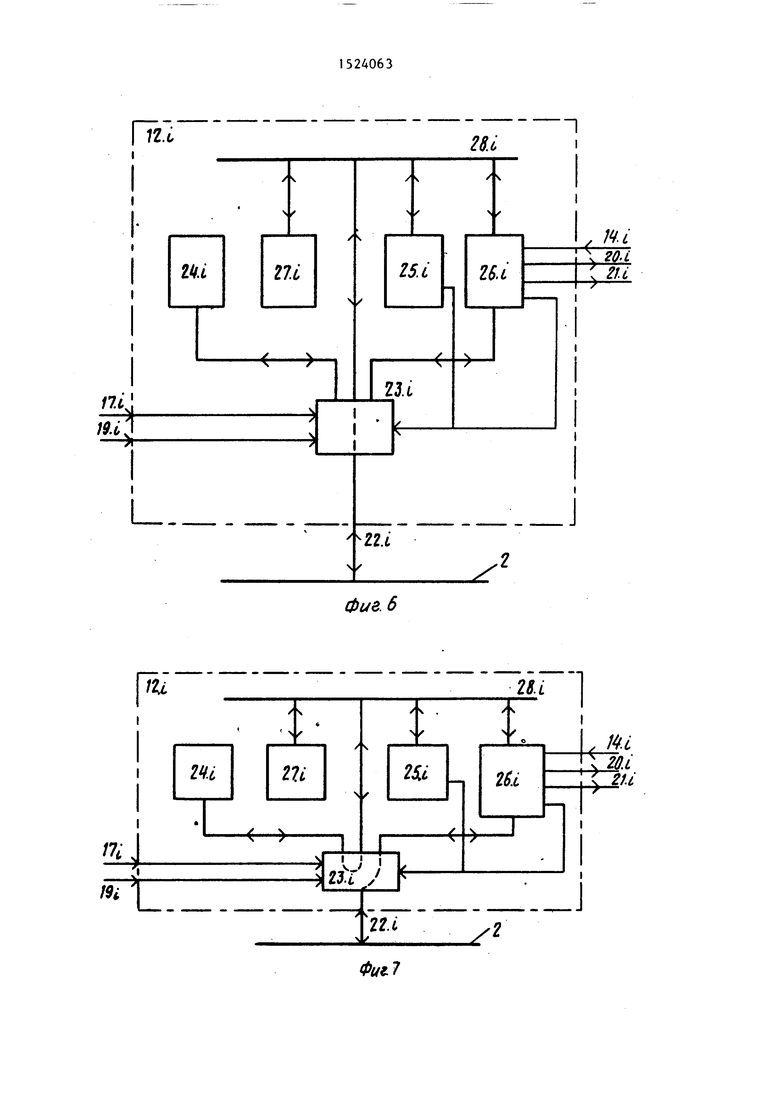

Сигнал с выхода триггера 10.1 поступает на вход 19.1 вычислительного блока 12,1 и настраивает коммутатор 23.I таким образом, что он соединяет системный канал 2 обмена информацией с локальным каналом 28,1 обмена информацией, т.е. процессорное устройство 1.1 принимает конфигурацию управляющего процессорного устройства (фиг.7).

11

Кроме этого, на входе I6gl управляющего процессорного устройства 1.1 поддерживается нулевой потенциал, так как на выходах элементов 11.2., ..о,11дП всех процессорных устройств It2,...,l.n нулевые потенциалы, следовательно, на тактирующий вход триггера 7.1 через формирователь 8,1 поступает нулевой потенциал.

Триггер 7о1 отключения процессора остается в прежнем состоянии, т.е. на выходе остается нулевой потенциал.

Таким образом, в процессе работы в управляющем процессорном устройстве 1.1 триггер 10.1 находится в единичном состоянии, а триггеры 10„2, ...,10.п процессорных устройств 1.2, ..о,1.п - в нулевом состояниио Следовательно, вычислительные блоки 12.2 ...,12.п имеют конфигурацию, показанную на фиг.8 или на фиГо9. Тово выполняют функции подчиненных процессорных блоков.

Если управляющее процессорное устройство 1.1 выходит из строя, то оно заменяется работоспособным процессор

Процессорное устройство 1.2 принимает функции управляющего процессорного устройства, установив предварительно 4-й разряд этого регистра 26.2 в единицу (как следует из апным устройством, которое находится первым справа (фиг,1 и 2) от управля- зо горитма, фиг.11). В остальных процес- ющего процессорного устройства 1.1 сорных устройствах 1.3,„..,1„п 5-е (не считая отключенные процессорные разряды (УПВ) регистров 26 о 3,о о,,

26.п состояний остаются в нулео Эти процессорные устройства поочередно анализируют 5-й и 1-й разряды (УПВ и Пуск) своих регистров 26,3,,.., 26.11 и после установки первого разряда в единицу, т.е, поступления сигнала Пуск от нового управляющего процессорного устройства 1,2, выполняют функции подчиненных процессорных устройств, предварительно установив

35

устройства), Если отключенных процессорных устройств нет то функции управляющего процессорного устройства начинает выполнять процессорное устройство 1.2. Это осуществляется следующим образом. Подчиненные процессорные устройства 1.2,,,о,1оП (фиг,II) в начале каждого системного такта Q ожидают сигнал Пуск от процессорного устройства 1.1. При этом (фиго15)

если сигнал Пуск от Управляющего в единичное состояние 4-е разряды устройства 1.1 не поступает, например, (НУП) своих регистров 26.3,,о«, в начале 3-го такта, подчиненное про- j 26,п состояний

цессорное устройство 1 переходит на программу прерывания от своего таймера 27,1.

По прерыванию от таймера 27.1 происходит выработка сигнала о неисправности управляющего процессорного устройства на выходе вычислительного бло+ ка 12,1 (т,е. 4-й разряд регистра 26,2 сбрасывается в нулевое состояние). Этот сигнал поступает на такти- руияций вход триггера 10.1 (триггер lOoi остается в нулевом состоянии), а также на инверсный вход элемента ll,ij Кроме этого, анализируется

50

55

Пока в устройствах I,3,,,о,1,п осуществляется поочередная проверка разрядов Пуск и УПВ, управляющий процессор осуществляет инициализацию систем (фиг,II) с учетом выхода из строя управляющего процессорного устройства 1,1.

Если в процессе дальнейшего функционирования системы выходит из строя управляющее процессорное устройство 1.2, то оно заменяется следуюрдам за ним справа (не отключенным) процессорным устройством.и т.До В системе выход из строя любого процессорного

10

2406312

5-й разряд (УПВ) регистра 26.1 состояния.

Таким образом, после того, как все подчиненные процессорные устройства 1о2,...,1.п выставляют на одном из входов элемента ll.i единичные потенциалы, то устанавливается единичный потенциал на тине 4 отключения управляющего процессорного устройЛ-

ва, что свидетельствует о неисправности управляющего процессорного уст- ройтсва 1.1 о По входу 16.1 этого процессорного устройства 1.1 через формирователь 8.1 поступает единичный сигнал на тактирующий вход триггера 7.1. В результате этого на выходе триггера 7,1 отключения процессора устанавливается единичный потенциал о

При этом процессорное устройство 1.1 отключается и на вход 13.2 следующего устройства 1.2 поступает единичный потенциал, устанавливающий 5-й разряд (фиг,4 и 6) в единицу

Процессорное устройство 1.2 принимает функции управляющего процессорного устройства, установив предварительно 4-й разряд этого регистра 26.2 в единицу (как следует из апгоритма, фиг.11). В остальных процес- сорных устройствах 1.3,„..,1„п 5-е разряды (УПВ) регистров 26 о 3,о о,,

0

5

Пока в устройствах I,3,,,о,1,п осуществляется поочередная проверка разрядов Пуск и УПВ, управляющий процессор осуществляет инициализацию систем (фиг,II) с учетом выхода из строя управляющего процессорного устройства 1,1.

Если в процессе дальнейшего функционирования системы выходит из строя управляющее процессорное устройство 1.2, то оно заменяется следуюрдам за ним справа (не отключенным) процессорным устройством.и т.До В системе выход из строя любого процессорного

131524063

ройства как управляющего, так и чиненного| не приводит к выходу строя всей системы, поскольку в ном случае обеспечивается возможть замены отказавшего процессорноустройства. Если в системе предусрены резервные процессорные устройа, то отказавшие процессорные устства могут заменяться резервными,

10

ра це ми но ра пр ед ци ма ни бл пе хо ра ус ни ре с ус го че ИЛ уп но ли си тр ИЛ пр лю го ро ти та со +

что не вызывает снижения производительности системы. В случае, когда резервные устройства отсутствуют, после очередного отказа отсуществля- ется перераспределение задач между оставшимися процессорными устройствами , При этом система продолжает выполнять свои функции, хотя и с меньшей производительностью.

Формула изобретения

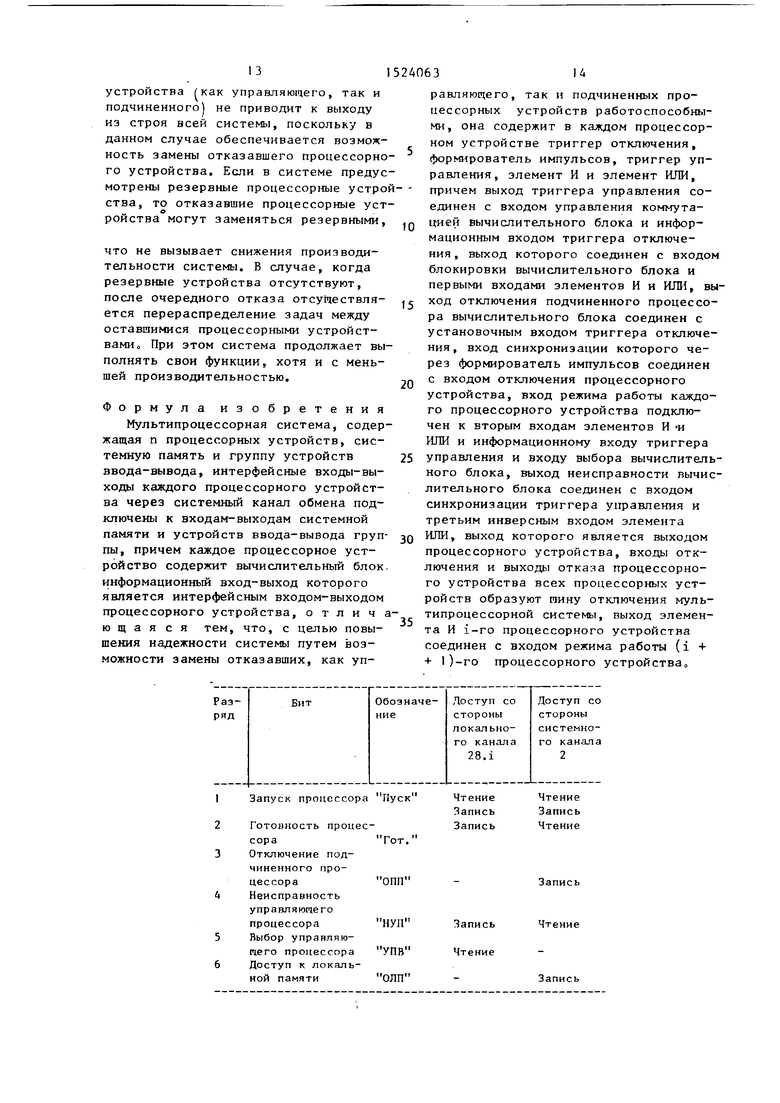

Мультипроцессорная система, содержащая п процессорных устройств, системную память и группу устройств ввода-вывода, интерфейсные входы-выходы каждого процессорного устройства через системный канал обмена подключены к входам-выходам системной памяти и устройств ввода-вывода группы, причем каждое процессорное устройство содержит вычислительный блок информационный вход-выход которого является интерфейсным входом-выходом процессорного устройства, отличющая с я тем, что, с целью повышения надежности системы путем возможности замены отказавших, как уп14

0

5

0

5

0

5

равляющего, так и подчиненных процессорных устройств работоспособными, она содержит в каждом процессорном устройстве триггер отключения, формирователь импульсов, триггер управления, элемент И и элемент ИЛИ, причем выход триггера управления соединен с входом управления коммутацией вычислительного блока и информационным входом триггера отключения , выход которого соединен с входом блокировки вычислительного блока и первыми входами элементов И н ИЛИ, выход отключения подчиненного процессора вычислительного блока соединен с установочным входом триггера отключения, вход синхронизации которого через формирователь импульсов соединен с входом отключения процессорного устройства, вход режима работы каждого процессорного устройства подключен к вторым входам элементов И -и ИЛИ и информационному входу триггера управления и входу выбора вычислительного блока, выход неисправности вычислительного блока соединен с входом синхронизации триггера у1фавления и третьим инверсным входом элемента ИЛИ, выход которого является выходом процессорного устройства, входы отключения и выходы отказа процессорного устройства всех процессорных устройств образуют пину отключения мультипроцессорной системы, выход элемента И i-ro процессорного устройства соединен с входом режима работы (1 + + 1)-го процессорного устройства

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная вычислительная система | 1991 |

|

SU1820391A1 |

| Мультипроцессорная система | 1990 |

|

SU1732351A1 |

| Устройство для сопряжения процессоров с общей шиной мультипроцессорной системы | 1988 |

|

SU1571606A1 |

| Устройство обработки данных для многопроцессорной системы | 1988 |

|

SU1683039A1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1989 |

|

RU1819116C |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

| Устройство для обработки запросов | 1989 |

|

SU1688248A1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Устройство для синхронизации вычислительной системы | 1985 |

|

SU1684785A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения надежных мультипроцессорных систем. Мультипроцессорная система повышает надежности системы, так как возможна перестройка системы таким образом, что отказавшие процессорные блоки заменяются исправными, и после инициализации системы она работает в прежнем режиме. Мультипроцессорная система содержит процессорные устройства 1.1,....., 1.N, системную память 5, устройства ввода-вывода 6.1,...,6.M. В состав каждого процессорного устройства входят триггер отключения процессора 7.I, формирователь 8.I, элемент И 9.I, триггер управления 10.I, элемент ИЛИ 11.I, вычислительный блок 12.I. В процессе функционирования системы управляющее процессорное устройство осуществляет инициализацию системы и производит запуск подчиненных процессорных устройств. Кроме того, управляющее процессорное устройство /по прерыванию от своего таймера/ может переходить на подпрограмму проверки работоспособности подчиненных процессорных устройств, анализируя поочередно слова состояния каждого из них. 14 ил.

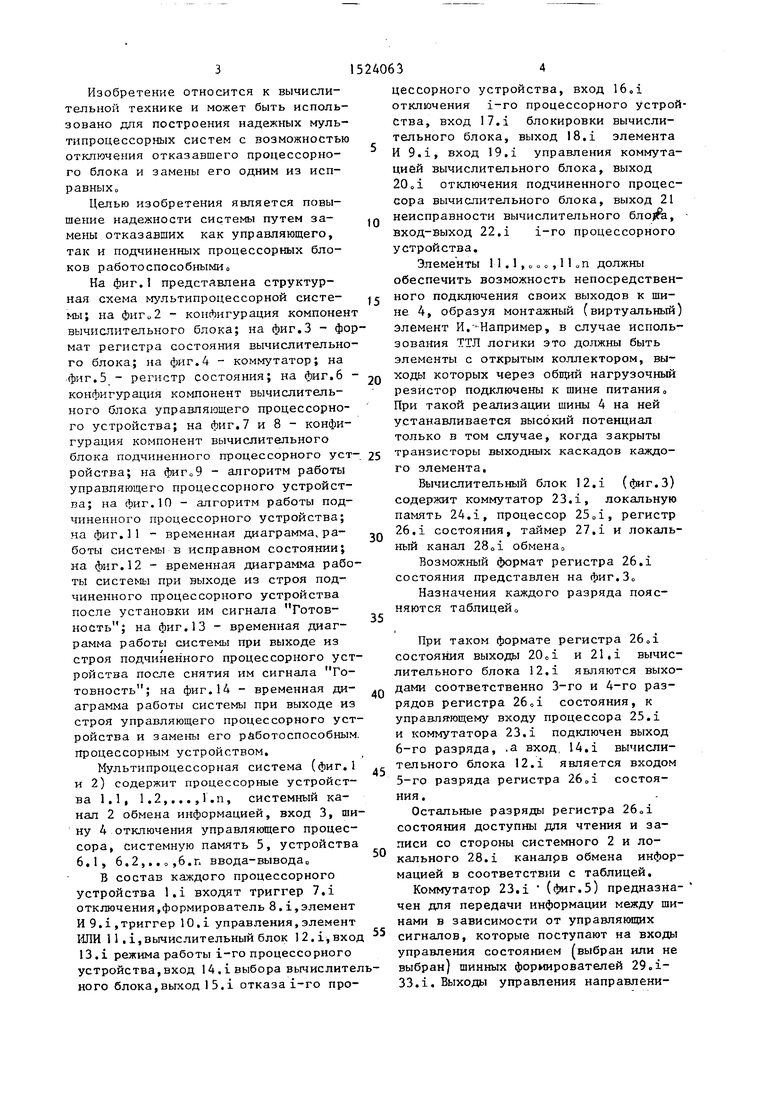

чиненного процессораНеисправность управляющего процессора Выбор управляющего процессора Доступ к локапьной памяти

Запись

Запись Чтение

Чтение

ОЛП

Запись

L.

6 U

разряд

1

Фие.2

2В. i I

/V I разрла I

I

Фиг.

ш

Г

Wt

-(

я iAOKjf М.Iл наноАу ill К Su/ty ISt Us paV

A ,,бмка U.t,

9ut

Z6.t

II

Фut.5

ш

Htutmtrwony МММ I

/и:

ч-)(

г л.

1

Фиг. 6

F

/ ч

IJ:L X

ч

/ ч

N

25J.

/ ч /

1

ш

Mi ги

X

гг.(.

I

/г

Фиг.7

I Iti

2U 1

м оЛлока

Фиг.13

| Адаптивная система обработки данных | 1980 |

|

SU926662A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительная структура | 1978 |

|

SU744589A1 |

Авторы

Даты

1989-11-23—Публикация

1987-09-24—Подача