СО

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультипроцессорная система | 1990 |

|

SU1732351A1 |

| Мультипроцессорная система | 1987 |

|

SU1524063A1 |

| Устройство для сопряжения процессоров с общей шиной мультипроцессорной системы | 1988 |

|

SU1571606A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1987 |

|

SU1462344A1 |

| Микропроцессорная система для программного управления технологическими процессами | 1987 |

|

SU1418653A1 |

| Устройство для операций над матрицами | 1990 |

|

SU1784997A1 |

| Устройство обработки данных для многопроцессорной системы | 1988 |

|

SU1683039A1 |

| Анализатор сопротивлений систем промышленного электроснабжения | 1985 |

|

SU1282021A1 |

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МАРШРУТА СООБЩЕНИЯ | 2000 |

|

RU2175144C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих систем. Целью изобретения является повышение надежности в работе за счет сохранения работоспособности системы при кратных отказах и сокращения отключения управляющего устройства при разных длинах программ, выполняемых подчиненными устройствами обработки информации. Система содержит Н устройств обработки информации, М устройств ввода-вывода и запоминающее устройство, причем каждое устройство обработки информации содержит вычислительный блок, первый и второй блоки отключения, формирователь импульсов, триггер управления и элемент И. 2 ил.

Изобретение относится к вычислительной технике и может быть использовано при построении надежных мультиплексорных систем с возможностью отключения отказавшего процессорного блока и замены его исправным.

Целью изобретения является повышение надежности в работе за счет сохранения работоспособности системы при кратных отказах и сокращения времени отключения управляющего устройства при разных длинах программ, выполняемых подчиненными устройствами обработки информации.

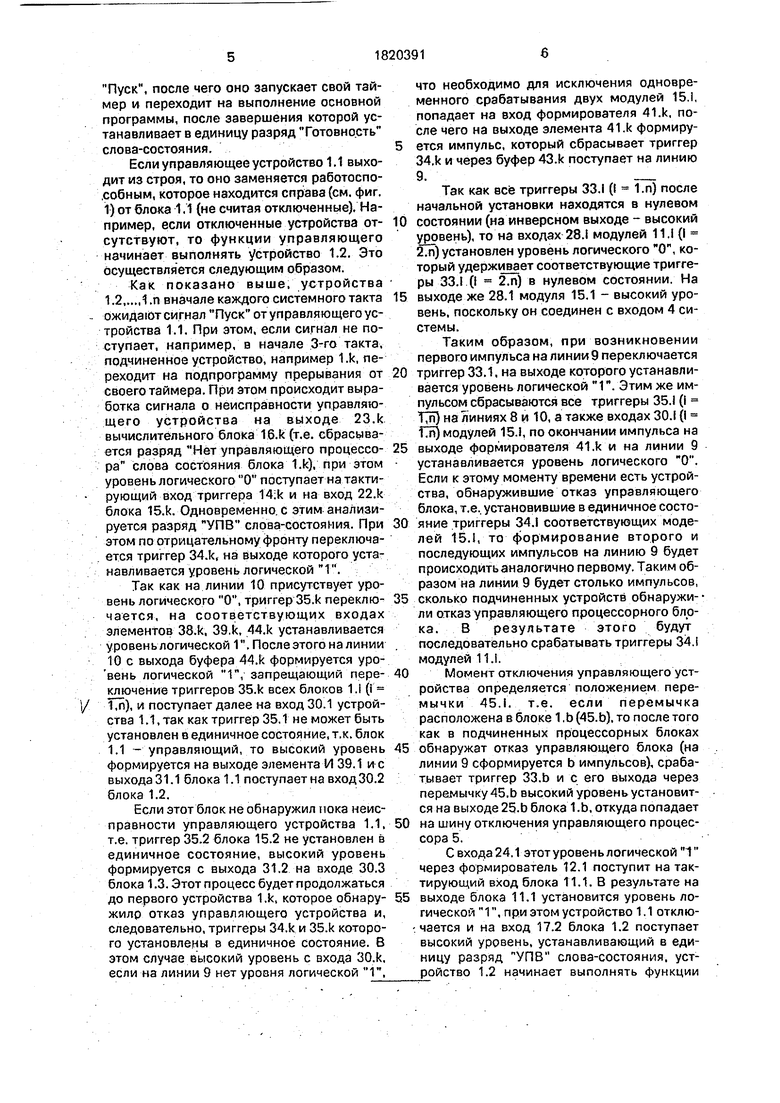

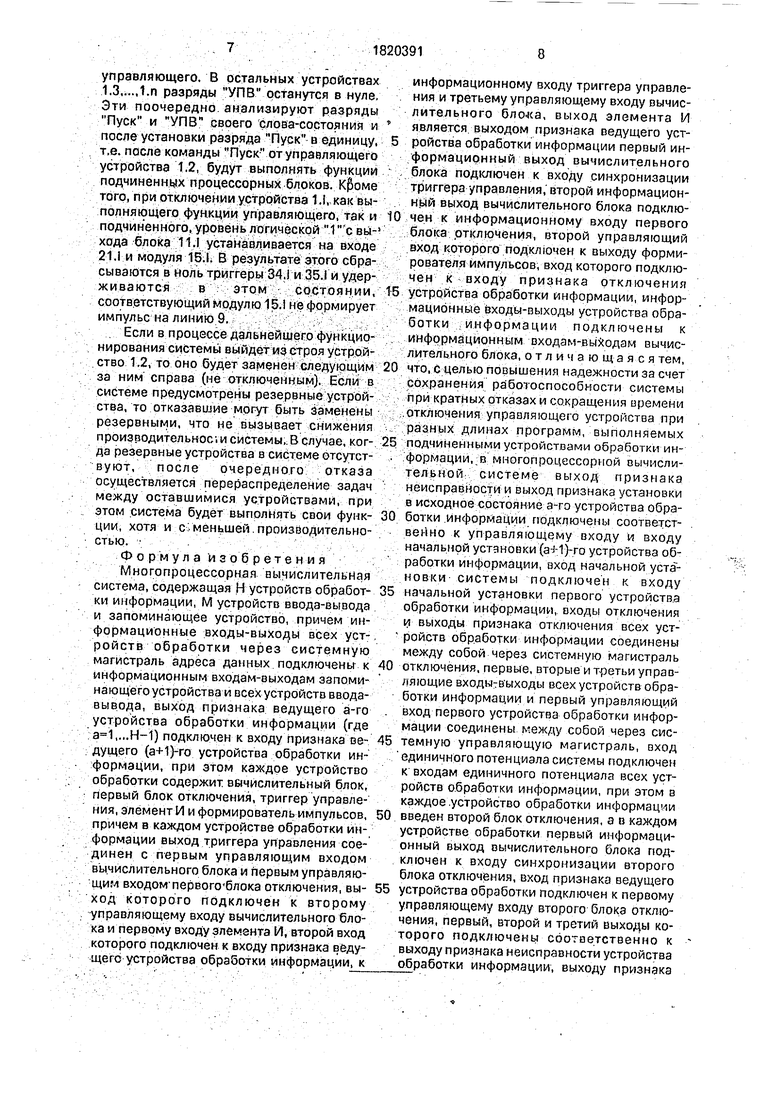

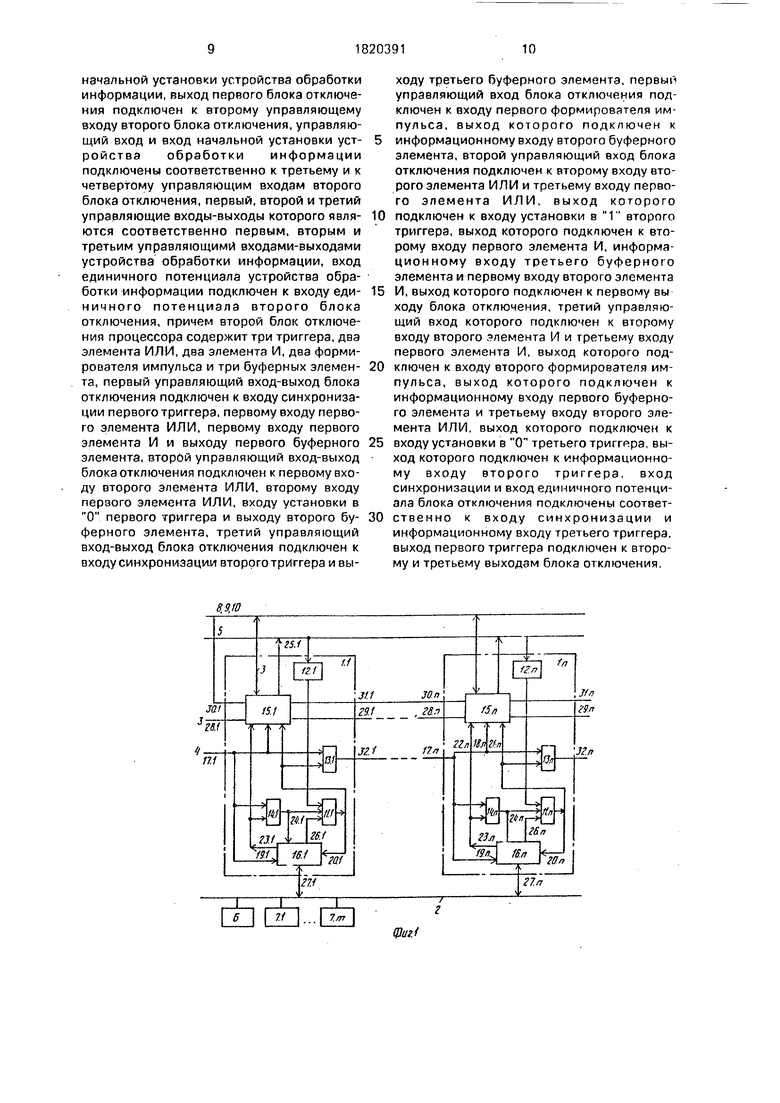

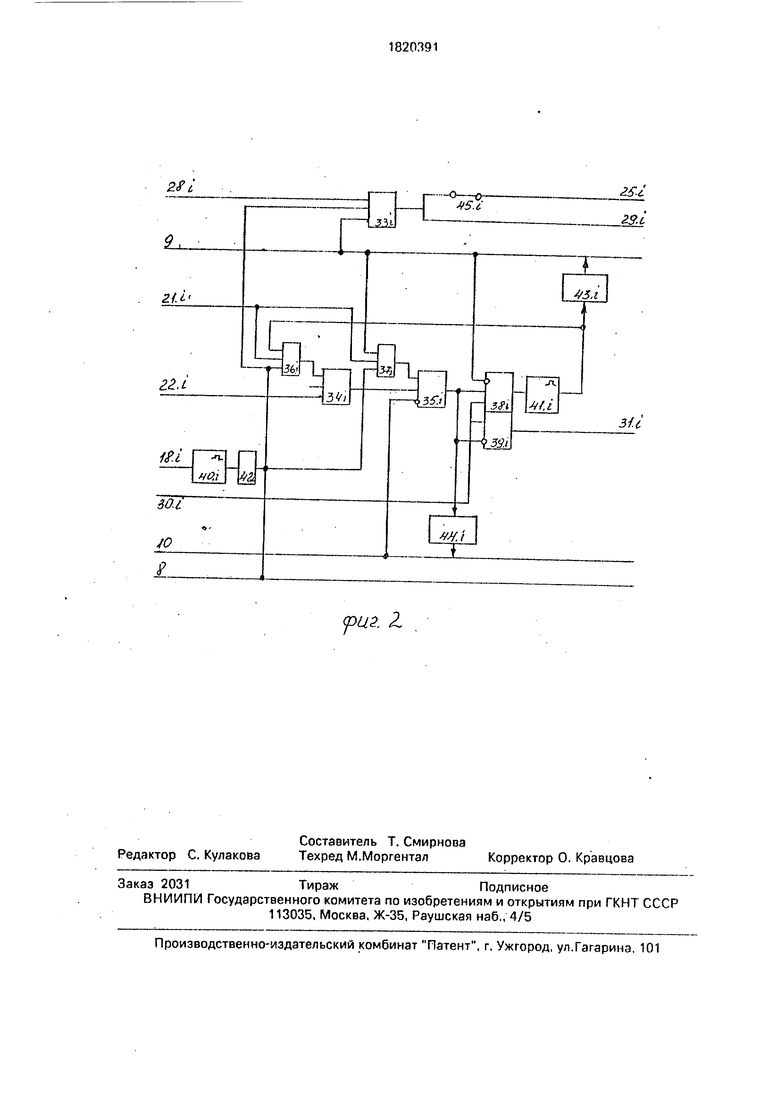

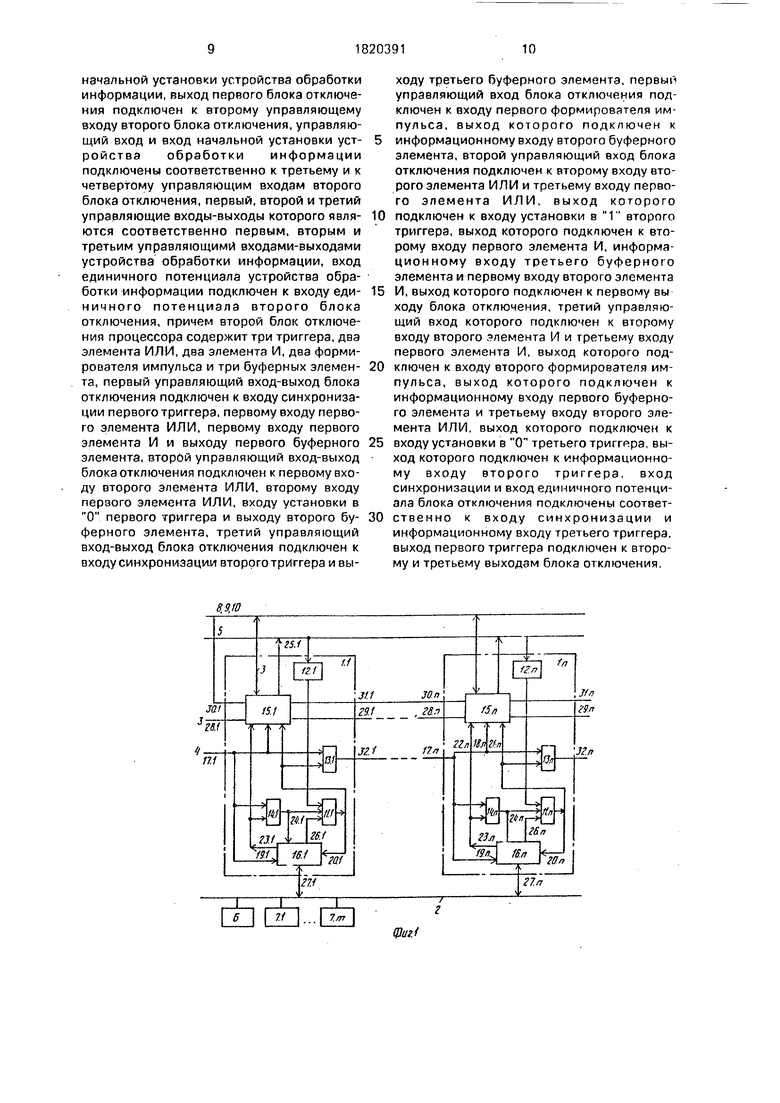

На фиг. 1 дана структурная схема многопроцессорной вычислительной системы; на фиг. 2 - структурная схема модуля отключения.

Многопроцессорная вычислительная система, представленная на фиг. 1. содержит устройства обработки информации 1.1. 1.2...., 1 .п. системный канал 2 обмена информацией, входы 3 и 4, шину 5 отключения управляющего процессора, запоминающее устройство 6, устройства ввода-вывода 7.1,...,7т. вспомогательную шину 8, 9, 10.

В состав каждого процессорного блока 1.1 входят первый блок отключения процессора 11,1. формирователь импульсов 12.1, элемент И 13.J, триггер управления 14.1, второй блок отключения 15.1, вычислительный блок 16.1.

Второй блок отключения (см. фиг. 2) содержит первый триггер 33.1, второй триггер 34.1, третий триггер 35.1, первый элемент ИЛИ 36.1, второй элемент ИЛИ 37.1, первый элемент И 38.1. второй элемент И 39.1, первый формирователь импульса 40.1, второй формирователь импульса 41.1, первый бусо ю о со о

ферный элемент 42.1, второй буферный элемент 43.1, третий буферный элемент 44.1.

Система работает следующим образом.

Устройство обработки информации 1.1, например, на вход 17.1 которого подается высокий уровень с входа 3 системы, выполняет функции управляющего блока. Кроме того, в момент установления устройства обработки информации 1.1 статуса управляющего устанавливаются в исходное состояние первые блоки отключения 11.1 всех процессорных блоков 1.

Это происходит следующим образом.

При возникновении на входе 17.1 блока 1.1 уровня логической 1 (это означает, что данный блок должен принять функции управляющего, если, конечно, он не был отключен ранее), на выходе формирователя 40.1 формируется импульс, который с выхода буфера 42.1 поступает в линию 8 и сбра- . сывэет триггеры 33.1-35.1 во всех блоках 1.1. Длительность этого импульса должна быть достаточна для надежного сброса этих триггеров, т.е. ги tip, где tTp - время переключения триггера. Через время (3-4)Стр схемы модулей 11.1 надежно установятся в исходное состояние: выходы триггеров 33.1

- 35.1 (i 17п) и линии 8-10 будут находиться в состоянии логического О. Так как ty меньше длительности выполнения любой команды блоком 12.1 при условии реализации всех блоков 1.1 (I Tjrij на единой элементной базе, то процесс установки в исходное состояние модулей 11.1 завершится до начала работы управляющего блока 1.1 и, следовательно, не повлияет на работу системы. На входах 17.2,..., 17.п процессорных блоков 1,2,..., 1.п устанавливается низкий уровень

- эти устройства обработки информации являются подчиненными.

Управляющее устройство 1.1 имеет доступ к запоминающему устройству 6, устройствам ввода-вывода 7.1,...,7,т. а также через соответствующие порты ввода-вывода (шины 27.1,,..,27.п)- к подчиненным устройствам 1.2,...,1.п. Оно может передавать команды для подчиненных устройств 1.2,...,1..п и читать слово состояния этих про- . цессорных блоков. Соответствующими командами осуществляется запуск процессорных блоков 1.2,...,1.п, отключение при неисправности одного или нескольких подчиненных процессорных блоков, а также обеспечивается доступ к их внутренней памяти.

В начале работы системы управляющее устройство 1.1 осуществляет инициализацию, т.е. загружает данные и программы во внутреннюю память подчиненных процессорных блоков и производит их запуск. Для загрузки данных и программ в подчиненные устройства 1.2,,,.,1.п подается команда Открыть внутреннюю память, затем осуществляются циклы обращения к открытой внутренней памяти, после чего внутренняя память закрывается командой Закрыть внутреннюю память. После этого по команде Пуск, которая поступает поочередно на

каждое устройство 1.2,.,.,1.п, подчиненные устройства начинают выполнять свои программы. Далее запускается таймер в управляющем устройстве 1.1, который через одинаковые промежутки времени, называе5 мые тактом системы, осуществляет прерывание работы управляющего устройства 1.1. Такт системы выбирается в зависимости от времени выполнения программ подчиненными устройствами 1.2,...,1 .п.

0 После запуска таймера управляющее устройство 1. Г выполняет свою основную программу, которая будет приостановлена очередным прерыванием от таймера. По этому прерыванию устройство 1.1 перехо5 дит на подпрограмму проверки работоспособности и запуска подчиненных устройств 1.2.....1.П. При этом поочередно читаются слова состояния каждого устройства 1.2,..,,1,п. Если в слове состояния блока 1,1 в

0 разряде Готовность записана 1, а в разряде Пуск - О, то управляющее устройство 1.1 переходит к анализу слова-состояния блока 1.1+1. Если же отсутствует 1 в разряде Готовность или имеется 1 в разряде

5 Пуск, то подчиненное устройство считается отказавшим и отключается командой отключить процессорный блок. После управляющее устройство 1.1 останавливает свой таймер и переходит к программе ини0 циализации системы. При этом осуществляется перераспределение задач для оставшихся процессорных блоков, загрузка данных и программ в эти блоки. Затем осуществляется их запуск, запускается таймер

5 управляющего устройства 1.1. после чего последний приступает к выполнению своей основной программы. Если при выполнении подпрограммы по прерыванию от таймера устройства 1.1 устройства отсутствуют, то

0 осуществляется поочередный запуск подчиненных устройств и возврат из подпрограммы.

Каждое подчиненное устройство 1.2,...,1.п работает следующим образом.

5 в начале каждого системного такта подчиненное устройство 1.1 ожидает запуска, т.е. анализирует разряд Пуск своего слова-состояния (установив единицу в разряд Готовность). При появлении единицы в разряде Пуск снимает Готовность и

Пуск, после чего оно запускает свой таймер и переходит на выполнение основной программы, после завершения которой устанавливает в единицу разряд Готовность слова-состояния.

Если управляющее устройство 1.1 выходит из строя, то оно заменяется работоспо- .собным, которое находится справа (см. фиг. Т) от блока 1.1 {не считая отключенные). Например, если отключенные устройства отсутствуют, то функции управляющего начинает выполнять устройство 1.2. Это осуществляется следующим образом.

Как показано выше, устройства 1.2,...,1 .п вначале каждого системного такта ожидают си гнал Пуск от управляющего устройства 1.1. При этом, если сигнал не поступает, например, в начале 3-го такта, подчиненное устройство, например 1.k, переходит на подпрограмму прерывания от своего таймера. При этом происходит выработка сигнала о неисправности управляющего устройства на выходе 23.k вычислительного блока 16.k (т.е. сбрасывается разряд Нет управляющего процессора слова состояния блока l.k), при этом уровень логического О поступает на тактирующий вход триггера 14;k и на вход 22.k блока 15.k. Одновременно, с этим анализируется разряд УПВ слова-состояния. При этом по отрицательному фронту переключается триггер 34.k, на выходе которого устанавливается уровень логической 1.

Так как на линии 10 присутствует уровень логического О, триггер 35.k переключается, на соответствующих входах элементов 38.k. 39.k, 44.k устанавливается уровень логической 1. После этого на линии 10 с выхода буфера 44.k формируется уро- вень логической 1, запрещающий переключение триггеров 35.k всех блоков 1.1 (i 1,п), и поступает далее на вход 30.1 устройства 1.1, так как триггер 35.1 не может быть установлен в единичное состояние, т.к. блок 1.1 - управляющий, то высокий уровень формируется на выходе элемента И 39.1 и с выхода31.1 блока 1.1 поступает на вход 30.2 блока 1.2.

Если этот блок не обнаружил пока неисправности управляющего устройства 1.1, т.е. триггер 35.2 блока 15.2 не установлен в единичное состояние, высокий уровень формируется с выхода 31.2 на входе 30.3 блока 1.3. Этот процесс будет продолжаться до первого устройства 1,k, которое обнаружило отказ управляющего устройства и, следовательно, триггеры 34,k и 35.k которого установлены в единичное состояние. В этом случае высокий уровень с входа 30,k. если на линии 9 нет уровня логической 1,

что необходимо для исключения одновременного срабатывания двух модулей 15.1, попадает на вход формирователя 41.k, после чего на выходе элемента 41.k формиру- ется импульс, который сбрасывает триггер 34,k и через буфер 43.k поступает на линию 9.

Так как все триггеры 33.i (i 1.n) после начальной установки находятся в нулевом

0 состоянии (на инверсном выходе - высокий уровень), то на входах 28.1 модулей 11.1 (I 2.п) установлен уровень логического О, который удерживает соответствующие триггеры 33.1 (I 2.п) в нулевом состоянии. На

5 выходе же 28.1 модуля 15.1 - высокий уровень, поскольку он соединен с входом 4 системы.

Таким образом, при возникновении первого импульса на линии 9 переключается

0 триггер 33.1. на выходе которого устанавливается уровень логической 1. Этим же импульсом сбрасываются все триггеры 35.1 (i TJT) на линиях 8 и 10, а также входах 30.1 (I О) модулей 15.1, по окончании импульса на

5 выходе формирователя 41.k и на линии 9 устанавливается уровень логического О. Если к этому моменту времени есть устройства, обнаружившие отказ управляющего блока, т.е.. установившие в единичное состо0 яние триггеры 34.1 соответствующих моделей 15.1, то формирование второго и последующих импульсов на линию 9 будет происходить аналогично первому. Таким образом на линии 9 будет столько импульсов,

5 сколько подчиненных устройств обн а ружи- ли отказ управляющего процессорного блока. В результате этого будут последовательно срабатывать триггеры 34.1 модулей 11.1.

0Момент отключения управляющего устройства определяется положением перемычки 45.1. т.е. если перемычка расположена в блоке 1 ,b (45.b). то после того как в подчиненных процессорных блоках

5 обнаружат отказ управляющего блока (на линии 9 сформируется b импульсов), срабатывает триггер 33.b и с его выхода через перемычку 45.b высокий уровень установится на выходе 25.Ь блока 1 .о, откуда попадает

0 на шину отключения управляющего процессора 5.

С входа 24,1 этот уровень логической 1 через формирователь 12.1 поступит на тактирующий вход блока 11.1. В результате на

5 выходе блока 11.1 установится уровень логической 1, при этом устройство 1.1 отключается и на вход 17.2 блока 1.2 поступает высокий уровень, устанавливающий в единицу разряд УПВ слова-состояния, устройство 1.2 начинает выполнять функции

управляющего. В остальных устройствах 1.3.....1.П разряды УП В останутся в нуле. Эти поочередно, анализируют разряды Пуск и УПВ своего слова-состояния и после установки разряда Пуск в единицу, т.е. после команды Пуск от управляющег-о устройства 1.2, будут выполнять функции подчиненных процессорных блоков. Кр оме того, при отключении устройства 1,1, как выполняющего функции управляющего, так и подчиненного,уровень /готической вы- хода блока 11.1 устанавливается на входе 2.1.1 и модуля 15.1; В результате этого сбрасываются в Ноль триггеры 34.J и 35.i и уйер- живаются этом ; состоянии, соответствующий модулю 15.1 не формирует импульс на линию.9, ,; ;i / ; ;V -,:;;;.;, /

Если в процессе дальнейшего функцио- нирования системы выйдетиз строя устройство 1,2, то оно будет заменен следующим за ним справа (не отключенный). Если в системе предусмотрены резервные устройства, то отказавшие могут быть заменены резервными, что не вызывает снижения производительности системы,: В случае, ко г-, да резервные устройства в системе отсутст- вуют, после очередного отказа осуществляется перераспределение задач между оставшимися устройствами, при этом система будет выполнять свои функ- ции, хотя и ciменьшей.производительностью. . - .- - ..;, . . - . .; Формула изобретения: Многопроцессорная вычислительная система, содержащая Н устройств обработ ки информации, М устройств ввода-вывода и запоминающее устройство, причем информационные входы-выходы всех устройств обработки через системную магистраль адреса данных.подключены к информационным входам-выходам запоминающего устройства и всех устройств ввода- вывода, выход признака ведущего а-го устройства обработки информации (где ,...Н-1) подключен к входу признака ве- : дущего (а-Н)-го устройства обработки информации, при этом каждое устройство обработки содержит вычислительный блок, первый блок отключения, триггер управления, злементИ и формирователь импульсов, причем в каждом устройстве обработки информации выход триггера управления соединен с первым управляющим входом вычислительного блока и первым управляю- щим входом первого блока отключения, вы- ход которого подключен к второму . -управляющему входу вычислительного блока и первому входу элемента И, второй вход которого подключен к входу признака ведущего устройства обработки информации, к

информационному входу триггера управления и третьему управляющему входу вычислительного бло«а, выход элемента И является, выходом признака ведущего устройства обработки информации первый информационный выход вычислительного блока подключен к входу синхронизации триггера управления, второй информационный выход вычислительного блока подключен к информационному входу первого блока отключения, второй управляющий вход которого .подключен к выходу формирователя импульсов, вход которого подключен к входу признака отключения устройства обработки информации, информационные входы-выходы устройства обработки .информации подключены к информационным входам-выходам вычислительного блока, от л и ч а ю ща я ся тем, что, с целью повышения надежности за счет сохранения работоспособности системы при кратных отказах и сокращения времени .отключения; управляющего устройства при разных длинах программ, выполняемых подчиненными устройствами обработки ин- ;формаций,; в многопроцессорной вычисли- тельной: системе выход признака неисправности и выход признака установки в исходное состояние устройства обработки .информации подключены соответственно к управляющему входу и входу начальной установки ()-го устройства обработки информации, вход начальной новки системы подключен к входу начальной установки первого устройства обработки информации, входы отключения и выходы признака отключения всех устройств обработки информации соединены между собой через системную магистраль отключения, первые, вторые и третьи управляющие входы в ыходы всех устройств обработки информации и первый управляющий вход первого устройства обработки информации соединены между собой через системную управляющую магистраль, вход единичного потенциала системы подключен к входам единичного потенциала всех устройств обработки информации, при этом в каждое .устройство обработки информации введен второй блок отключения, а в каждом устройстве обработки первый информационный выход вычислительного блока подключен к входу синхронизации второго блока отключения, вход признака ведущего устройства обработки подключен к первому управляющему входу второго блока отключения, первый, второй и третий выходы которого подключены соответственно к выходу признака неисправности устройства обработки информации, выходу признака

начальной установки устройства обработки информации, выход первого блока отключения подключен к второму управляющему входу второго блока отключения, управляющий вход и вход начальной установки уст- ройства обработки информации подключены соответственно к третьему и к четвертому управляющим входам второго блока отключения, первый, второй и третий управляющие входы-выходы которого явля- ются соответственно первым, вторым и третьим управляющими входами-выходами устройства обработки информации, вход единичного потенциала устройства обработки информации подключен к входу еди- ничного потенциала второго блока отключения, причем второй блок отключения процессора содержит три триггера, два элемента ИЛИ, два элемента И, два формирователя импульса и три буферных элемен- та, первый управляющий вход-выход блока отключения подключен к входу синхронизации первого триггера, первому входу первого элемента ИЛИ. первому входу первого элемента И и выходу первого буферного элемента, второй управляющий вход-выход блока отключения подключен к первому входу второго элемента ИЛИ, второму входу первого элемента ИЛИ, входу установки в О первого триггера и выходу второго бу- ферного элемента, третий управляющий вход-выход блока отключения подключен к входу синхронизации второго триггера и выходу третьего буферного элемента, первый управляющий вход блока отключения подключен к входу первого формирователя импульса, выход которого подключен к информационному входу второго буферного элемента, второй управляющий вход блока отключения подключен к второму входу второго элемента ИЛИ и третьему входу первого элемента ИЛИ, выход которого подключен к входу установки в 1 второго триггера, выход которого подключен к второму входу первого элемента И, информа- ционному входу третьего буферного элемента и первому входу второго элемента И, выход которого подключен к первому вы ходу блока отключения, третий управляющий вход которого подключен к второму входу второго элемента И и третьему входу первого элемента И, выход которого подключен к входу второго формирователя импульса, выход которого подключен к информационному входу первого буферного элемента и третьему входу второго элемента ИЛИ, выход которого подключен к входу установки в 0м третьего триггера, выход которого подключен к информационному входу второго триггера, вход синхронизации и вход единичного потенциала блока отключения подключены соответственно к входу синхронизации и информационному входу третьего триггера, выход первого триггера подключен к второму и третьему выходам блока отключения.

фиг.1

рцг. 2.

| Вычислительная структура | 1978 |

|

SU744589A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мультипроцессорная система | 1987 |

|

SU1524063A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

Авторы

Даты

1993-06-07—Публикация

1991-03-11—Подача