I315257

фоккера-Планка, Цель изобретения - .йовьшение быстродействия, Поставпен- мая цель достигается тем, что.уст- |)ойство содержит коммутатор 1 , труп- fty 2 иЭ N регистров, где N - размер аппроксимирующей сетки по пространг Ственной координате, блок 3 памяти, фервую группу 4 из N умножителей, jtepBbrii блок 5 быстрого преобразова- tO ия Фурье, вторую группу 6 из N умно154

жителей, торой блок 7 быстрого преобразования Фурье,.третью и четвертую группы 8 и 9 и N умножителей группу 10 из N сумматоров, блок 11 обратного преобразования Фурье, пятую группы 12 из N умножителей, группу 13 из N йакапливающих сумматоров, группу 14 из N элементов,И и блок 15 управления, 1 з,п, ф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Субоптимальный нелинейный фильтр | 1990 |

|

SU1714618A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1990 |

|

SU1734103A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Анализатор спектра Фурье | 1984 |

|

SU1226486A1 |

| Цифровой адаптивный фильтр | 1990 |

|

SU1837322A1 |

| Устройство корреляционной обработки широкополосных сигналов | 1989 |

|

SU1741274A2 |

| Процессор цифровой обработки сигналов | 1990 |

|

SU1789991A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1988 |

|

SU1640710A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

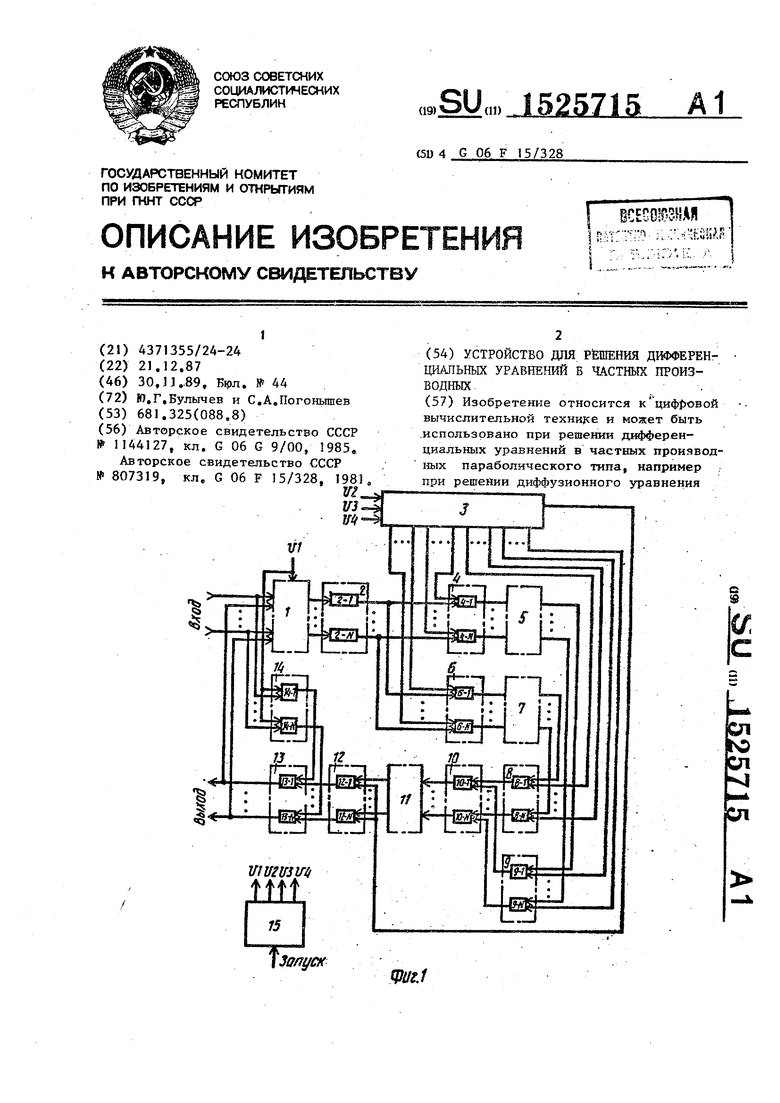

Изобретение относится к цифровой вычислительной технике и может быть использовано при решении дифференциальных уравнений в частных производных параболического типа, например при решении диффузионного уравнения Фоккера-Планка. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что устройство содержит коммутатор 1, группу 2 из N регистров, где N - размер аппроксимирующей сетки по пространственной координате, блок 3 памяти, первую группу 4 из N умножителей, первый блок 5 быстрого преобразования Фурье, вторую группу 6 из N умножителей, второй блок 7 быстрого преобразования Фурье, третью 8 и четвертую 9 группы из N умножителей, группу 10 из N сумматоров, блок 11 обратного преоразования Фурье, пятую группу 12 из N умножителей, группу 13 из N накапливающих сумматоров, группу 14 из N элементов И и блок 15 управления. 1 з.п. ф-лы, 2 ил.

Изобретение относится к цифровой ычислительной технике и может быть Использовано при решении дифференци- 4льных уравнений в частных производ- ых параболического типа например .иффузионного уравнения Фоккера-План- ;а,

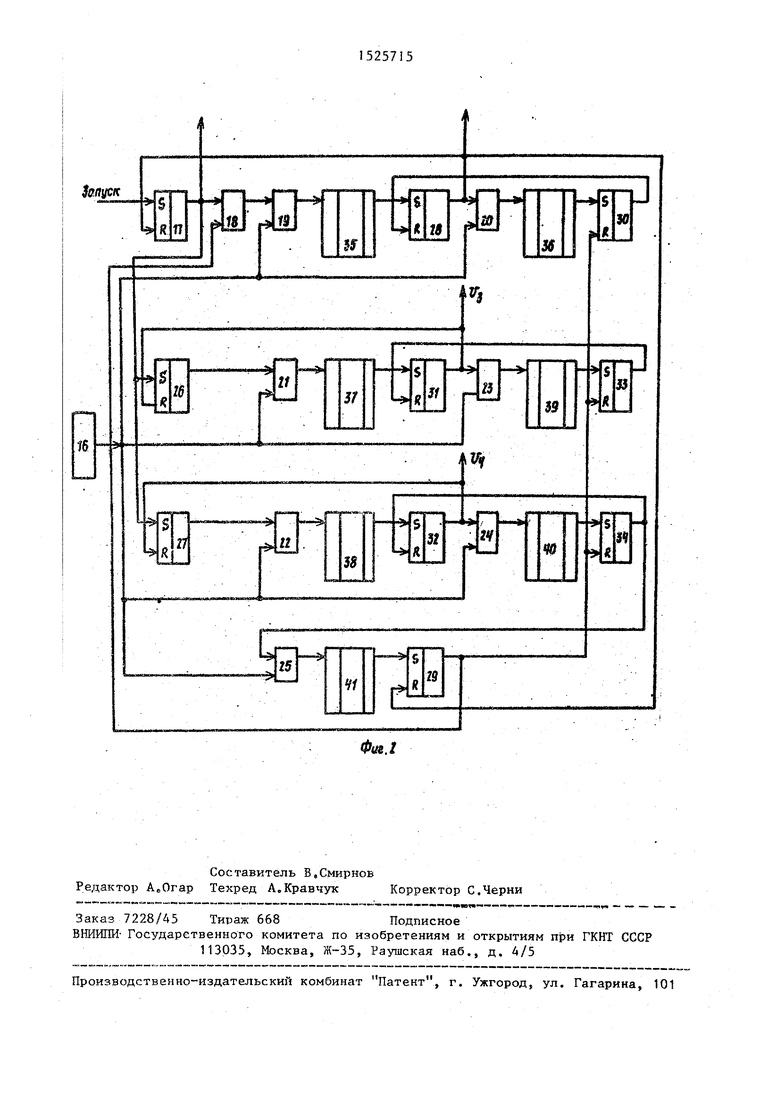

Цель изобретения - повьшение быстродействия за счет применения алгоритмов быстрого преобразования Фурье, На фиу, представлена схема уст- Ьойства , на фиг,2 - схема блока управления в

i Устройство содержит коммутатор i, группу 2 из N регистров (БР) где .. IN - размер аппроксимирующей сетки, |блок 3 памяти (БП), первую группу 4 |из N. умножителей (БУМ), первый блок ;5 быстрого П реобразования Фурье (БПФ)J вторзга) группу 6 из N умножи- :телей, второй БПФ 7 третью 8 k четвер тую 9 группы из N умножителей (БУМК) :,группу 10 из N сумматоров (БСК) , блок И обратного преобразования Фурье (ОБПФ)S пятую группу 12 из N умножителей, группу 13 из N накапливающих сумматоров (БСН), группу 14 из N элементов И и блок 15 управления

(БУ).

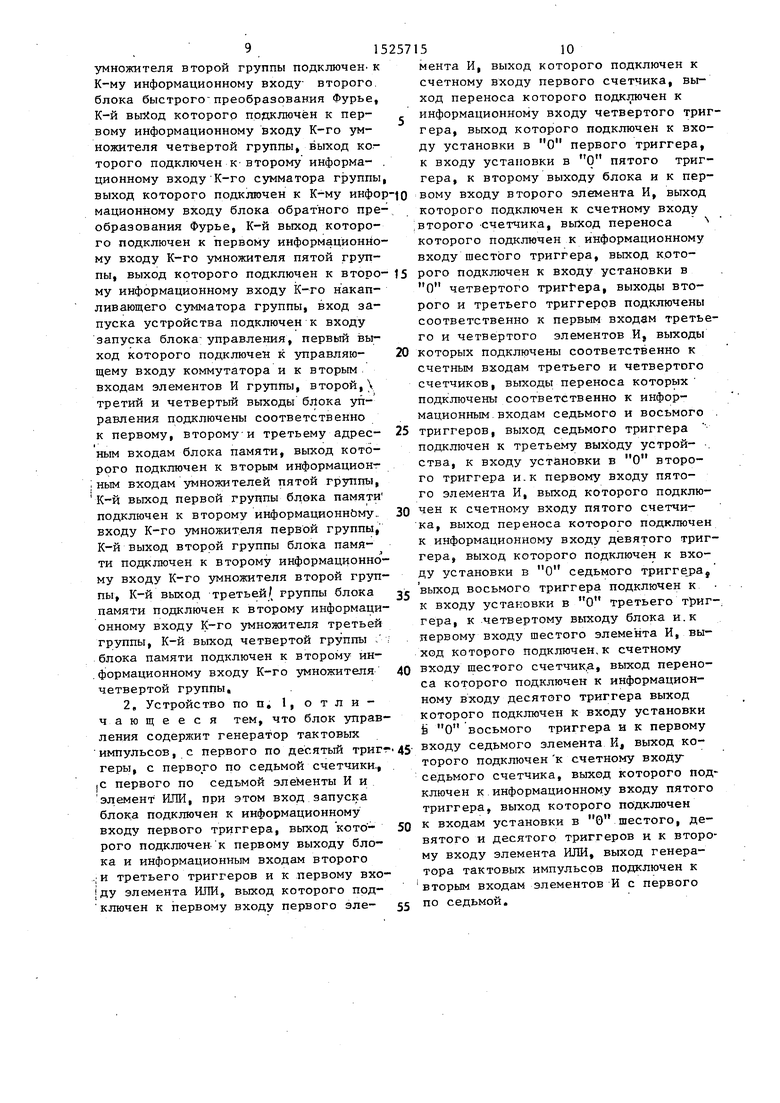

, содержит генератор 16 тактовых импульсов (ГТИ), первьй триггер J7, элемент ИЛИ 18, с первого, по седьмой элементы И 19-25, с второго по десятый триггеры 26-34 и с первого по седьмой счетчики 35-41

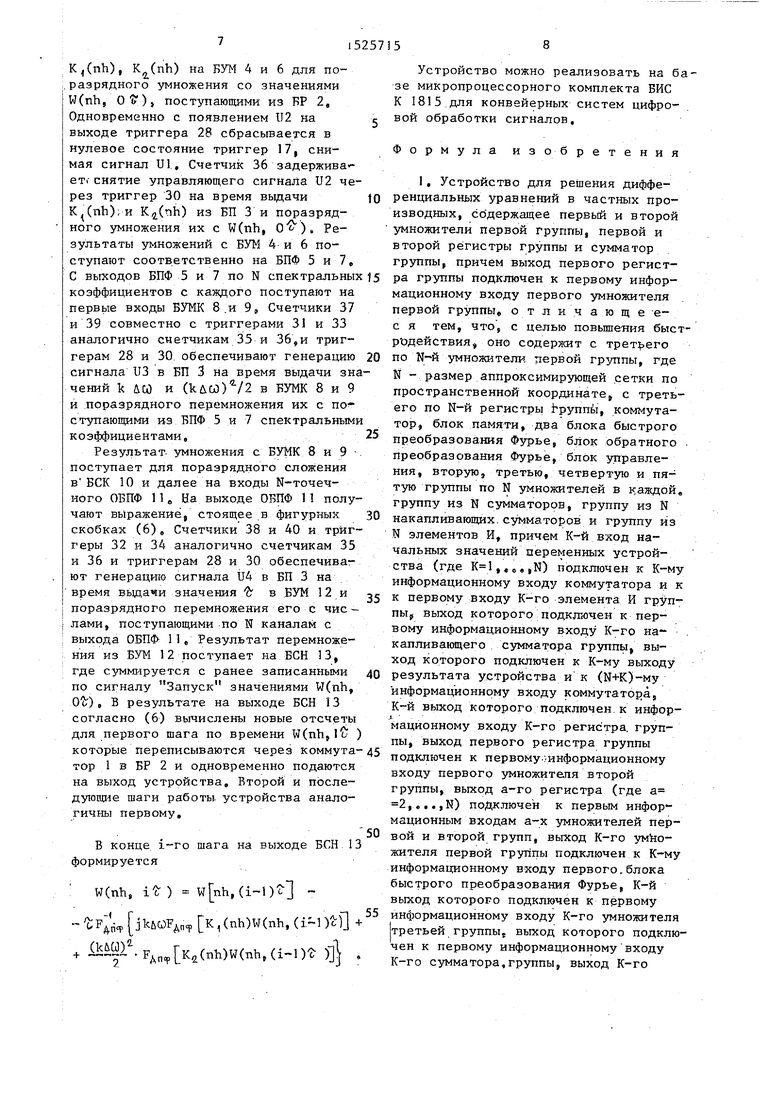

-.Уравнение Фоккера-Планка со стационарными коэффициентами сноса и диффузии имеет следующий вид:

Wj SAJll - i MHiSi.tXl 91Эх

1 B CKiCx) W() + 2

(1)

где W(x,t) - одномерная плотность вероятности скалярного марковского процесса (искомая Функция);

К(х) - стационарный коэффициент сноса|

Kg(x) - стационарный коэффициент диффузии.

Соответствующая разностная схема решения имеет вид

,(i+l)(xj i &) - OF ,(X) w(x,iu) ,,(x)W(K,i & )1 ()

/г

где i - номер узла сетки.по временной координате t, ,1{ - шаг сетки по временной координате;

F и F -соответственно операторы . прямого и обратного пре- . образования Фурье,

С помощью теоремы отсчетов Котель- никова и представления функции W(x,i ci ) в каждый фиксированный момент времени it- совокупностью N отсчетов по пространственной координате уравнение (2) может быть представлено в виде

, (i+l)(nh, i t ) - РдпФ jkbCOFA,,(nh)W(nh,it). л.

РД„Т, (kuW). F K/nli)W(nh.i &)

,l,...; ,N-l, ,N-l, (3)

где n - номер отсчета функции W(x,i b) по пространственной координате;

- шаг дискретизации УСх,) по пространственной координате;

- операторы прямого и обратного дискретного преобразования Фурье (ДПФ), которые для произв ольной функции u(nh) и ее спектрального аналога U(k utO) определяются парой взаимно обратных преобразований:

N-I

F.n(p|u(nh) u(nh)exp(

-н . А

-1

u(ku

СО

1 2 и 21U(UCO)exp( kn).

F

Ап

и F

получим (3) в

номер отсчета спектрального аналога функции СО (nh);

шаг дискретизации ее по пространственной частоте.

ьзуя свойство линейности one- 25

20

, (i+I)(nh, i ) - t jkbQF j,K, (nh,it)W(nhi it) + + K(nh)W(nh.i)lj/ (6)

Коммутатор 1 предназначен для отключения входов БР 2 от входов уст-- ройства после записи в БР 2 начальных отсчетов W(nh, О) и подключения их к входам БСН 13 по команде U1 из БУ 15, Каждый из регистров группы 2 предназначен для записи одного отсчета W(nh, it) на каждом временном шаге i c в последовательном двоичном коде, БП 3 обеспечивает хранение кон- .стант K,(Tih), K(nh), kuCO, . (kuQ)V22 и выдачз их по сигналам U2,. U3 и U4, БУМ 4 и БПФ 5 предназначены для пере множения отсчетов W(nh,i$ ), поступающих из БР 2, соответственно со

35

40

30

45

U4 - на время выдачи из БП 3 в. БУМ 12, -.

Устройство работает следующим образом,

В исходном состоянии, все триггеры и счетчики блоков находятся в нулевом состоянии, во всех разрядах всех регистров записаны нули, в БП 3 записаны константы K.(nh), ), kAU, (kuG))V2,.

По сигналу Запуск триггер 17 переводится в состояние 1 и генерирует управляющий сигнал U1, -при nor ступлении которого на зтрав ляющйй вход коммутатора его информационные входы соединяются с входом устройства, N отсчетов начальных значений W(nh, O S ) через -N входных каналов коммутатора 1 записьгоаются на N регистров 2, Одновременно N отсчетов начальных значений W(nh, 0) . по

значениями К(nh) и К2(nh), .поступаю- л каналам записываются в N-канальный щими из БП 3, БПФ 5 и БПФ 7, .служат БСН 13, Счетчик 35 задерживает снятие

U1 на время, необходимое для записи последовательных кодов чисел WCnhpOS) в регистры БР 2, Сигнал переполнения счетчика 35 переводит триггер 28 в состояние 1,,в результате Чего на его выходе формируется U2, При наличии данного сигнала на управляющем входе БП 3 вьщает значения

для вьтолнения операции ДПФ над полученными соответственно в БУМ 4 и БПФ 5 произведениями, БУМК 8 и 9 предназначены для перемножения результатов соответственно с БПФ 5 и 7 с по- поступающими из БП 3 значениями kdCO- . и (kutO), БСК 10 служит для суммирования полз енных на выходе БЗ МК.

10

25

35

40

15

20

30

45

и 9 комплексных чисел. ОБПФ 11 предназначен для выполнения обратного I ДПФ над полученным на выходе БСК 10 набором , N--T отсчетов комплексных чисел, БУМ 12 служит для з ножения полученного на выходе ОБПФ 11 результата на постоянную величину , поступающую из БП 3, БСН 13 предйа- значен для суммирования на каждом последующем шаге (i+1) значений искомой функции на предьщущем шаге i€ с поступающим из БУМ 12 результатом,Таким образом, на выходе БСН 13 формируется набор из N отсчетов искомой функции W(nh, (i+I) ) в. соответствии с (6), .БУ 15 предназначен, для выработки в соответствии с временной диаграммой управляющих сигналов:

U1 - на время записи начальных значений W(nh, ) в регист ры БР 2J

U2 - на время выдачи ) и K(nh). из БП 3 в БУМ 4 и 6;

из - на время вьздачи kA(0 и (kuta) из БП 3 в БУМК 8 и 9;

U4 - на время выдачи из БП 3 в. БУМ 12, -.

Устройство работает следующим образом,

В исходном состоянии, все триггеры и счетчики блоков находятся в нулевом состоянии, во всех разрядах всех регистров записаны нули, в БП 3 записаны константы K.(nh), ), kAU, (kuG))V2,.

По сигналу Запуск триггер 17 переводится в состояние 1 и генерирует управляющий сигнал U1, -при nor ступлении которого на зтрав ляющйй вход коммутатора его информационные входы соединяются с входом устройства, N отсчетов начальных значений W(nh, O S ) через -N входных каналов коммутатора 1 записьгоаются на N регистров 2, Одновременно N отсчетов начальных значений W(nh, 0) . по

55

КДпЬ), K,(nh) на БУМ 4 и 6 для по- разрядного умножения со значениями W(nh, О ), поступающими из БР 2, Одновременно с появлением U2 на с выходе триггера 28 сбрасывается в Нулевое состояние триггер 17, снимая сигнал U., Счетчик 36 задержива- етс- снятие управляющего сигнала U2 через триггер 30 на время выдачи fO K(nh); и K,2(nh) из БП 3 и поразрядного умножения их с W(nh, 0). Результаты утмножений с БУМ 4- и 6 поступают соответственно на БПФ 5 и 7, С выходов БПФ 5 и 7 по N спектральныхf5 коэффициентов с каждого поступают на первые входы БУИК 8.и 9, Счетчики 37 и 39 совместно с триггерами 31 и 33 аналогично счетчикам 35 и 36,и триггерам 28 и 30 обеспечивают генерацию 20 сигнала U3 в БП 3 на время выдачи значений k йСд) и (kuCO) в БУМК 8 и 9 и поразрядного перемножения их с по- ступающими из БПФ 5 и 7 спектральными коэффициентами,25

Результат- умножения с БУМК 8 и 9 -. поступает для поразрядного сложения в БСК 10 и далее на входы N-точеч- ного ОБПФ lie На выходе ОБПФ 1 получают выражение, стоящее ,в фигурных 30 скобках (6), Счетчики 38 и 40 и триггеры 32 и ЗА аналогично счетчикам 35 и 36 и триггерам 28 и 30 обеспечивают генерацию сигнала tJ4 в БП 3 на время выдачи значения /& в БУМ 12 и эс поразрядного перемножения его с чис - лами, поступающими по N каналам с выхода ОБПФ 11« Результат перемножения из БУМ 12 поступает на БСН 13, где с-З ммируется с ранее записанными 40 по сигналу Запуск значениями W(nh, ОЪ), В результате на выходе БСН 13 согласно (6) вычислены новые отсчеты для первого шага по времени W(nh, lll ) которые переписываются через коммута- 45 тор 1 в БР 2 и одновременно подаются на выход устройства. Второй и последующие шаги работы, устройства аналогичны первому,

50

Б конце, i-ro шага на выходе БСН. 13

формируется

W(nh, 1 ) ,() - С;РЛЙ Т л йОРдп K,(nh)W(nh, (i-l)cf + (nli)W(nh,(i-l) ) .

0 с 0 5

0

5

Устройство можно реализовать на базе микропроцессорного комплекта БИС К 1815 для конвейерных систем цифровой обработки сигналов.

Формула изобретения

1, Устройство для реЩения дифференциальных уравнений в частных производных, сО держащее первьй и второй умножители первой Группы, первой и второй регистры группы и сумматор группы, причем выход первого регистра группы подключен к первому информационному входу первого умножителя первой группы, отличающе -е- с я тем, 4TOj с целью повьшеяия быстродействия оно содержит с трет: его по М-й умножители цервой группы, где N - размер аппроксимирующей сетки по пространственной координате, с третьего по Ы-и регистры hpynn i, коммутатор, блок памяти, два блока быстрого преобразования Фурье, блок обратного . преобразования Фурье, блок управления, вторую, третью, четвертую и пятую группы по N умножителей в каждой, группу из N сумматоров, группу из N накапливающих.сумматоров и группу из N элементов И, пр1тчем К-й вход начальных значений переменных устройства (где ,«e,rN) подключен к К-му информационному входу коммутатора и к к первому входу К-го элемента И груп- пыу выход которого;подключен к первому информационному входу К-го накапливающего сумматора группы, выход которого подключен к К-му выходу результата устройства и к (N+K)-My информационному входу коммутатора, К-й выход которого подключен.к информационному входу К-го регистра, группы, выход первого регистра группы подключен к первому-жнформационному входу первого умножителя второй группы, выход а-го регистра (где а 2,.,.,N) подключен к первым информационным входам а-х умножителей первой и второй групп, выход К-го умйо- жителя первой группы подключен к К-му информационному входу первого.блока быстрого преобразования Фурье, К-й выход которого подключен к первому информационному входу К-го умножителя третьей группы5 выход которого подключен к первому информационному входу К-го сумматора,группы, выход К-го

умножителя второй группы подключен к К-му информационному входу второго, блока быстрого преобразования Фурье, К-й выйод которого подключён к первому информационному входу К-го умножителя четвертой группы, выход которого подключен к-второму информа- . ционному входу К-го сумматора группы.

выход которого подключен к К-му инфор- о вому входу второго элемента И, выход мационному входу блока обратного преобразования Фурье, К-й выход которого подключен к первому информационному входу К-го умножителя пятой группы, выход которого подключен к второ- 15 му информационному входу К-го накапливающего сумматора группы, вход запуска устройства подключен к входу запуска блока: управления, первый выход которого подключен к управляю- 20 щему входу коммутатора и к вторым входам элементов И группы, второй, третий и четвертый выходы блока управления подключены соответственно к первому, второму И третьему адрес- 25 ным входам блока памяти, выход которого подключен к вторым информационг

ным входам умножителей пятой группы,

К-й выход первой группы блока памяти подключен к второму информационнЬму.. 30 входу К-го з ножителя первой группы, К-й выход второй группы блока памяти подключен к второму информационному входу К-го умножителя второй группы, К-й выход третьей/ группы блока 35 памяти подключен к второму информационному входу К-го умножителя третьей группы, К-й выход четвертой группы ; блока памяти подключен к второму ин.формационному входу К-го умножителя 40 четвертой группы,

2, Устройство по ц, 1, отличающееся тем, что блок управления содержит генератор тактовых

которого подключен к счетному входу ;второго Счетчика, выход переноса которого подключен к информационному входу шестого триггера, выход которого подключен к входу установки в О четвертого триг1 ера, выходы второго и третьего триггеров подключены соответственно к первым входам третье го и четвертого элементов И, выходы которых подключены соответственно к счетным входам третьего и четвертого счетчиков, выходы переноса которых подключены соответственно к информационным входам седьмого и восьмого триггеров, выход седьмого триггера подключен к третьему выходу устрой- . ства, к входу уст&новки в О второго триггера и.к первому входу пятого элемента И, выход которого подключен к счетному входу пятого счетчика, выход переноса которого подключен к информационному входу девятого триггера, выход которого подключен к входу установки в О седьмого триггера, выход восьмого триггера подключен к к входу установки в О третьего триггера, к четвертому выходу блока и.к первому входу шестого элемента И, выход которого подключен,к счетному входу щестого счетчика, выход переноса которого подключен к информационному входу десятого триггера выход которого подключен к входу установки i О восьмого триггера и к первому

импульсов, с первого по десятый тригг. 45 °ДУ седьмого элемента К, выход которого подключен к счетному входу седьмого счетчика, выход которого под- ключен к информационному входу пятого триггера, выход которого подключен к входам установки в 0 шестого, девятого и десятого триггеров и к второму входу элемента ИЛИ, выход генератора тактовых импульсов подключен к вторым входам элементов И с первого по седьмой.

геры, с первого по седьмой счетчики., |С первого по седьмой элементы И и элемент ИЛИ, при этом вход запуска блока подключен к информационному входу первого триггера, выход кото- рого подключен- к первому выходу блока и информационным входам второго .; и третьего триггеров и к первому вхо jду элемента ИЛИ, выход которого прд- ключен к первому входу первого эле-

мента И, выход которого подключен к счетному входу первого счетчика, выход переноса которого подключен к информационному входу четвертого триггера, выход которого подключен к входу установки в О первого триггера, к входу установки в О пятого триггера, к второму выходу блока и к первому входу второго элемента И, выход

которого подключен к счетному входу ;второго Счетчика, выход переноса которого подключен к информационному входу шестого триггера, выход которого подключен к входу установки в О четвертого триг1 ера, выходы второго и третьего триггеров подключены соответственно к первым входам третьего и четвертого элементов И, выходы которых подключены соответственно к счетным входам третьего и четвертого счетчиков, выходы переноса которых подключены соответственно к информационным входам седьмого и восьмого триггеров, выход седьмого триггера подключен к третьему выходу устрой- . ства, к входу уст&новки в О второго триггера и.к первому входу пятого элемента И, выход которого подключен к счетному входу пятого счетчика, выход переноса которого подключен к информационному входу девятого триггера, выход которого подключен к входу установки в О седьмого триггера, выход восьмого триггера подключен к к входу установки в О третьего триг гера, к четвертому выходу блока и.к первому входу шестого элемента И, выход которого подключен,к счетному входу щестого счетчика, выход переноса которого подключен к информационному входу десятого триггера выход которого подключен к входу установки i О восьмого триггера и к первому

торого подключен к счетному входу седьмого счетчика, выход которого под- ключен к информационному входу пятого триггера, выход которого подключен к входам установки в 0 шестого, девятого и десятого триггеров и к второму входу элемента ИЛИ, выход генератора тактовых импульсов подключен к вторым входам элементов И с первого по седьмой.

| Оптическое вычислительное устройство | 1983 |

|

SU1144127A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1989-11-30—Публикация

1987-12-21—Подача