ТШ 1ШТ ИТПГ

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с селекторным каналом | 1986 |

|

SU1401472A1 |

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1451712A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для отладки микропроцессорной системы | 1987 |

|

SU1453408A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| РЕЗЕРВИРОВАННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2039372C1 |

| Устройство для синхронизации обмена микропроцессора с памятью отображения | 1989 |

|

SU1786489A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих систем управления различными объектами. Цель изобретения - повышение быстродействия за счет сокращения времени обращения к общей шине. Двухпроцессорная вычислительная система содержит вычислительные блоки 1 и 2, блок 3 регистров ввода, блок 4 общей памяти, блок 5 регистров вывода, блок 6 арбитражной коммутации, информационные входы 7 и выход 8, общие системные шины данных 9, адреса 10, управления 11, шины данных 12, 20, управления 13, 21, адреса 14, 22, выходы 15, 23 сопровождения адреса, выходы 16, 24 признака приема информации, выходы 17, 25 признака выдачи информации, выходы готовности 18, 26, входы сброса 19, 27. Повышение быстродействия достигается за счет совмещения во времени выборки команы одним вычислительным блоком и выполнения команды другим вычислительным блоком. 3 ил.

27

|памяти, блок 5 регистров вывода, блок 6 арбитражной коммутации, информацион- |Ные входы 7 и выход 8, общие систем- |ные шины данных 9, адреса 10, управ- ;ления 11, шины данных 12, 20, управ- |ления 13, 21, адреса 14, 22, выходы |15, 23 сопророждения адреса, выходы 16, 24 признака приема информации.

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих и надежных устройств управления различными объектами.

Цель изобретения - повышение производительности за счет сокращения времени обращения к общей шине.

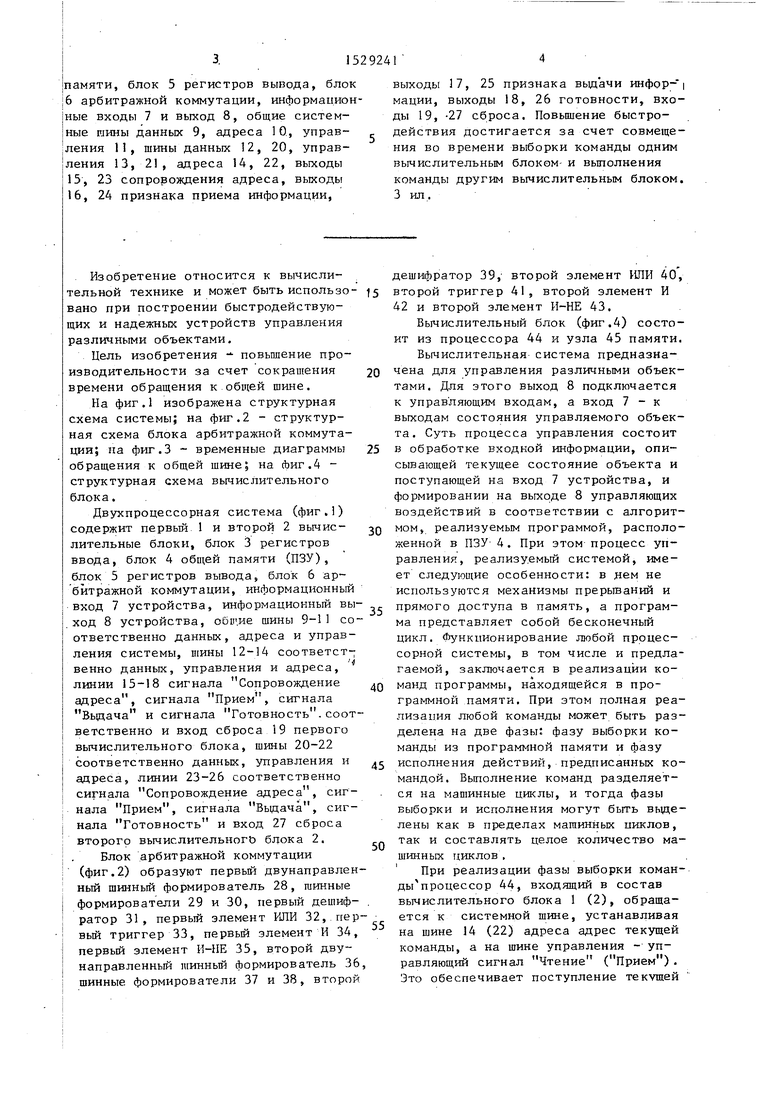

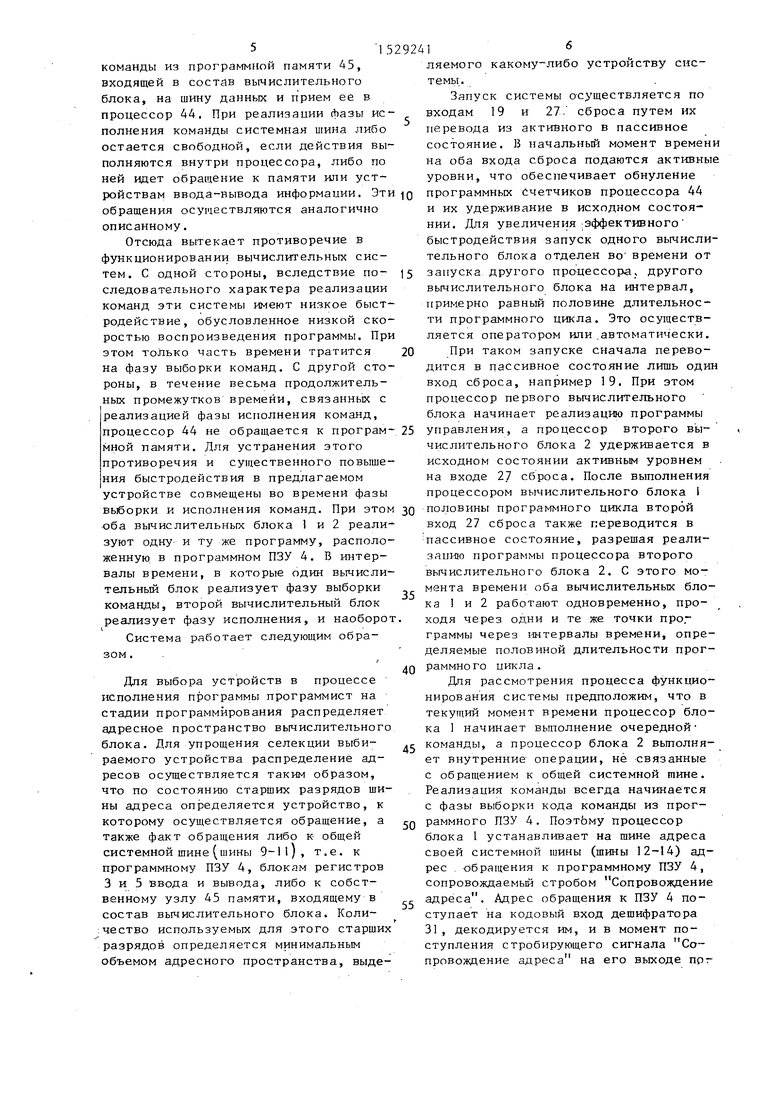

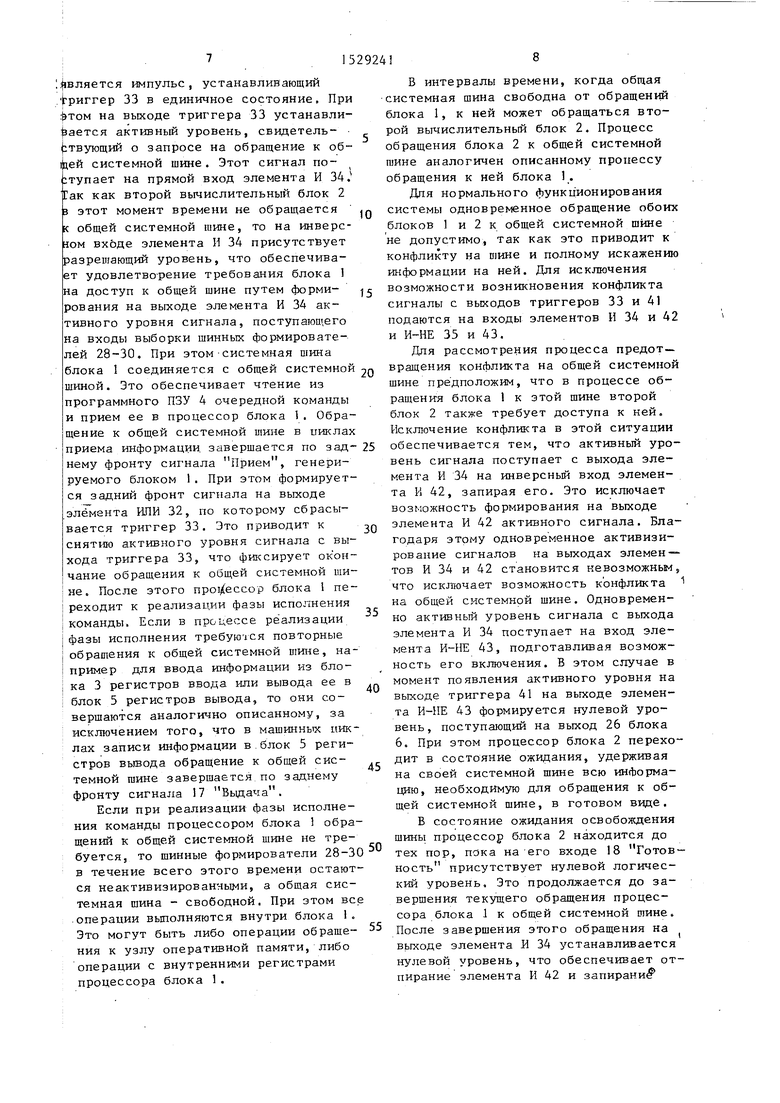

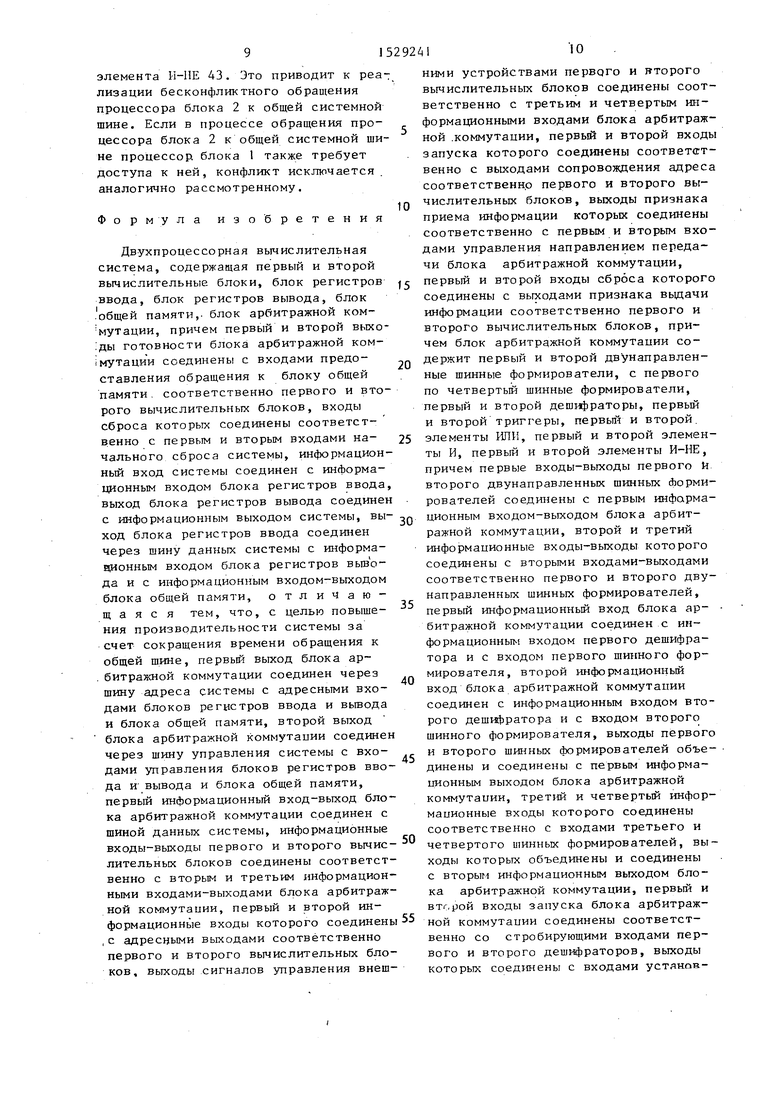

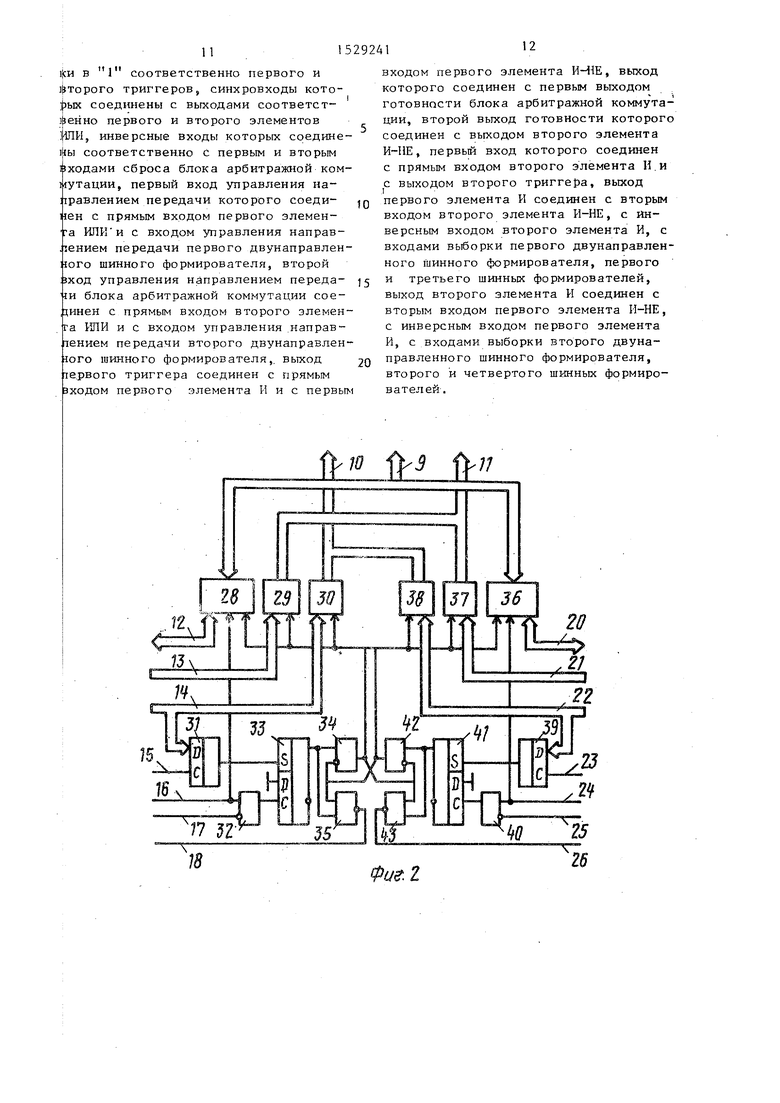

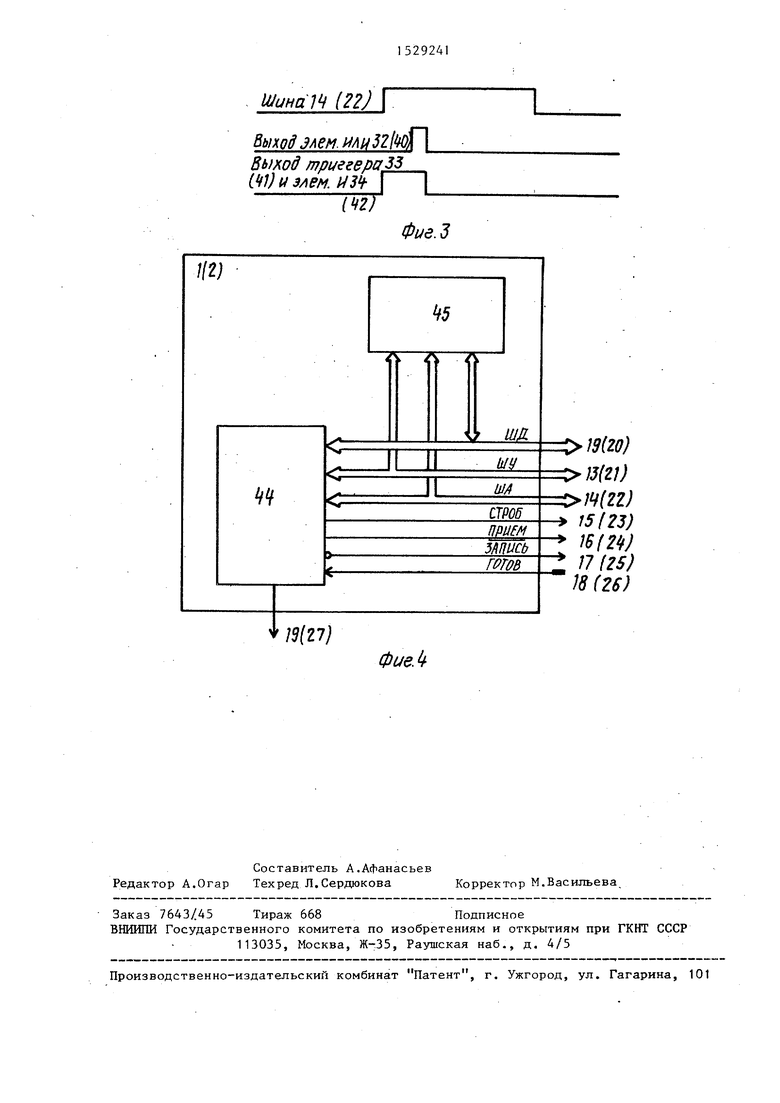

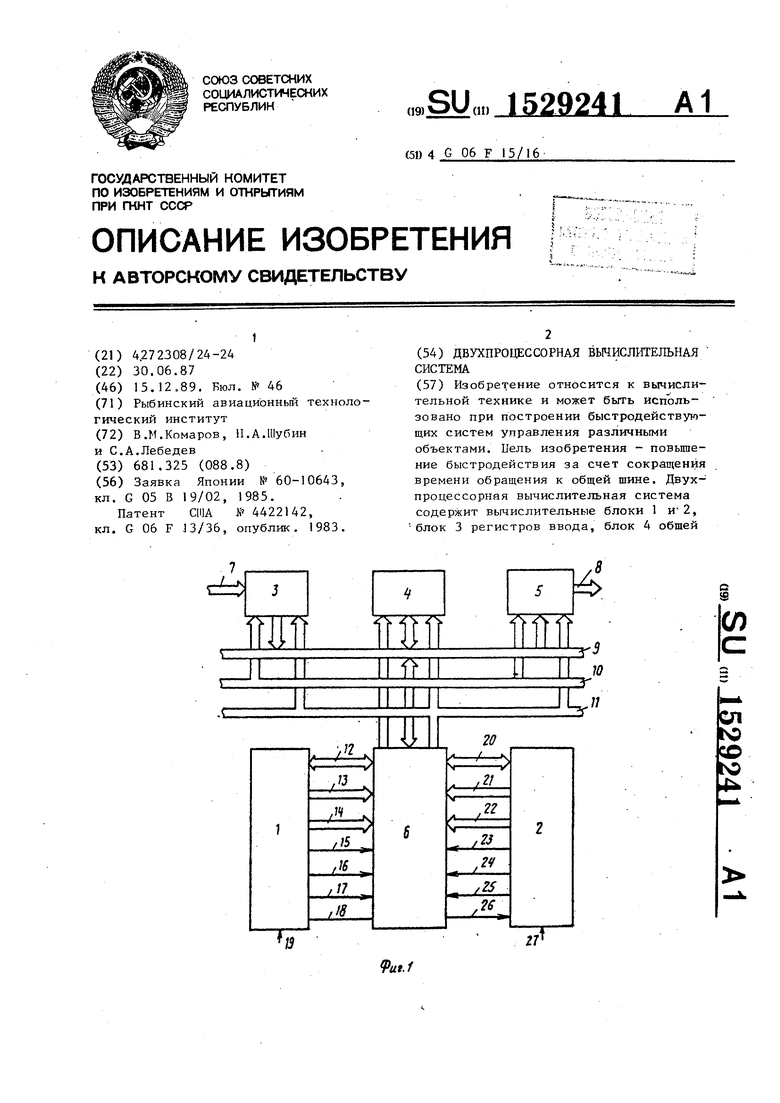

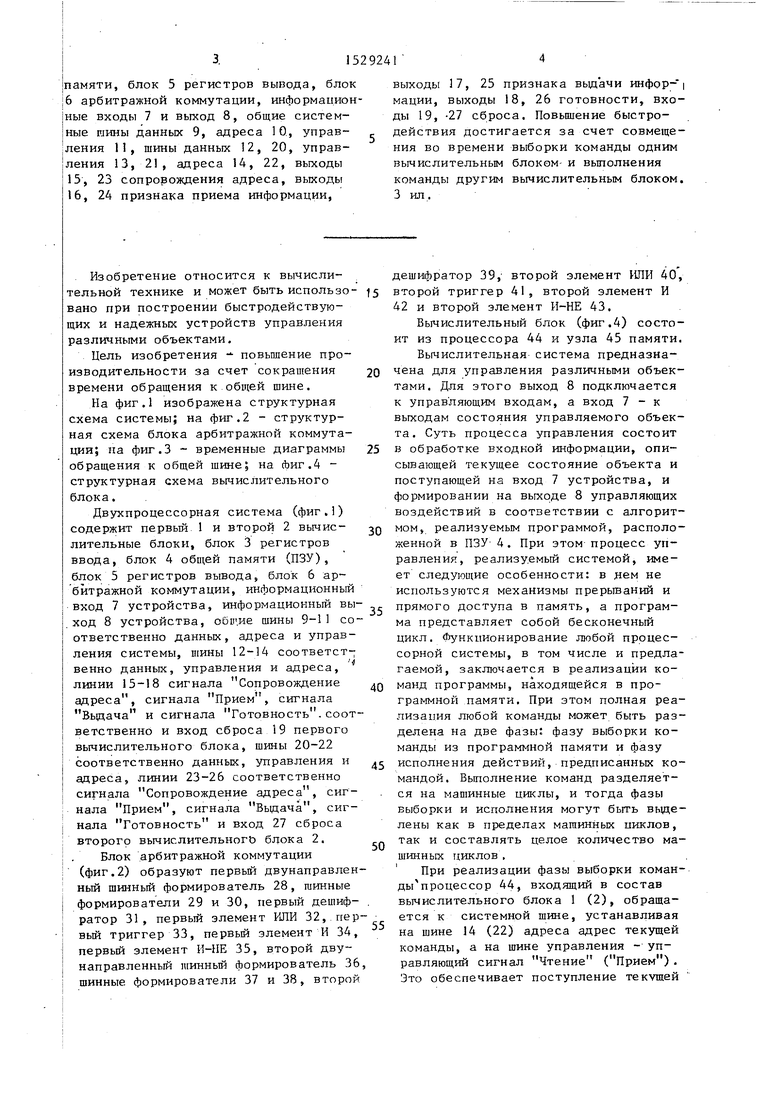

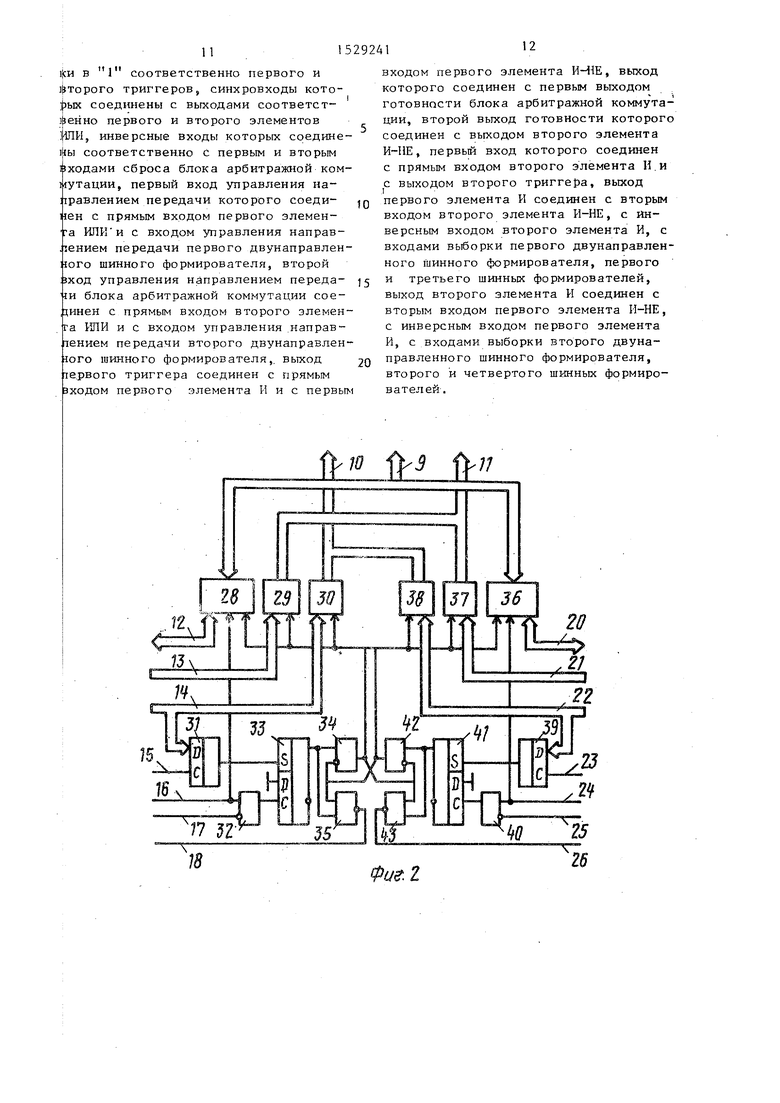

На фиг.1 изображена структурная схема системы; на фиг.2 - структурная схема блока арбитражной коммутации; па фиг.З - временные диаграммы обращения к общей щине; на фиг.4 - структурная схема вычислительного блока.

Двухпроцессорная система (фиг.1) содержит первьш 1 и второй 2 вычислительные блоки, блок 3 регистров ввода, блок 4 общей памяти (ПЗУ), блок 5 регистров вывода, блок 6 ар- битражной коммутации, информационный вход 7 устройства, информационньй выход 8 устройства, общие шины 9-11 соответственно данных, адреса и управления системы, шины 12-14 соответственно данных, управления и адреса, линии 15-18 сигнала Сопровождение адреса, сигнала Прием, сигнала Вьдача и сигнала Готовность.соответственно и вход сброса 19 первого вычислительного блока, шины 20-22 соответственно данных, управления и адреса, линии 23-26 соответственно сигнала Сопровождение адреса, сигнала Прием, сигнала Выдача, сигнала Готовность и вход 27 сброса второго вычислительного блока 2.

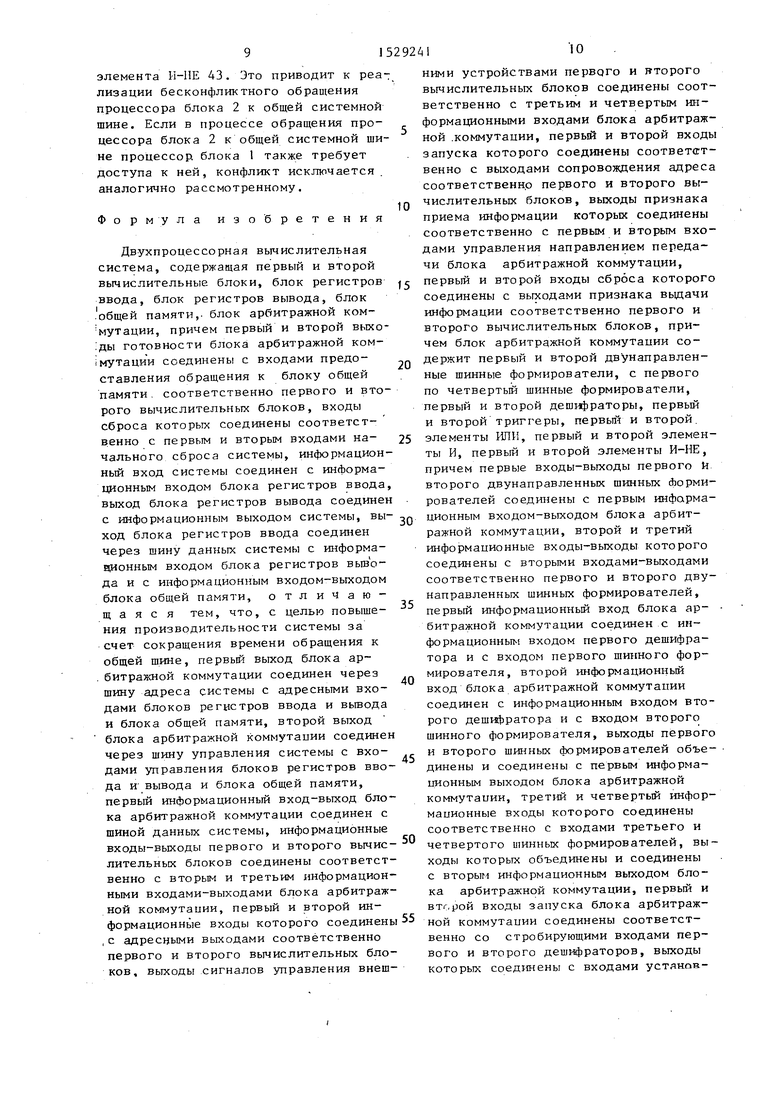

Блок арбитражной коммутации (фиг.2) образуют первый двунаправленный шинный формирователь 28, шинные формирователи 29 и 30, первый дешифратор 31, первый элемент КИИ 32, первый триггер 33, первый элемент И 34, первый элемент Н-ПЕ 35, второй двунаправленный тинный формирователь 36 шинные формирователи 37 и 38, второй

выходы 17, 25 признака вьщачи инфор- | мации, выходы 18, 26 готовности, входы 19, -27 сброса. Повьщгение быстродействия достигается за счет совмещения во времени выборки команды одним вычислительным блоком- и выполнения команды другим вычислительным блоком, 3 ил.

5

0

5

0

5

0

5

0

5

дешифратор 39, второй элемент ИЛИ 40, второй триггер 41, второй элемент И 42 и второй элемент И-НЕ 43.

Вычислительный блок (фиг.4) состоит из процессора 44 и узла 45 памяти.

Вычислительная система предназначена для управления различными объектами. Для этого выход 8 подключается к управляющим входам, а вход 7 - к выходам состояния управляемого объекта. Суть процесса управления состоит в обработке входной информации, описывающей текущее состояние объекта и поступающей на вход 7 устройства, и формировании на выходе 8 управляющих воздействий в соответствии с алгоритмом, реализуемым программой, расположенной в ПЗУ 4. При этом процесс управления, реализуемый системой, имеет следующие особенности: в дем не используются механизмы прерьгоаний и прямого доступа в память, а программа представляет собой бесконечный цикл, Функиионирование любой процессорной системы, в том числе и предлагаемой, заключается в реализации команд программы, находящейся в программной памяти. При этом полная реализация любой команды может быть разделена на две фазы: фазу выборки команды из программной памяти и фазу исполнения действий, предписанных командой. Выполнение команд разделяется на машинные циклы, и тогда фазы выборки и исполнения могут быть вьще- лены как в пределах машинных пиклов, так и составлять целое количество машинных циклов ,

При реализации фазы выборки коман- ды процессор 44, входящий в состав вычислительного блока 1 (2), обращается к системной шине, устанавливая на шине 14 (22) адреса адрес текущей команды, а на шине управления - управляющий сигнал Чтение (Прием). Это обеспечивает поступление текущей

команды из программной памяти 45, входящей в состйв вычислитепьного блока, на шину данных и прием ее в процессор 4А, При реализации фазы исполнения команды системная шина либо остается свободной, если действия выполняются внутри процессора, либо по ней идет обращение к памяти или устройствам ввода-вывода информапии. Эти Q программных Счетчиков процессора 44

обращения осуществляются аналогично описанному.

Отсюда вытекает противоречие в функционировании вычислительных систем. С одной стороны, вследствие по- следовательного характера реализации команд эти системы имеют низкое быстродействие, обусловленное низкой скоростью воспроизведения программы. При этом только часть времени тратится на фазу выборки команд. С другой стороны, в течение весьма продолжительных промежутков времени, связаннь1Х с реализацией фазы исполнения , процессор 44 не обращается к програм- мной памяти. Для устранения этого противоречия и существенг ого повышения быстродействия в предлагаемом устройстве совмещены во времени фазы

выборки и исполнения команд. При этом зо половины программного цикла второй оба вычислительных блока 1 и 2 реализуют одну- и ту же программу, расположенную в программном ПЗУ 4. В интервалы времени, в которые один вычислительный блок реализует фазу выборки команды, второй вычислительный блок

реализует фазу исполнения, и наоборот

I

Система работает следующим образом .

35

вход 27 сброса также переводится в пассивное состояние, разрешая реали запию программы процессора второго вычислительного блока 2. С этого мо мента времени оба вычислительных бл ка и 2 работают одновременно, про ходя через одни и те же точки прог граммы через интервалы времени, опр деляемые половиной длительности про раммно го цикла.

Для выбора устройств в процессе исполнения программы программист на стадии программирования распределяет адресное пространство вычислительного блока. Для упрощения селекции выбираемого устройства распределение адресов осуществляется таким образом, что по состоянию старших разрядов шины адреса определяется устройство, к которому осуществляется обращение, а также факт обращения либо к общей системной шине (щины 9-П), т.е. к программному ПЗУ 4, блокам регистров 3 и 5 ввода и вывода, либо к собственному узлу 45 памяти, входящему в состав вычислительного блока. Коли- ;чество используемых для этого старших разрядов определяется минимальным объемом адресного пространства, выделяемого какому-либо устройству системы.

Запуск системы о существляется по входам 19 и 27/ сброса путем их перевода из активного в пассивное состояние. В начальный момент времени на оба входа сброса подаются активные уровни, что обеспечивает обнуление

и их удерживание в исходном состоянии. Для увеличения :Эффективного быстродействия запуск одного вычислительного блока отделен во времени от запуска другого процессора другого вычислительного блока на интервал, примерно равный половине длительности программного цикла. Это осуществляется оператором или .автоматически. При таком запуске сначала переводится в пассивное состояние лишь одрт Вход сброса, например 19. При этом процессор первого вычислительного блока начинает реализацию программы управления, а процессор второго вычислительного блока 2 удерживается в исходном состоянии активным уровнем на входе 21 сброса. После выполнения процессором вычислительного блока I

о половины программного цикла второй

5

0

5

0

5

вход 27 сброса также переводится в пассивное состояние, разрешая реали- запию программы процессора второго вычислительного блока 2. С этого момента времени оба вычислительных блока и 2 работают одновременно, проходя через одни и те же точки прог граммы через интервалы времени, определяемые половиной длительности программно го цикла.

Для рассмотрения процесса функционирования системы предположим, что в текущий момент времени процессор блока 1 начинает выполнение очередной команды, а процессор блока 2 вьтолня- ет внутренние операции, не связанные с обращением к общей системной тине. Реализация команды всегда начинается с фазы выборки кода команды из программного ПЗУ 4. ПоэтЬму процессор блока 1 устанавливает на шине адреса своей системной шины (шины 12-14) адрес обращения к программному ПЗУ 4, сопровождаемый стробом Сопровождение адреса. Адрес обращения к ПЗУ 4 поступает на кодовый вход дешифратора 31, декодируется им, и в момент поступления стробирующего сигнала Сопровождение адреса на его выходе пот

;||вляется импульс , устанавливающий риггер 33 в единичное состояние. При на выходе триггера 33 устанавли- ается активный уровень, свидетель- |:твующий о запросе на обращение к об- цей системной шине. Этот сигнал по- ;тупает на прямой вход элемента И 34. ак как второй вычислительный блок 2 3 этот момент времени не обращается к общей системной шине, то на инверсном входе элемента И 34 присутствует разрешающий уровень, что обеспечивает удовлетворение требования блока 1 на доступ к общей шине путем формирования на выходе элемента И 34 активного уровня сигнала, поступающего на входы выборки шинных формирователей 28-30. При этом-системная шина блока I соединяется с общей системной шиной. Это обеспечивает чтение из программного ПЗУ 4 очередной команды и прием ее в процессор блока 1. Обращение к общей системной шине в ииклах приема информации, завершается по зад- нему фронту сигнала Прием, генерируемого блоком 1. При этом формируется задний фронт сигнала на выходе элемента ИЛИ 32, по которому сбрасывается триггер 33. Это приводит к снятию активного уровня сигнала с выхода триггера 33, что фиксирует ок он- чание обращения к общей системной шине. После этого npoi eccop блока 1 переходит к реализации фазь исполнения команды. Если в продессе реализации фазы исполнения требуются повторные обрашения к общей системной шине, например для ввода информации из блока 3 регистров ввода или вывода ее в блок 5 регистров вывода, то они совершаются аналогично описанному, за исключением того, что в машинньк циклах записи информации в блок 5 регистров вывода обращение к общей системной шине завершается по заднему фронту сигнала 17 Выдача.

Если при реализации фазы исполнения команды процессором блока 1 обращений к общей системной шине не требуется, то шинные формирователи 28-3 в течение всего этого времени остаются неактивизированчыми, а общая системная щина - свободной, При зтом вс .операции вьшолняются внутри блока 1. Это могут быть либо операции обращения к узлу оперативной памяти, либо операции с внутренними регистрами процессора блока 1.

0

5

0

5

0

5

0

5

5

В интервалы времени, когда общая системная шина свободна от обращений блока 1, к ней может обращаться второй вычислительный блок 2. Процесс обращения блока 2 к общей системной шине аналогичен описанному процессу обращения к ней блока 1.

Дпя Нормального функционирования системы одновременное обращение обоих блоков 1 и 2 к общей системной шине не допустимо, так как это приводит к конфликту на шине и полному искажению информации на ней. Для исключения возможности возникновения конфликта сигналы с выходов триггеров 33 и 41 подаются на входы элементов И 34 и 42 и И-НЕ 35 и 43.

Для рассмотрения процесса предотвращения конфликта на общей системной шине предположим, что в процессе обращения блока 1 к этой шине второй блок 2 также требует доступа к ней. Исключение конфликта в этой ситуации обеспечивается тем, что активный уровень сигнала поступает с выхода элемента И 34 на инверсный вход элемента И 42, запирая его. Это исключает возьюжность формирования на выходе элемента И 42 активного сигнала. Благодаря этому одновременное активизирование сигналов на выходах элемен- тов И 34 и 42 становится невсзможньм, что исключает возможность конфликта 1 на общей системной шине. Одновременно активный уровень сигнала с выхода элемента И 34 поступает на вход элемента И-НЕ 43, подготавливая возможность его включения. В этом случае в момент появления активного уровня на выходе триггера 41 на выходе элемента И-ПЕ 43 формируется нулевой уровень, поступающий на выход 26 блока 6. При этом процессор блока 2 переходит в состояние ожидания, удерживая на своей системной шине всю информацию, необходимую для обращения к общей системной шине, в готовом виде.

Б состояние ожидания освобождения щины процессор блока 2 находится до тех пор, пока на его входе 18 Готовность присутствует нулевой логический уровень. Это продолжается до завершения текущего обращения процессора блока 1 к общей системной тине. После завершения этого обращения на вьгкоде элемента И 34 устанавливается нулевой уровень, что обеспечивает отпирание элемента И 42 и запирани

915292А

элемента И-ПЕ 43. Это приводит к реализации бесконфликтного обращения процессора блока 2 к общей системной шине. Если в процессе обращения процессора блока 2 к общей системной шине процессор блока 1 также требует доступа к ней, конфликт исключается аналогично рассмотренному.

Формула изобретения

Двухпроцессорная вычислительная система, содержащая первый и второй вычислительные блоки, блок регистров ввода, блок регистров вывода, блок .общей памяти,, блок арбитражной ком- мутации, причем первый и второй вько- :ды готовности блока арбитражной ком- i fyтaци и соединены с входами предоставления обращения к блоку общей памяти, соответственно первого и второго вычислительных блоков, входы сброса которых соединены соответственно с первым и вторым входами начального сброса системы, информационный вход системы соединен с информационным входом блока регистров ввода, выход блока регистров вывода соединен

с информационным выходом системы, вы- Q ционным входом-выходом блока арбит35

40

ход блока регистров ввода соединен через шину данных системы с информа- Е(ионным входом блока регистров вьшо- да и с информационным входом-выходом блока общей памяти, отл ичаю- щ а я с я тем, что, с целью повышения производительности системы за счет сокращения времени обращения к общей шине, первый выход блока арбитражной коммутации соединен через шину адреса системы с адресными входами блоков регистров ввода и вьшода и блока общей памяти, второй выход блока арбитражной коммутации соединен через шину управления системы с входами управления блоков регистров ввода И вывода и блока общей памяти, первый информационньй вход-выход блока арбитражной коммутации соединен с шиной данных системы, информационные входы-выходы первого и второго вьгчис лительных блоков соединены соответственно с вторым и третьим информационными входами-выходами блока арбитражной коммутации, первый и второй информационные входы которого соединены 55 ,с адресными выходами соответственно первого и второго вычислительных блоков, выходы сигналов управления внеш45

, 50

ражнои коммутации, второй и третий информационные входы-выходы которого соединены с вторыми входами-выходами соответственно первого и второго дву направленных шинных формирователей, первый информационный вход блока арбитражной коммутации соединен с информационным входом первого дешифратора и с входом первого шинного формирователя, второй информационньй вход блока арбитражной коммутации соединен с информационным входом вто рого дешифратора и с входом второго шинного формирователя, выходы первог и второго шинных формирователей объе динены и соединены с первым информационным выходом блока арбитражной коммутации, третий и четвертьй инфор мационные входы которого соединены соответственно с входами третьего и четвертого шинных формирователей, вы ходы которых объединены и соединены с вторым информационным выходом блока арбитражной коммутации, первьй и втг.рой входы запуска блока арбитражной коммутации соединены соответственно со стробирующими входами первого и второго дешифраторов, выходы которых соединены с входами устянов 10

0

5

0

5

ними устройствами первого и второго вычислительных блоков соединены соответственно с третьим и четвертым информационными входами блока арбитражной .коммутации, первый и второй входы запуска которого соединены соответственно с выходами сопровождения адреса соответственн.о первого и второго вычислительных блоков, выходы признака приема информации которых соединены соответственно с первым и вторым входами управления направлением передачи блока арбитражной коммутации, первый и второй входы сброса которого соединены с выходами признака выдачи информации соответственно первого и второго вычислительных блоков, причем блок арбитражной коммутации содержит первый и второй двунаправленные шинные формирователи, с первого по четвертый шинные формирователи, первый и второй дешифраторы, первый и второй триггеры, первьй и второй, элементы ИЛИ, первый и второй элементы И, первый и второй элементы И-НЕ, причем первые входы-выходы первого И второго двунаправленных шинных Лорми- рователей соединены с первым инфарма35

40

5545

50

ражнои коммутации, второй и третий информационные входы-выходы которого соединены с вторыми входами-выходами соответственно первого и второго двунаправленных шинных формирователей, первый информационный вход блока ар битражной коммутации соединен с информационным входом первого дешифратора и с входом первого шинного формирователя, второй информационньй вход блока арбитражной коммутации соединен с информационным входом второго дешифратора и с входом второго шинного формирователя, выходы первого и второго шинных формирователей объединены и соединены с первым информационным выходом блока арбитражной коммутации, третий и четвертьй информационные входы которого соединены соответственно с входами третьего и четвертого шинных формирователей, выходы которых объединены и соединены с вторым информационным выходом блока арбитражной коммутации, первьй и втг.рой входы запуска блока арбитражной коммутации соединены соответственно со стробирующими входами первого и второго дешифраторов, выходы которых соединены с входами устянов

10

в 1 соответственно первого и iHoporo триггеров, синхровходы кото- рых соедннены с вьгходами соответст- -фенно первого и второго элементов ШИ, инверсные входы которых соединены соответственно с первым и вторым входами сброса блока арбитражной коммутации, первый вход управления на- :1равлением передачи которого соединен с прямым входом первого элемента ИЛИ и с входом управления направ- зением передачи первого двунаправлен- юго шинного формирователя, второй :зход управления направлением переда- и блока арбитражной коммутации соединен с прямым входом второго элемента ШИ и с входом управления .направ- 1ением передачи второго двунаправленного шинного формирователя,, выход20 первого триггера соединен с прямым зходом первого элемента И и с первым

152924112

входом первого элемента H4iE, выход которого соединен с первым выходом готовности блока арбитражной коммутации, второй выход готовности которого соединен с выходом второго элемента И-НЕ, первьй вход которого соединен с прямым входом второго элемента Н.и

15

с выходом второго триггера, выход первого элемента И соединен с вторым входом второго элемента И-НЕ, с инверсным входом второго элемента И, с входами выборки первого двунаправленного шинного формирователя, первого и третьего шинных формирователей, выход второго элемента И соединен с вторым входом первого элемента И-НЕ, с инверсным входом первого элемента И, с входами выборки второго двунаправленного шинного формирователя, второго и четвертого шинных формирователей.

с выходом второго триггера, выход первого элемента И соединен с вторым входом второго элемента И-НЕ, с инверсным входом второго элемента И, с входами выборки первого двунаправленного шинного формирователя, первого и третьего шинных формирователей, выход второго элемента И соединен с вторым входом первого элемента И-НЕ, с инверсным входом первого элемента И, с входами выборки второго двунаправленного шинного формирователя, второго и четвертого шинных формирователей.

2

26

Шина (22) Выход элем, ли

Вымд шриегерд-ЗЗ

W) и элем. //J j

Ц

С С

(П

Фие.З

lO- W

да/;

(гг} - /5/ад - /5/W

11125) 18 (26)

Фие.

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Патент США № 4422142, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1989-12-15—Публикация

1987-06-30—Подача