if.Ll 1-„J

(Л

пятеля 11 и группы элементов И 10, введен элемент ИЛИ 2, а каждый блок намятн содержит элемент И 13 и узел сравнения 12. Устройст зо функционирует совместно с блоком основной па- м|яти 20 и блоком записи 17. Дефект- нЬе слово из ОС11ОВНОГО блока памяти

20 может быть заменено на слово, которое записывается в один из k блоков памяти подмены. При считывании из блока памяти подмены считывается само слово, а не код адреса, по которому хранится резервное слово. 1 ил. , 1 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подмены информации в постоянной памяти | 1988 |

|

SU1536443A1 |

| Устройство для подмены информации в постоянной памяти | 1989 |

|

SU1645998A1 |

| Многоканальное оперативное запоминающее устройство | 1987 |

|

SU1432606A1 |

| Устройство для параллельной передачи информации | 1990 |

|

SU1795465A1 |

| Устройство для связи процессоров | 1986 |

|

SU1481785A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Устройство для обработки структур данных | 1990 |

|

SU1698891A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

Изобретение относится к вычислительной технике и может быть использовано для коррекции программ или исправления ошибок в постоянной памяти. Целью изобретения является упрощение п повышение быстродействия устройства. Для достижения цели в устройство, содержащее K блоков памяти подмены 1, состоящих из накопителя 11 и группы элементов И 10, введен элемент ИЛИ 2, а каждый блок памяти содержит элемент И 13 и узел сравнения 12. Устройство функционирует совместно с блоком памяти 20 и блоком записи 17. Дефектное слово из основного блока памяти 20 может быть заменено на слово, которое записывается в один из K блоков памяти подмены. При считывании из блока памяти подмены считывается само слово, а не код адреса, по которому хранится резервное слово. 1 ил., 1 табл.

Изобретение относится к вычислительной технике и может быть использовано для коррекции программы или и справления ошибок в постоянной па- м);ти.

Целью изобретения является упро- щйние и повьшение быстродействия устройства.

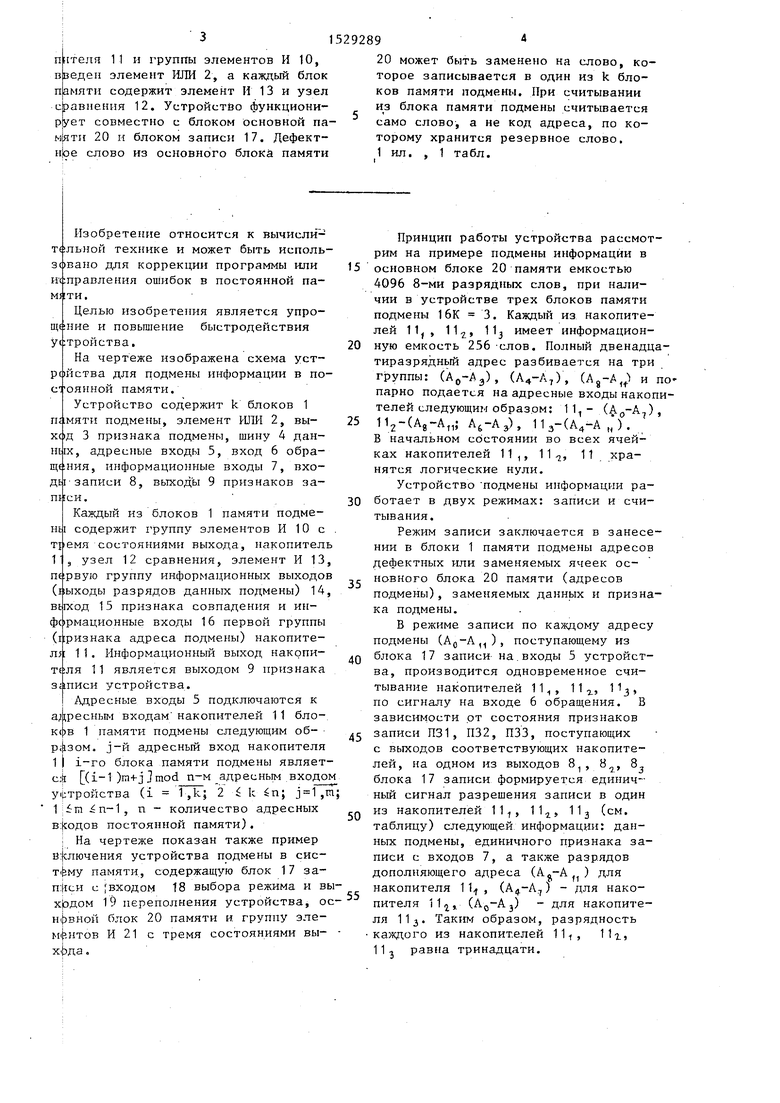

На чертеже изображена схема уст- Р(

пг хс

|йства для подмены информации в по оянной памяти.

Устройство содержит k блоков 1 .мяти подмены, элемент ИЛИ 2, вы- |Д 3 признака подмены, шину 4 данних, адресные входы 5, вход 6 обра- щ«:ния, информационные входы 7, вхо- ДЕ1-записи 8. выходы 9 признаков заП1

Каждый из блоков 1 памяти подме- Htji содержит 1 руппу элементов И 10 с

30

емя состояниями выхода, накопитель

э узел 12 сравнения, элемент И 13,

рвую группу информационных выходов

1ЫХОДЫ разрядов данных подмены) 14,

TI Г пе d

вьгход 15 признака совпадения и ин- фсфмационные входы 16 первой группы (1:ризнака адреса подмены) накопителе: 11. Информационный выход накопи- 11 является выходом 9 признака записи устройства.

Адресные входы 5 подключаются к адресным входам накопителей 11 бло-, ков 1 памяти подмены следующим об- , j-й адресный вход накопителя 1i i-ro блока памяти подмены являет- ci (i-T ) n-м адресным входом у|1;тройства (i 1 ,k; 2 k en; j 1 ,m n-1, n - количество адресных в:}содов постоянной памяти).

; На чертеже показ-ан также пример 8:| ;лючения устройства подмены в сис- т4му памяти., содержащую блок 17 за- с входом 18 выбора режима и вы хЬдом 19 нереполнения устройства, ос н|)вной блок 20 памяти и группу эле- Mii-HTOB И 21 с тремя состояниями вы- хЬда,

5

0

5

0

5

0

5

0

5

Принцип работы устройства рассмотрим на примере подмены информации в основном блоке 20 памяти емкостью 4096 8-ми разрядных слов, при наличии в устройстве трех блоков памяти подмены 16К 3. Каждый из накопителей 11у, ll Ь мвет информационную емкость 256 -слов. Полный двенадца- тиразряднь1й адрес разбивается на три группы: (АО-АЗ), (А4-А7), (, и по- парно подается на адресные входы накопителей следующим образом: 1 1 - (,),

ii2-(Ag-A,,; ), ПЗ-СА -А,.).

В начальном состоянии во всех ячейках накопителей 11,, 11-2, 11. ра- нятся логические нули.

Устройство подмены информации работает в двух режимах: записи и считывания.

Режим записи заключается в занесении в блоки 1 памяти подмены адресов дефектных или заменяемых ячеек основного блока 20 памяти (адресов подмены), заменяемых данных и признака подмены.

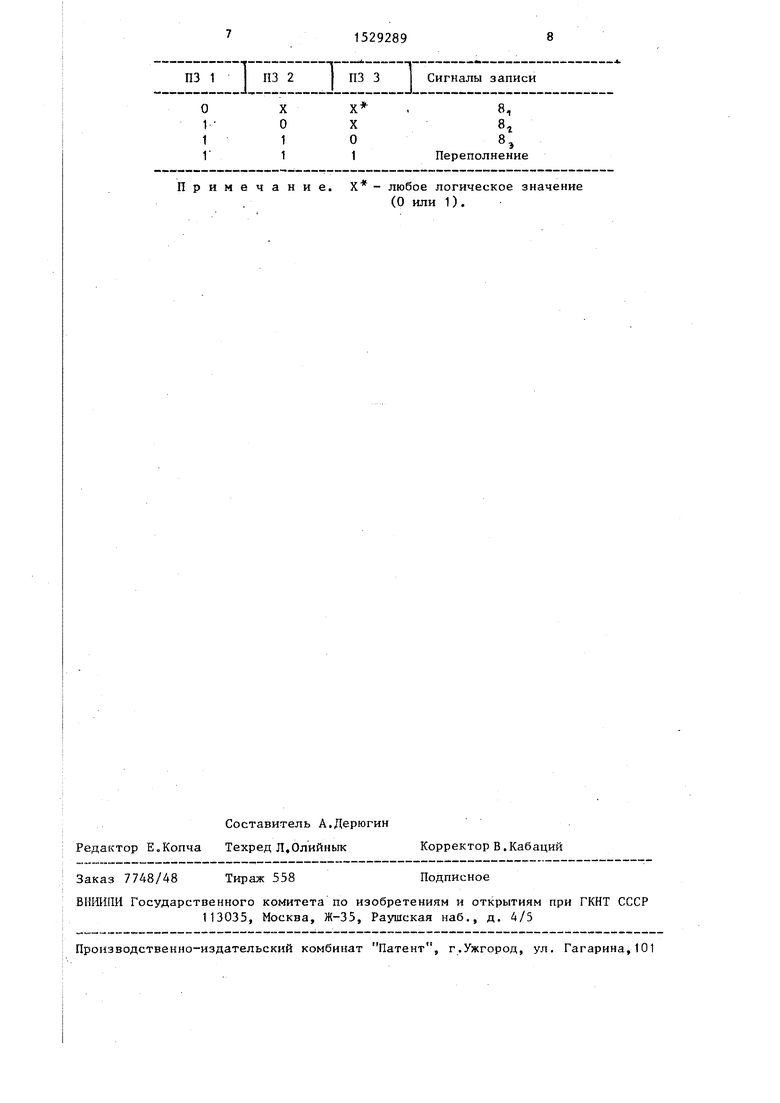

В режиме записи по каждому адресу подмены (Ag-A,), поступающему из блока 17 записи на.входы 5 устройства, производится одновременное считывание накопителей 11, 11х з по сигналу на входе 6 обращения. В зависимости от состояния признаков записи П31, П32, ПЗЗ, поступающих с выходов соответствующих накопителей, на одном из выходов 8,, 8, 8, блока 17 записи формируется единичный сигнал разрешения записи в один из накопителей 11, 11 г 11з (см. таблицу) следующей, информации: данных подмены, единичного признака записи с входов 7, а также разрядов дополняющего адреса () для накопителя 1 1 , (.) - для накопителя 112,, (AQ-AJ) - для накопителя 11з Таким образом, разрядность каждого из накопителей 11, 11г, 11J равна тринадцати.

Запись адресов в устройстве може продолжаться до тех пор, пока при записи очередного адреса все признаки записи не окажутся равными единице. В этом случае на выходе блока 17 записи формируется признак (на выходе 19) переполнения устройства.

И режиме считывания блок 17 записи по сигналу на входе 18 отключае- ся от адресных входов 5 и входа 6 обращения, на входах 8 устройства выставляются сигналы логического нуля.

При обращении к основному блоку 20 памяти по сигнапу обращения на входе 6. происходит одновременное считывание из накопителей 11, 11j , причем в узлах 12, 12, , сравнения осуществляется сравнение дополняющего адреса, считанного из накопителей 11, 11, Ц с соответствующими разрядами адреса на входах 5. Результаты сравнения поступают далее на элементы И 13,, 13, 13 и, если имели место сравнения адреса и единичный признак записи в одном из блоков 1 памяти подмены, то на выходе элемента И 13 блока памяти формируется единичный признак совпадения, по которому элементом ШШ

2вырабатывается общий признак подмены. Логическая единица на выходе

3переводит выходы элементов И группы 21 в третье состояние, блокируя выдачу информадии из блока 20 основной памяти на шину 4 данных. Одновременно .одна- из групп элементов И 10, 10, 103 по сигналу с выхода соответствующего элемента И 13,, 13,.,, 13 разрешает передачу данных подмены от соответствующего накопителя 11,, 11,, на шину 4 данных В случае отсутствия единичного признака подмены на выходе 3 информация на шину 4 данных передается из блока 20 основной- памяти, а выходы групп элементов И Ю,, 10, 10 находятся в третьем состоянии.

По сравнению с устройством-прототипом предлагаемой устройство при одиноковом количестве адресов подмены позволяет для рассмотренного примера почти в 8 раз сократить аппаратурные затраты на реализацию, причем данные подмены выбираются за один дикл обращения к блокам памяти.

Формула изобретения

Устройство для подмены и-кЬорма- ции в постоянной памяти, содержащее k блоков памяти подмены, каждый из

Q которых состоит из накопителя и

группы элементов И с тремя состояниями выхода, вьгход.1 которых являются информационными выходами устройства, отличающееся тем, что, с

5 целью упрощения и повьппения быстро- действия устройства, в него введен элемент ИПЛ, а каждый блок памяти подмены содержит узел сравнения и элемент И, причем j-й адресный вход

0 накопителя i-ro блока памяти подмены является (i-1)m4-jj mod п-м адрес- ным входом устройства, i 1, k, , , j 1,m, , n - колическтво адресных входов по5 стоянкой памяти, а информационные входы первой группы накопителя i-ro блока памяти подмены являются остальными адресными входами устройства и соединены с входами первой группы

0 узла сравнения, входы второй группы которого подключены к информационным выходам первой группы нак.опите5

0

5

0

элемента И, выход которого соединен с первыми входами группы элементов И с тремя состояниями выхода, вторые входы которых соединены с соответствующими информационными выходами второй группы накопителя, информационный выход которого подключен к второму входу элемента И и является i-м выходом признака записи устройства, выход элемента И каждого блока памяти подмены соединен с соответствующим входом элемента 11ПН, выход которого является выходом -признака подмены устройства, вход обращения и информационные входы второй группы каждого накопителя являются соответственно входом обращения и информационными входами устройства, вход записи накопителя i-ro блока памят и подмены является i-м входом записи устройства.

Примечание. любое логическое значение

(О или 1).

| УСТРОЙСТВО ДЛЯ СОЗДАНИЯ КОЛЕБАНИЙ БАРАБАННОЙ ПЕРЕПОНКИ УХА | 2006 |

|

RU2328262C2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| ТЕРМОКОНТРАСТНЫЙ ДУШ-1 | 2006 |

|

RU2328263C2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1989-12-15—Публикация

1988-04-01—Подача