Изобретение относится к радиотехнике и может быть использовано в фазовращателях, корректорах временного положения импульсов синтезато- - ров сигналов и измерительных комплексах.

Цель изобретения - повышение быстродействия при управлении задержкой входных импульсов на частоте их следования путем введения в состав устройства формирователя импульсов, N дополнительных элементов задержки, (N-.1) дополнительных регистров и новых сбязей каждый коммутатор управляется с выхода соответствующего дополнительного регистра, который

тактируется сигналом с выхода пре- дьщущего коммутатора.

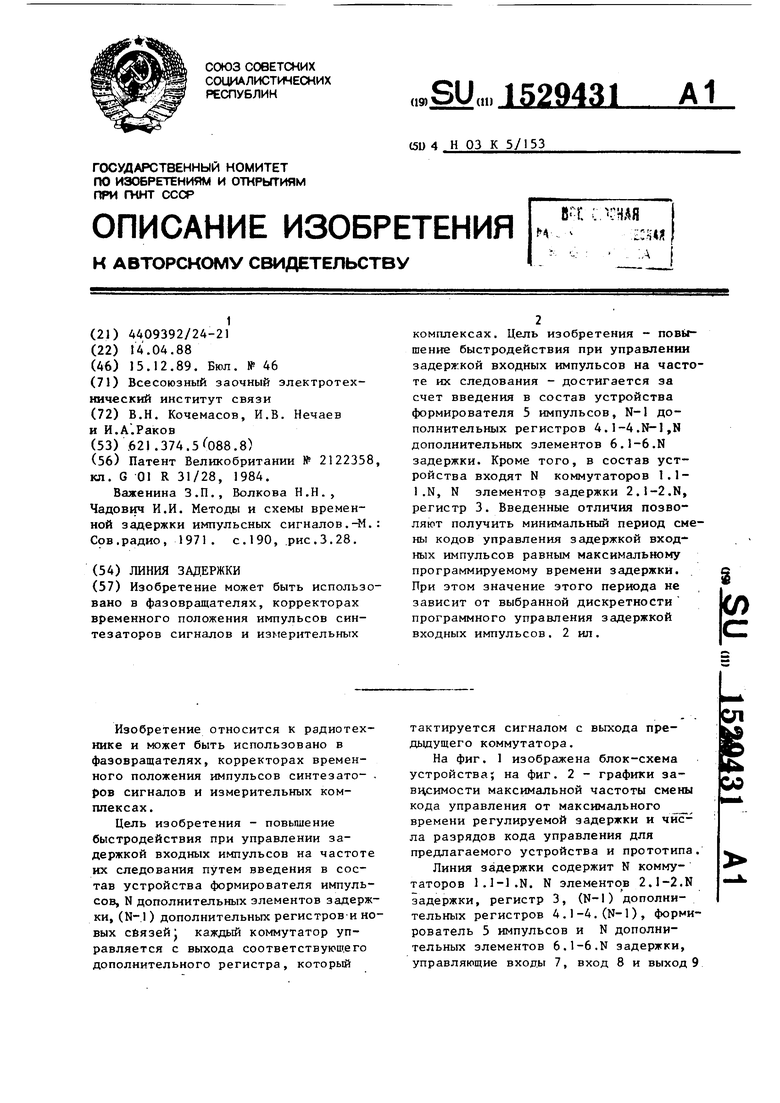

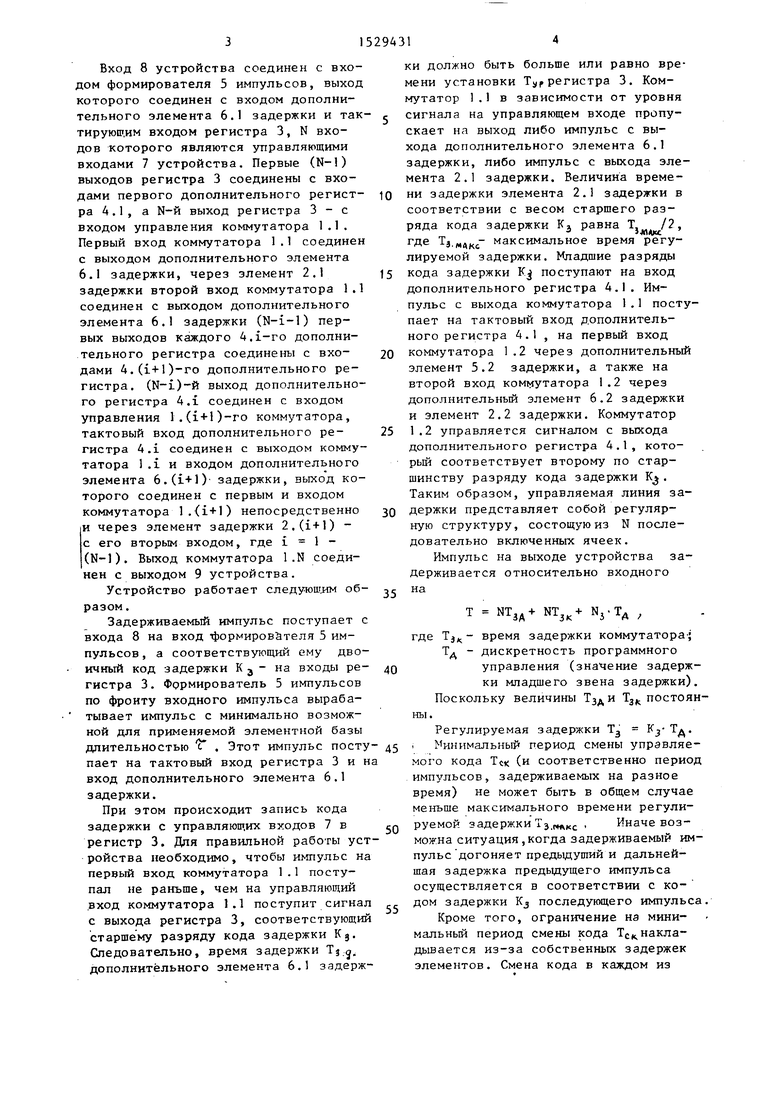

На фиг. I изображена блок-схема устройства; на фиг. 2 - графики зависимости максимальной частоты смены

кода управления от максимального

времени регулируемой задержки и числа разрядов кода управления для предлагаемого устройства и прототипа.

Линия задержки содержит N коммутаторов 1.1-1.N. N элементо в 2.1-2.N задержки, регистр 3, (N-I) дополнительных регистров 4.1-4.(N-1), формирователь 5 импульсов и N дополнительных элементов 6.1-6.N задержки, управляющие входы 7, вход 8 и выход 9

Вход 8 устройства соединен с входом формирователя 5 импульсов, выход которого соединен с входом дополнительного элемента 6.1 задержки и так тирующим входом регистра 3, N входов которого являются управляющими входами 7 устройства. Первые (N-) выходов регистра 3 соединены с входами первого дополнительного регист- ра 4.1, а N-й выход регистра 3-е входом управления коммутатора 1.1. Первый вход коммутатора 1.1 соединен с выходом дополнительного элемента 6.1 задержки, через элемент 2.1 задержки второй вход коммутатора 1.1 соединен с выходом дополнительного элемента 6.1 задержки (N-i-1) первых выходов каждого 4.-го дополнительного регистра соединены с вхо- дами 4.(i+l)-ro дополнительного регистра. (К-1)-й выход дополнительного регистра 4.i соединен с входом управления 1.(i+l)-ro коммутатора, тактовый вход дополнительного ре- гистра 4.1 соединен с выходом коммутатора 1.1 и входом дополнительного элемента 6.(i+l) задержки, выход которого соединен с первым и входом коммутатора l.{i+l) непосредственно и через элемент задержки 2.(i+l) - с его вторьм входом, где (N-1). Выход коммутатора 1.N соединен с выходом 9 устройства.

Устройство работает следуюш.им об- разом.

Задерживаемый импульс поступает с входа 8 на вход формиров&теля 5 импульсов , а соответствующий ему двоичный код задержки К j - на входы ре- гистра 3. Формирователь 5 импульсов по фронту входного импульса вырабатывает импульс с минимально возможной для применяемой элементной базы длительностью t . Этот импульс посту пает на тактовый вход регистра 3 и н вход дополнительного элемента 6.1 задержки.

При этом происходит запись кода задержки с управляющих входов 7 в регистр 3. Для правильной работы устройства необходимо, чтобы импульс на первый вход коммутатора 1.1 поступал не раньше, чем на управляющий вход коммутатора 1.1 поступит сигнал с выхода регистра 3, соответствующий старшему разряду кода задержки Kj. Следовательно, время задержки Tj, дополнительного элемента 6.1 задержки должно быть больше или равно времени установки Тур регистра 3. Коммутатор 1.1 в зависимости от уровня сигнала на управляющем входе пропускает на выход либо импульс с выхода дополнительного элемента 6.1 задержки, либо импульс с выхода элемента 2.1 задержки. Величина времени задержки элемента 2.1 задержки в соответствии с весом старшего разряда кода задержки Kj равна Т. /2, где Тз. максимальное время регулируемой задержки. Младшие разряды кода задержки Kj поступают на вход дополнительного регистра 4.1. Импульс с выхода коммутатора 1.1 поступает на тактовый вход дополнительного регистра 4.1 , на первый вход коммутатора 1.2 через дополнительный элемент 5.2 задержки, а также на второй вход коммутатора 1.2 через дополнительный элемент 6.2 задержки и элемент 2.2 задержки. Коммутатор 1.2 управляется сигналом с выхода дополнительного регистра 4.1, который соответствует второму по старшинству разряду кода задержки К . Таким образом, управляемая линия задержки представляет собой регулярную структуру, состощую из N последовательно включенных ячеек.

Импульс на выходе устройства задерживается относительно входного на

Т МТзд+ N1,4- Nj-T ,

где Tj. - время задержки коммутатора Тд - дискретность программного

управления (значение задержки младшего звена задержки)

Поскольку величины Тзд и Tj постояны.

Регулируемая задержки Т . 1 Минимальный период смены управляемого кода Тек (и соответственно перио импульсов, задерживаемых на разное время) не может быть в общем случае меньше максимального времени регулируемой задержки Тз.(члкс Иначе возможна ситуация , когда задерживаемый импульс догоняет предыдуший и дальнейшая задержка предыдущего импульса осуществляется в соответствии с ко- дом задержки Kj последующего импульс

Кроме того, ограничение на минимальный период смены кода Тс накла- дьшается из-за собственных задержек элементов. Смена кода в каждом из

регистров возможна только после того, как задний фронт задерживаемого импульса появляется на выходе соответствующего коммутатора 1.1-1,N. Максимальное время задержки имеет ячейка, управляемая старшим разрядом кода задержки К. Следовательно, она и определяет ограничение на минимальный период смены кода Т «к,.

При условии Тзд (что необходимо для достижения максимального быстродействия) получают

кривая 4, N 16 - кривая 5). Зависимости построены при условии при- менения ЭСЛ микросхем 1500 серии со следующими параметрами:

f 3 НС, Тз 2,5 НС, Ту 2,2 не

Из графиков видно, что быстродействие предлагаемого устройства вьщ1е быстродействия прототипа,особенно если максимальная задержка сравнима с собственными задержками элементов применяемой элементной базы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска максимального числа | 1985 |

|

SU1314334A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для отображения информации | 1985 |

|

SU1267470A1 |

| Микропрограммное управляющее устройство | 1987 |

|

SU1527634A1 |

| Устройство для обработки запросов | 1989 |

|

SU1688248A1 |

| Синтезатор частот | 1987 |

|

SU1417165A1 |

| Устройство доступа к общей памяти | 1990 |

|

SU1836686A3 |

| Устройство для реализации логических функций | 1990 |

|

SU1739376A1 |

| Коммутатор | 1985 |

|

SU1248048A1 |

Изобретение может быть использовано в фазовращателях, корректорах временного положения импульсов синтезаторов сигналов и измерительных комплексах. Цель изобретения - повышение быстродействия при управлении задержкой входных импульсов на частоте их следования - достигается за счет введения в состав устройства формирователя 5 импульсов, N-1 дополнительных регистров 4.1...4.N-1, N дополнительных элементов 6.1...6.N задержки. Кроме того, в состав устройства входят N коммутаторов 1.1...1.N, N элементов задержки 2.1...2.N, регистр 3. Введенные отличия позволяют получить минимальный период смены кодов управления задержкой входных импульсов равным максимальному программируемому времени задержки. При этом значение этого периода не зависит от выбранной дискретности программного управления задержкой входных импульсов. 2 ил.

.j2 4 Т, + Т,

где Т„ равно максимальному из значений Тур и i.

Из приведенного выражения видно, что для достижения периода смены кода управления, равного максимальному времени управляемой задержки,необходимо выполнить условие Т, ,/2(Т: + + Т,) . Таким образом, предлагаемое устройство может работать с периодом смены кода Тех, равным максималь ному времени регулируемой задержки Т. Кроме того, период смены кода не зависит от числа разрядов N кода управления.

В устройстве-прототипе минимальны период смены кода определяется временем между поступлением импульса на вход и появлением его заднего фронта на выходе. Поэтому в устройстве- прототипе нельзя обеспечить режим работы, при котором период смены кода (а следовательно, и период следования импульсов, каждый из которых необходимо .задержать на свое определенное время) равен максималь- ному программируемому времени задержки.Более того,с увеличением числа разрядов N кода задержки Kj минимальный период смены кода увеличивается и быстродействие устройства снижа- ется. Предлагаемое устройство не имеет указанных недостатков.

На фиг. 2 представлены графики зависимости максимальной частоты сме кода управления fo 1/Тск от времени максимальной регулируемой задержки Tj для предлагаемого устройства (кривая 1) и для устрой- ства-прототипа при различном числе разрядов N кода управления (N ,А- коивая 2, N 8 - кривая 3, N 12 15 Формула изобретения

Линия задержки, содержащая N коммутаторов, N элементов задержки, N входов которого соединены с управляющими входами устройства, а N-Й выход - с управляющим входом первого коммутатора, отличающаяся тем, что, с целью повьше ния быстродействия при управлении задержкой входных импульсов на частоте их следования, в нее дополнительно введены формирователь импульсов,N дополнительных элементов задержки, N-1 дополнительных регисров, N-i-l первых выходов каждог 1-го из которых соединены с входами (i+l)-ro дополнительного регистра, а ()-й выход i-ro дополнительного регистра соединен с входом управления (i+l)-ro коммутатора, тактовый вход i-го дополнительного регистра соединен с выходом i-ro коммутатора и входом (+1)-го дополнительного элемента задержки, выход которого соединен с первым входом (i+l)-ro коммутатора непосредственно и через (1+1)-й элемент задержки - с его вторым входом, где i 1 ...,N-1, при этом вход линии соединен с входом формирователя импульсов, выход которого соединен с тактовым входом регистра, N-1 первых выходов которого соединены с входами первого дополнительного регистра и входом первого дополнительного элемента задержки,выход которого соединен с первым входом первого коммутатора непосредственно и через первый элемент задержки - с его вторым входом, выход N-ro коммутатора соединен с выходом линии.

icH.

50

SO

фиг.2

Составитель A. Очеретяный Редактор Л. Пчолинская Техред Л.Сердюкова Корректор Э.Лончакова

Заказ 7759/55

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Фи9.1

, MC

WO

Подписное

| СПОСОБ РЕЗЕКЦИИ ЖЕЛУДКА | 1995 |

|

RU2122358C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Важеиина З.П., Волкова Н.Н., Чадович И.И | |||

| Методы и схемы временной задержки импульсных сигналов.-.: Сов.радио, 1971 | |||

| Ускоритель для воздушных тормозов при экстренном торможении | 1921 |

|

SU190A1 |

Авторы

Даты

1989-12-15—Публикация

1988-04-14—Подача